CPU+MIC mixed heterogeneous cluster system for achieving large-scale computing

A cluster system and heterogeneous cluster technology, which is applied in the field of high-performance computing to improve system performance, achieve computing scale, and meet high-performance applications.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

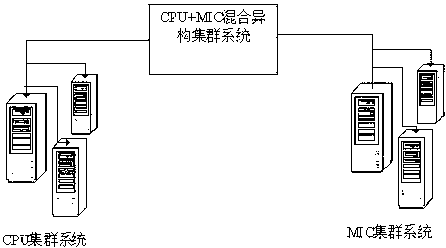

[0033] The present invention is a CPU+MIC hybrid heterogeneous cluster system that realizes large-scale computing, as shown in the figure 1 As shown, the system includes:

[0034] A pure central processing unit (CPU) cluster system, said system only uses CPU chips for computing;

[0035] A MIC cluster system, each node in the cluster system adopts CPU+MIC heterogeneous architecture, in addition to the CPU chip, the node also contains at least one integrated many-core (MIC) card;

[0036] The connector is used to connect the MIC card in each node in the MIC cluster system to the CPU chip.

[0037] Specifically, the connector is a PCIE slot.

[0038] A high-speed network is used to connect each node in the mixed heterogeneous cluster, and each node can realize high-speed communication with each other.

[0039] MIC is a many-core chip developed by Intel Corporation for high-performance parallel computing. It is developed from the existing Xeon processor products, and it is a ...

Embodiment 2

[0055] To achieve high efficiency, this system must be designed with integrated software and hardware, so that the application software can run on this system with the highest efficiency.

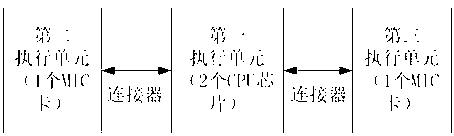

[0056] In view of this, a CPU+MIC hybrid heterogeneous cluster system that realizes large-scale computing in the present invention can also be described from the following perspectives, as figure 2 As shown, the system includes:

[0057] The first execution system uses a CPU cluster for computing, and the processor of each computing node is implemented by two CPU chips for executing information processing;

[0058] The second execution system uses MIC clusters for computing. The processor of each computing node is realized by 2 CPU chips and 2 MIC cards. Each computing node is divided into three execution units:

[0059] The first execution unit, the processor of which is implemented by two CPU chips, is used to perform information processing;

[0060] The second and third execution unit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More