Power semiconductor chip and manufacturing method thereof

A technology of power semiconductors and chips, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as uneven current between cells, uneven current, and switching speed differences, and achieve improved current sharing characteristics, improving the habit of current sharing, and improving the effect of switching control ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

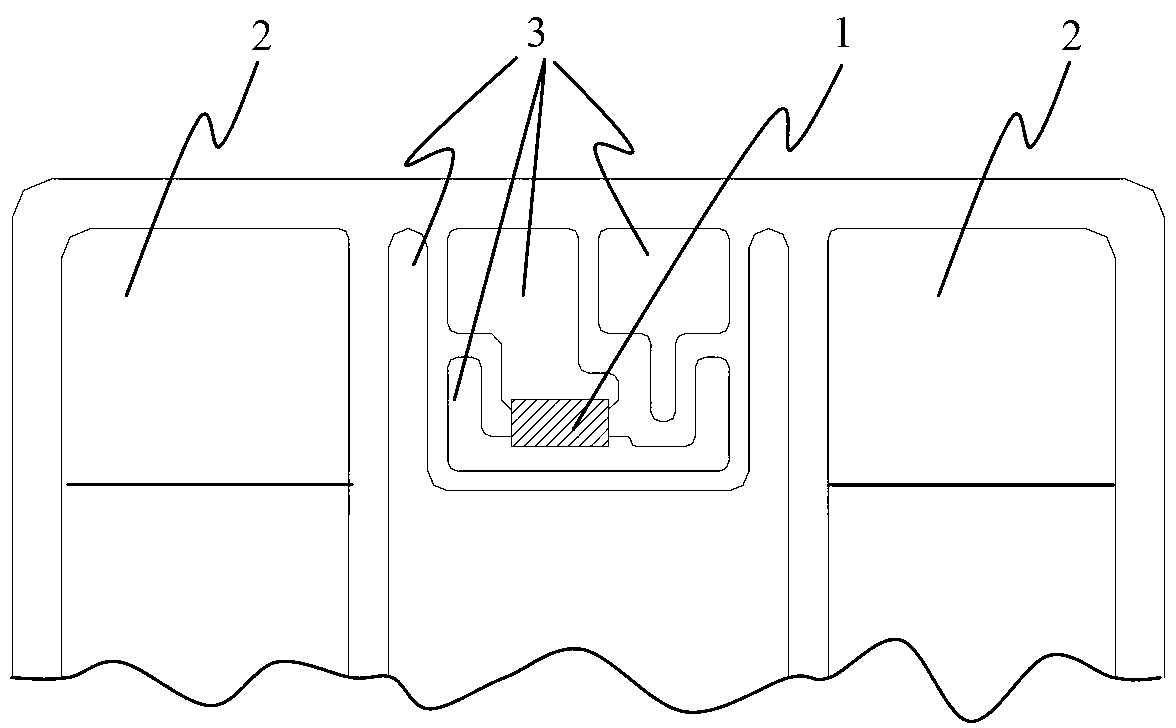

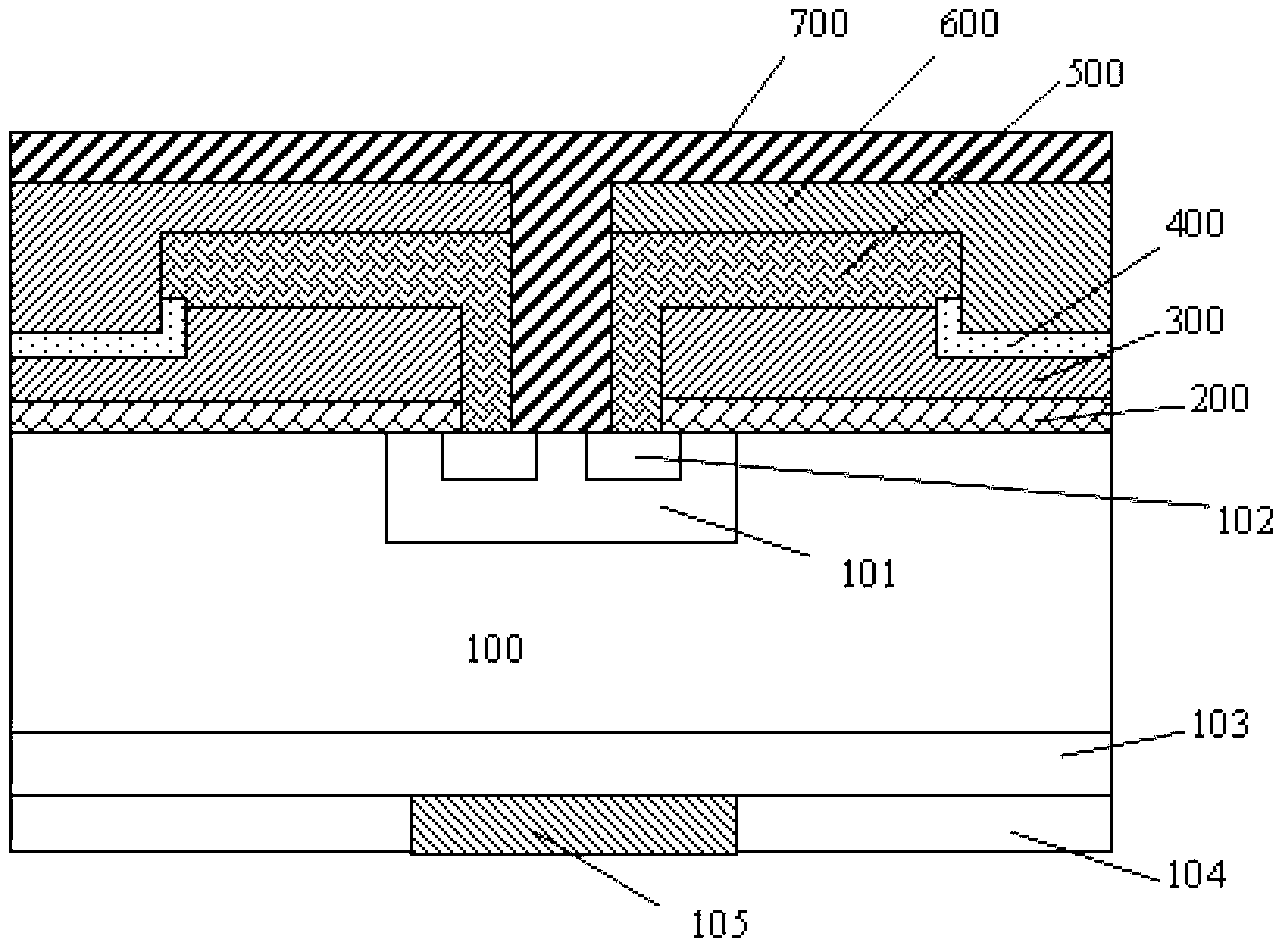

[0056] combine figure 2 The structure of the cell unit of the power semiconductor chip provided by the embodiment of the present invention will be described in detail. figure 2 It is a schematic cross-sectional structure diagram of a cell unit of a power semiconductor chip provided by an embodiment of the present invention.

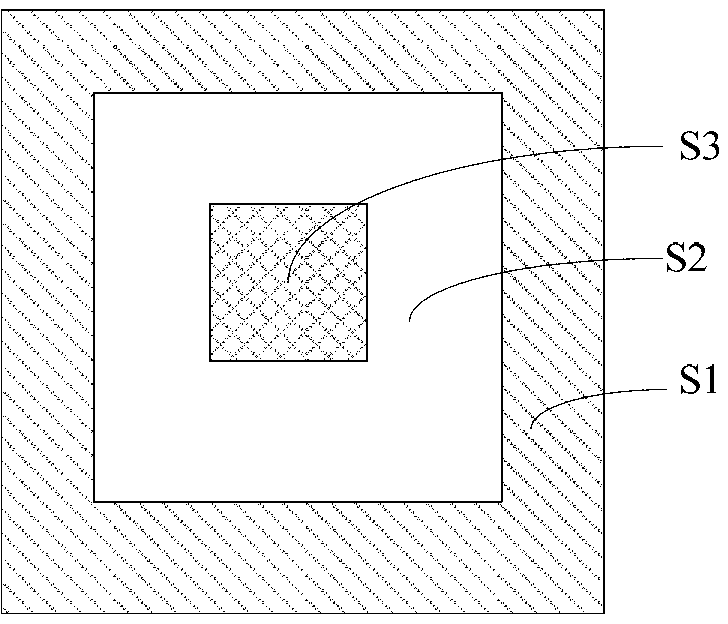

[0057] Such as figure 2 As shown, a cell unit of the power semiconductor chip includes a substrate 100 provided with a semiconductor structure; the front side of the substrate 100 includes a first sub-surface S1, a second sub-surface S2 and a third sub-surface S3, wherein the third The sub-surface S3 is the area where the center of the front surface is located, the second sub-surface S2 surrounds the third sub-surface, the first sub-surface S1 is located at the outermost periphery of the cell unit, and the first sub-surface S1 surrounds the second sub-surface S2 and the second sub-surface S2. The three sub-surfaces S3, the specific positional relatio...

Embodiment 2

[0087] combine Figure 5 6 (9) to describe the preparation method of the power semiconductor chip. Such as Figure 5 As shown, the preparation method of the power semiconductor chip comprises the following steps,

[0088] S51. Provide a substrate provided with a semiconductor structure:

[0089] Such as image 3 as shown, image 3 is the front top view of the substrate. The substrate front side has a first subsurface, a second subsurface, and a third subsurface. The positional relationship of the first sub-surface, the first sub-surface, the second sub-surface and the third sub-surface is the same as that of the sub-surfaces on the substrate described in the first embodiment above. For the sake of brevity, no detailed description is given here, please refer to the corresponding part of Embodiment 1.

[0090] As shown in FIG. 6(1), a semiconductor structure corresponding to the power semiconductor chip is disposed inside the substrate. The semiconductor structure includ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More