Method and system for reducing power consumption of multi-thread program

A multi-thread and program technology, applied in the field of reducing power consumption of multi-thread programs, can solve problems such as transition time and power loss

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment )

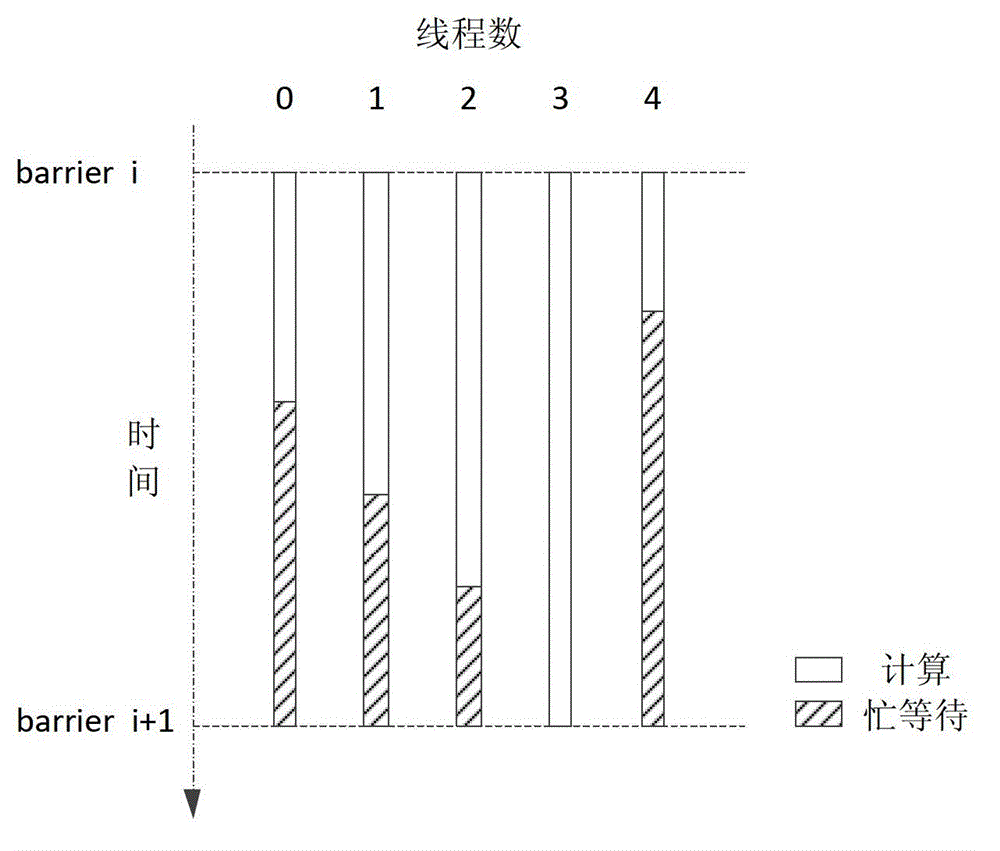

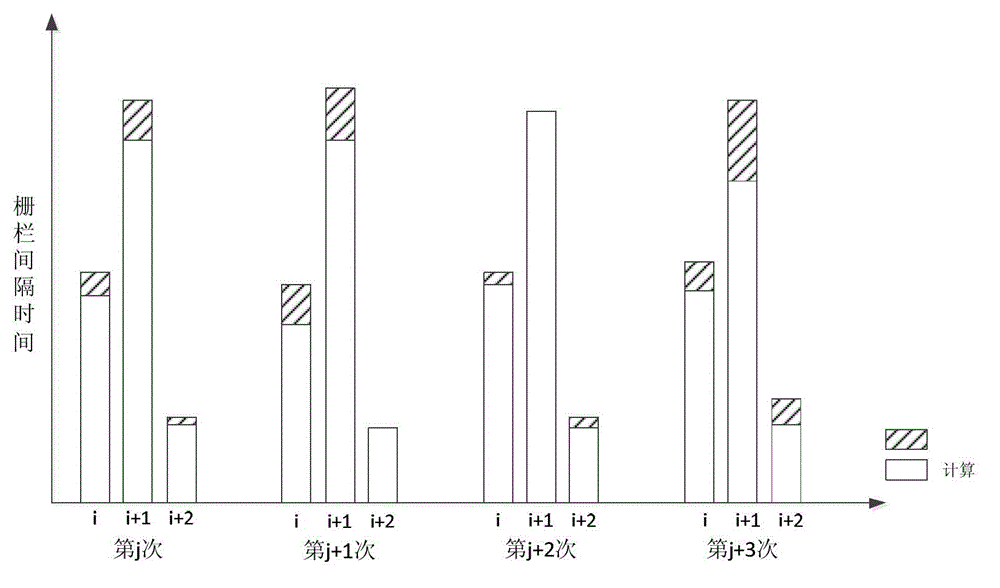

[0037] When the thread reaches the i-th fence again, the thread that reaches the fence synchronization point first uses the interval time read from the fence interval time prediction table to subtract the calculation time, predicts the busy waiting time of the thread, and chooses to enter the appropriate low power consumption mode.

[0038] In an embodiment, the fence interval time is 10000us+1500us, minus the calculation time of 8000us, the predicted busy waiting time is 3500us.

[0039] fence address

fence interval

0x2002e530

10000us+1500us

0x2002e536

17000us+3000us

[0040] When the prediction interval time of the fence is about to come, the thread that has reached the synchronization point of the fence earlier is restored to the normal power consumption mode, and the fence interval time prediction table is updated.

[0041] The update fence interval is 8000us+3200us.

[0042] fence address

fence ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More