A power semiconductor chip gate region

A technology of power semiconductors and gate regions, which is applied in semiconductor devices, electrical components, circuits, etc., can solve the problems of uneven switching speed, uneven current, and large signal differences between chips, so as to improve the uniformity of switching speed, The effect of reducing error sensitivity

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The present invention will be described in detail below in conjunction with specific embodiments shown in the accompanying drawings. However, these embodiments do not limit the present invention, and any structural, method or functional changes made by those skilled in the art according to these embodiments are included in the protection scope of the present invention.

[0025] Furthermore, repeated reference numerals or designations may be used in different embodiments. These repetitions are only for the purpose of simply and clearly describing the present invention, and do not represent any relationship between the different embodiments and / or structures discussed.

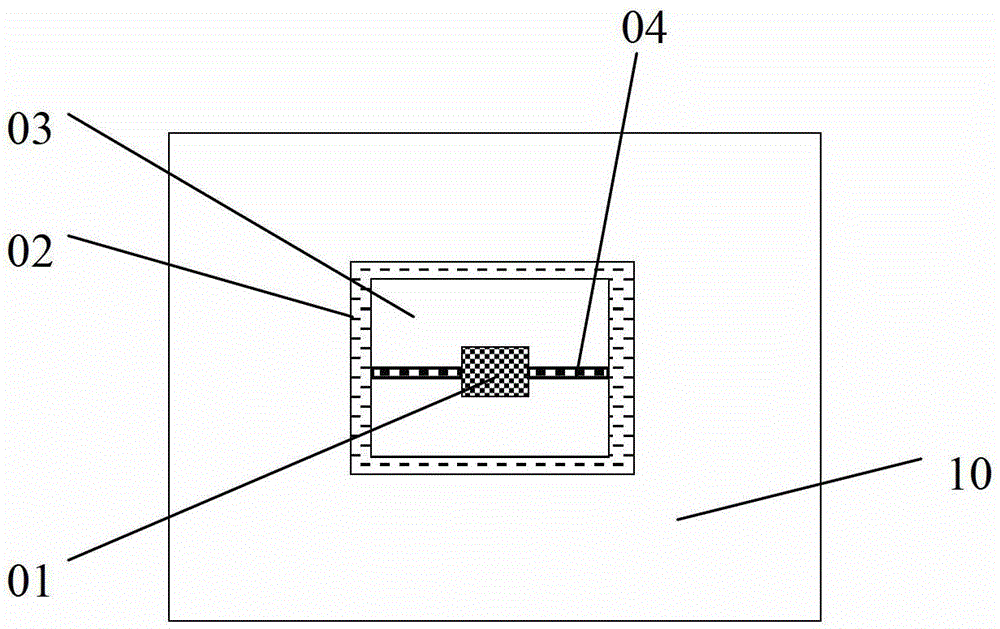

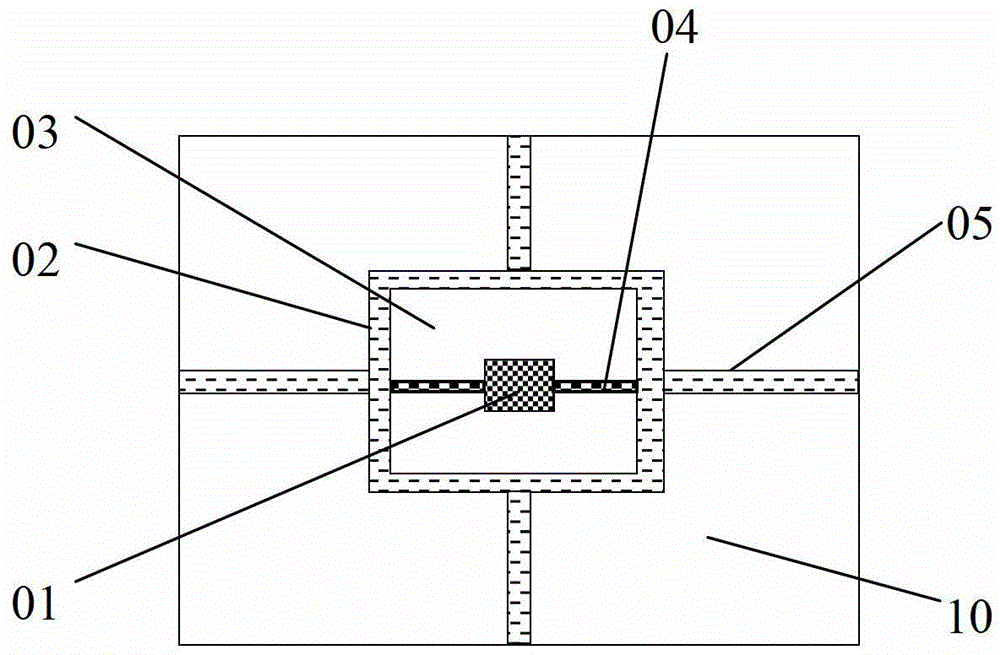

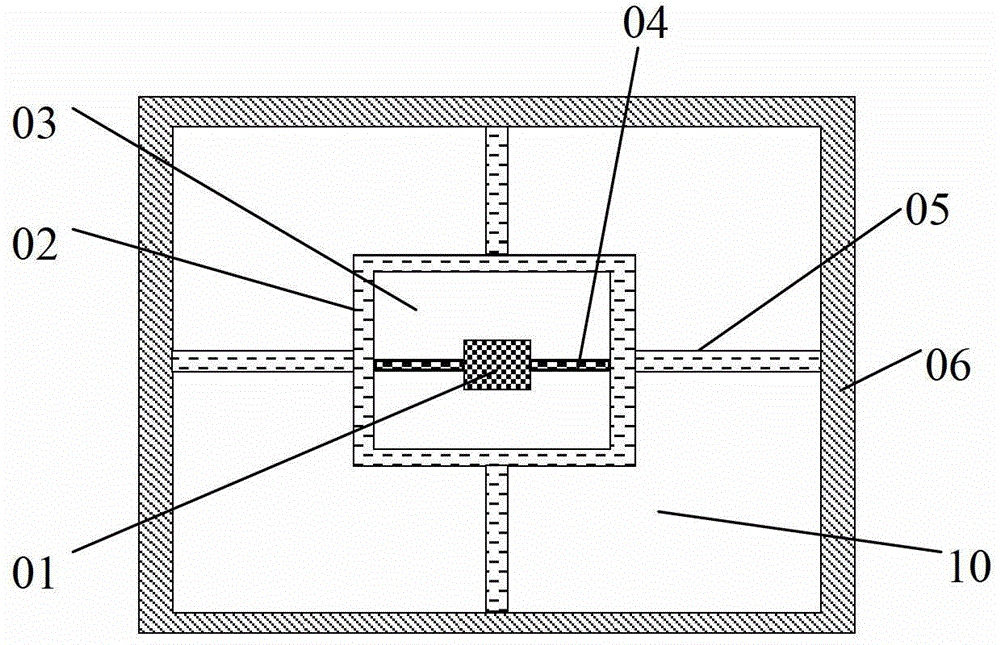

[0026] see figure 1 The gate area structure of the power semiconductor chip provided by the embodiment of the present invention includes a main gate area 01 located near the center of the chip cell area 10, a first gate bar 02 surrounding the main gate area 01, and a main gate area located in the main g...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More