Method and device for protecting chip top-layer covering integrity

A technology of integrity protection and chips, applied in the direction of internal/peripheral computer component protection, etc., can solve the problems of low security, simple detection mechanism, high power consumption, etc., and achieve the effect of solving low security

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

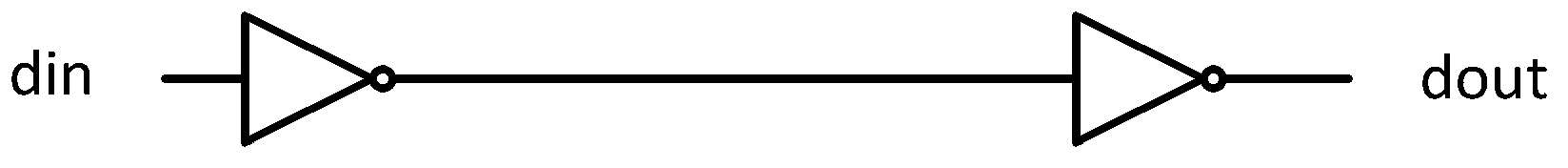

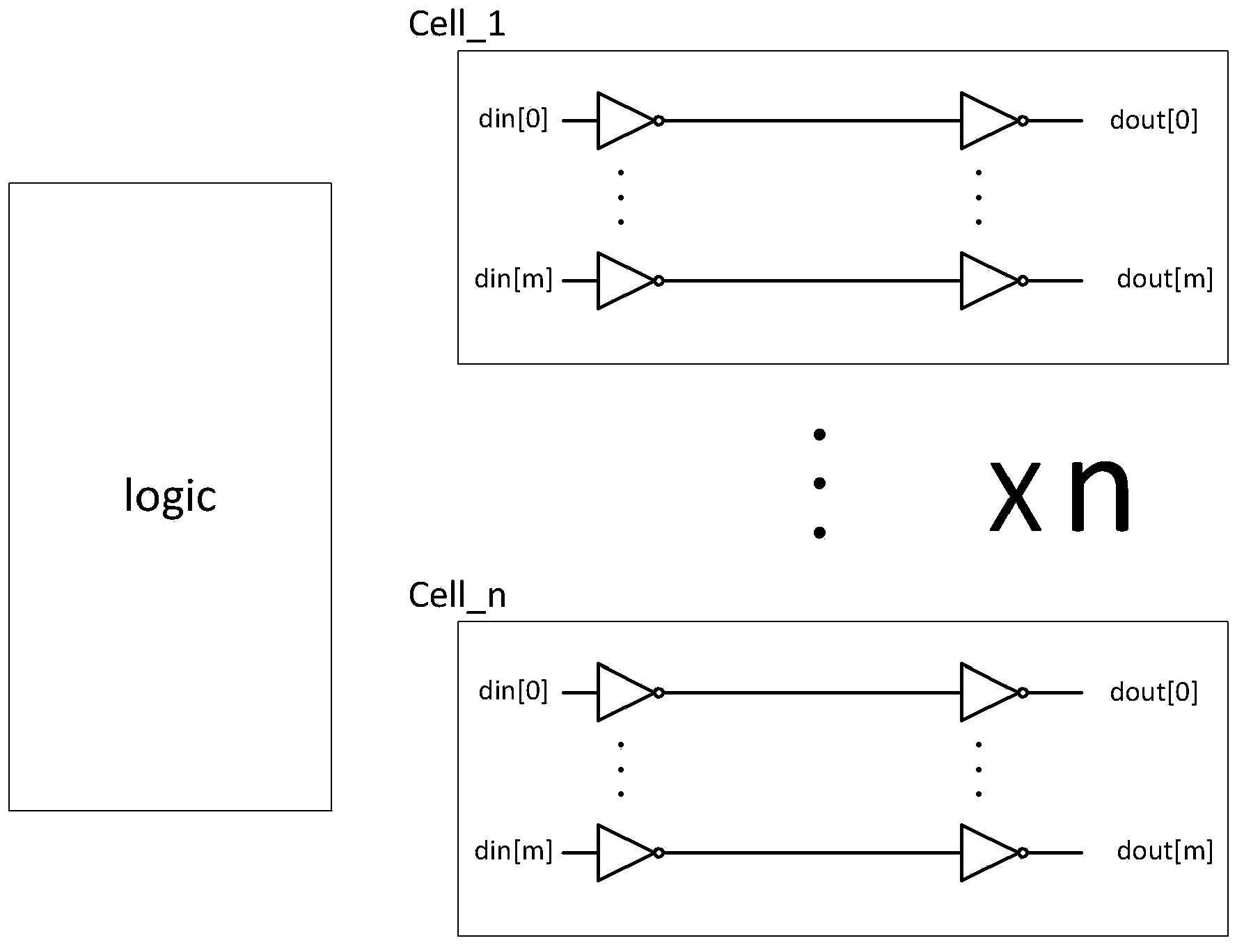

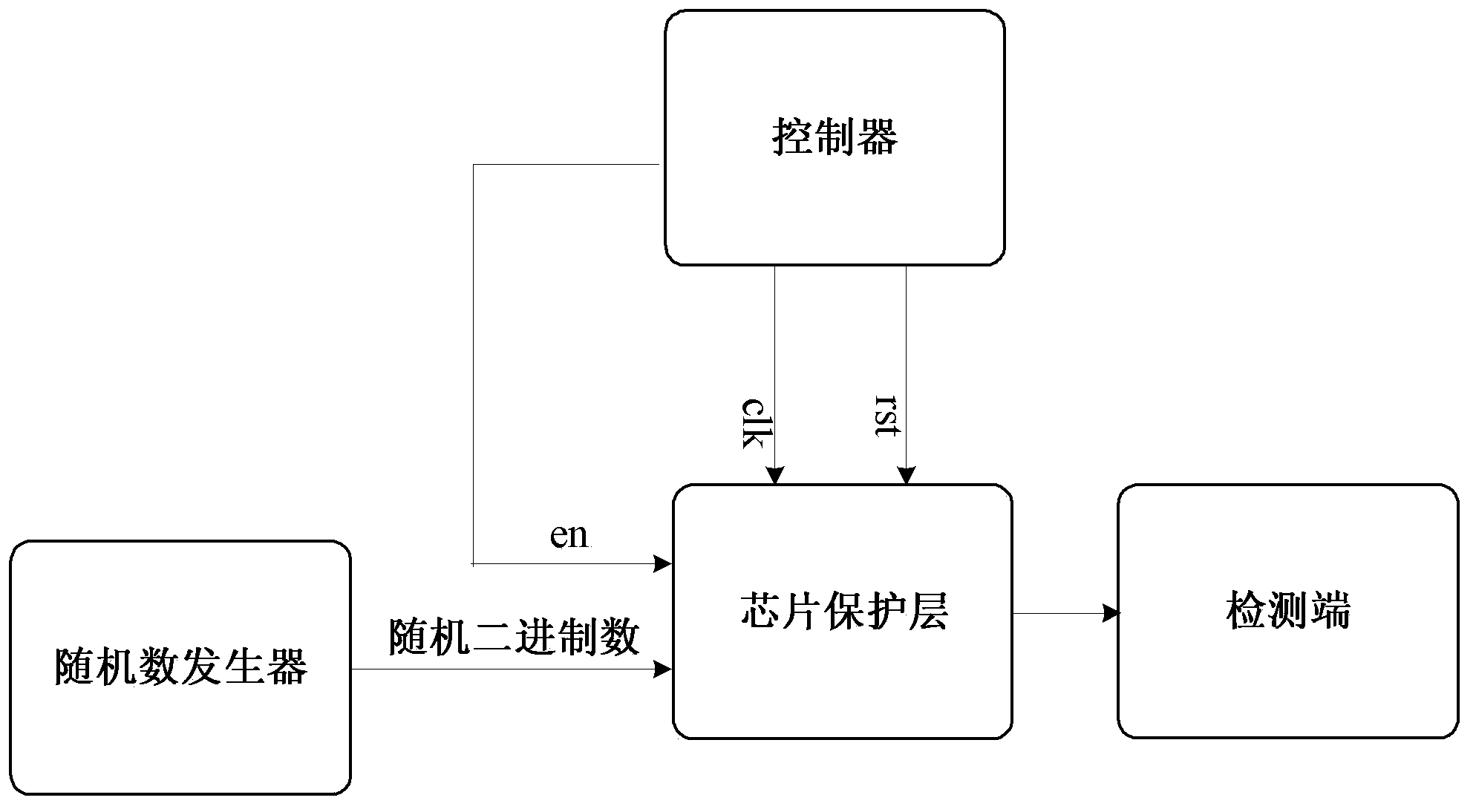

[0096] In the embodiment of the present invention, the top layer metal is divided into n groups, and each group has 8 metal lines, that is, M=8. After the system is reset, the initial value of each group of metal lines ([7:0]) is all "0". When the work enable signal is valid (en="1"), the circuit enters the work mode, and starts to detect whether the metal on the top layer of the entire chip is abnormal, and supports cycle detection.

[0097] The top metal wire covers the entire chip. When the chip is attacked by the top layer "stripping", whether only one or more metal wires on the top layer are cut, or the entire top layer is cut, an abnormal alarm interrupt can be generated. Figure 4 As shown, the second dashed line that is not connected represents a metal line that has been cut:

[0098] Detection order: check the first group, the second group of connections sequentially, and so on, and finally check the nth group.

[0099] When detecting a certain group, store the pre-...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More