Gearbox circuit for changing data bit width in high-speed transceiver and working method thereof

A gearbox circuit and data bit width technology, applied in the direction of asynchronous pulse counters, etc., can solve the problems of reducing system transmission efficiency and failing to meet system requirements

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

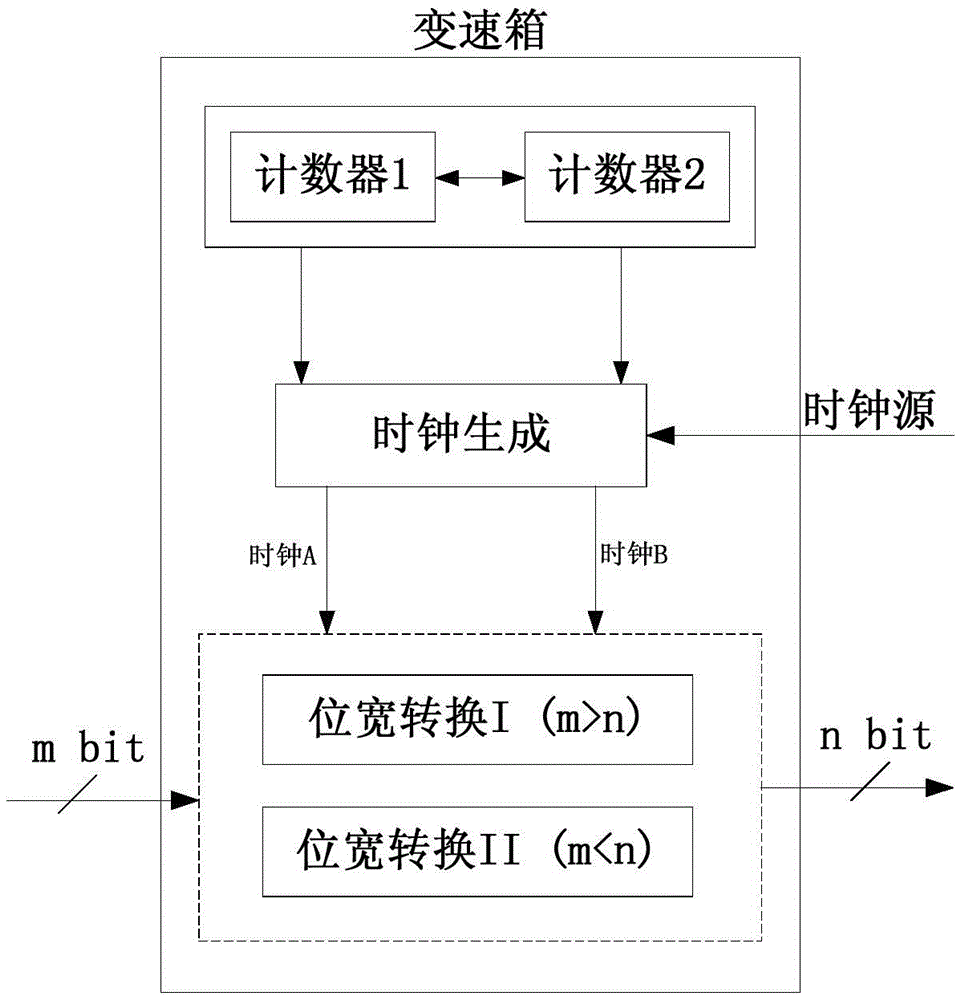

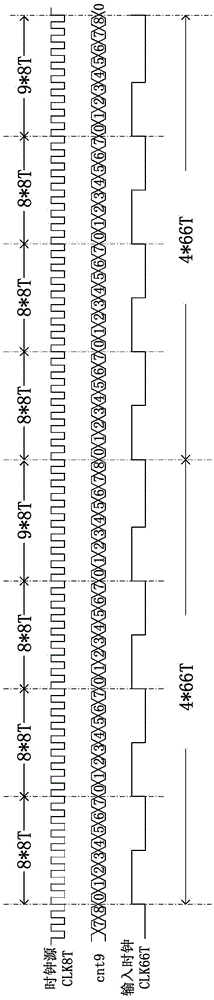

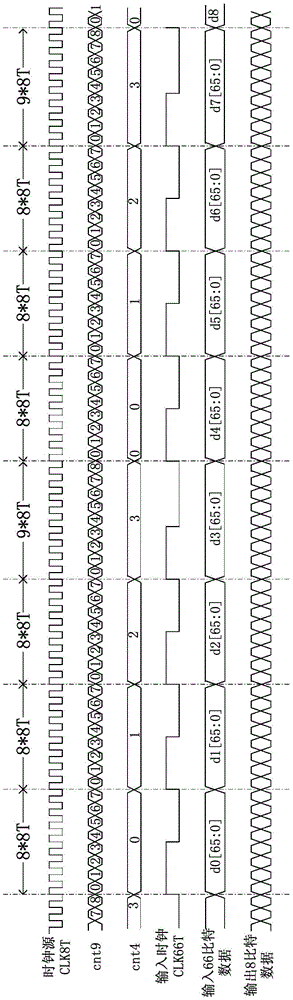

[0062] The present invention will be further described below in conjunction with the drawings and specific embodiments. In the present invention, according to the principle of stable bit rates at both ends of the gearbox, and according to the bit width relationship between input data and output data, a high-speed clock source is used to obtain two synchronous clocks to control the input and output of gearbox data. This method does not require any processing or control of the input data, and can perform continuous data transmission without changing the data bit width. It is possible to switch from more to less data bit width or from less to more under the condition of keeping input and output continuously without suspending input data. Gearbox circuit structure such as figure 1 As shown, it includes a counter generation circuit, a clock generation circuit, a first data width conversion circuit, and a second data width conversion circuit. The output of the counter generation ci...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More