Semiconductor device manufacturing method

A device manufacturing method and semiconductor technology, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as corrosion, stress layer loss, DSL integration failure, etc., and achieve the effect of process integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0028] Hereinafter, the present invention is described by means of specific embodiments shown in the drawings. It should be understood, however, that these descriptions are exemplary only and are not intended to limit the scope of the present invention. Also, in the following description, descriptions of well-known structures and techniques are omitted to avoid unnecessarily obscuring the concept of the present invention.

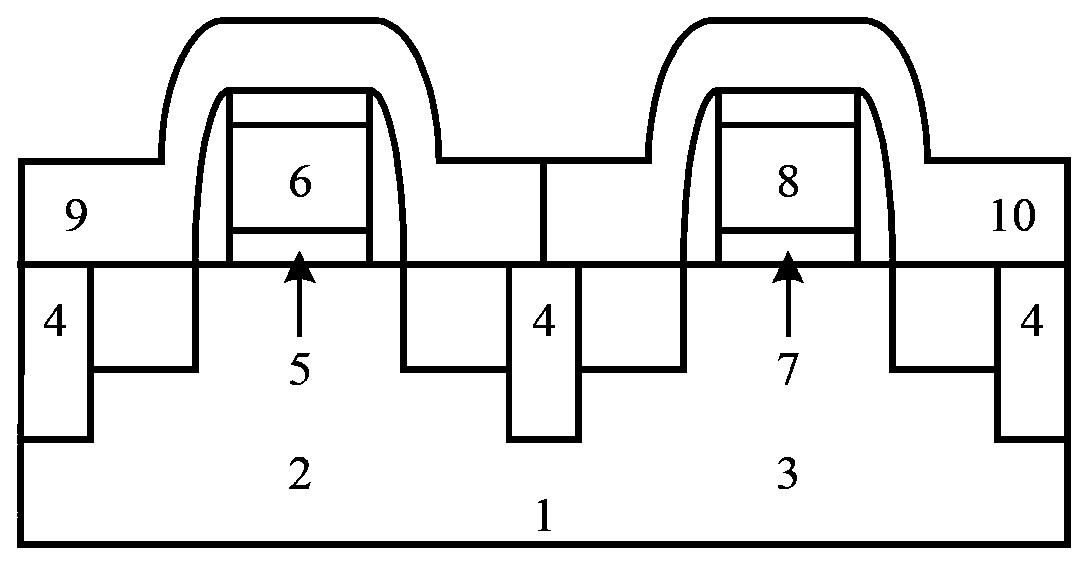

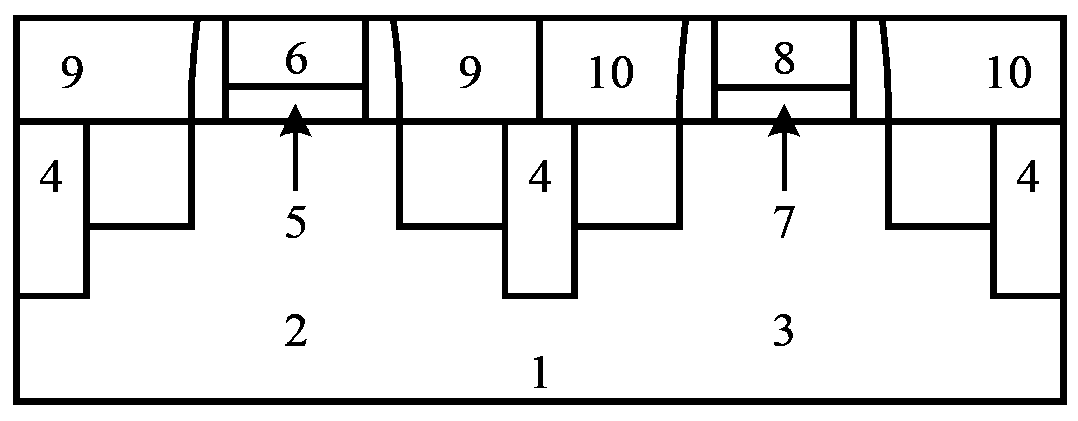

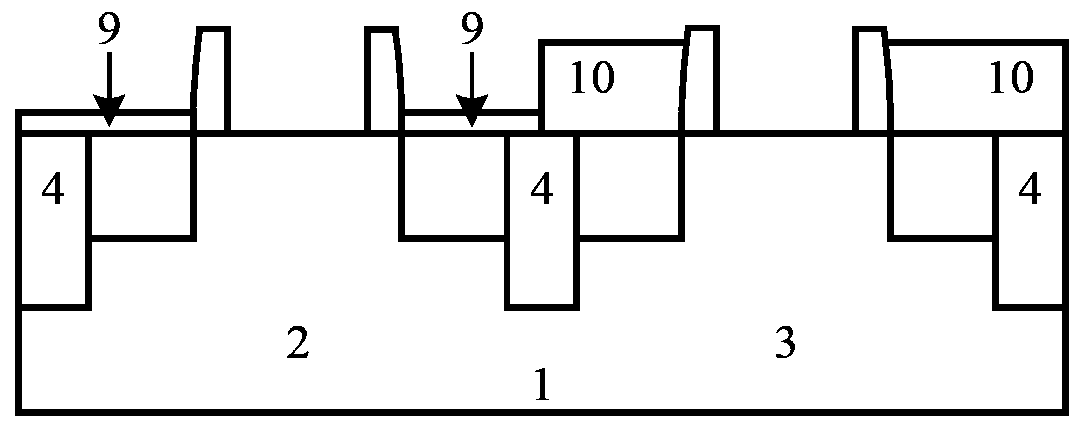

[0029] The present invention provides a method for manufacturing a semiconductor device, and in particular relates to a method for manufacturing a transistor using spacer technology. Please refer to the attached Figure 4-10 , the semiconductor device manufacturing method provided by the present invention will be described in detail.

[0030] First, see attached Figure 4 , on the semiconductor substrate 1 , NMOS 2 and PMOS 3 are formed, and different MOS transistors are isolated by STI structures 4 . Wherein, in this embodiment, a single crystal silicon...

PUM

| Property | Measurement | Unit |

|---|---|---|

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More