Method for measuring external parasitic resistance of MOS transistor

A MOS transistor and parasitic resistance technology, which is applied in the field of external parasitic resistance measurement, can solve problems such as complex methods, achieve simple methods and processes, improve measurement efficiency, and achieve uniform changes.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0030] At present, when measuring the external parasitic resistance of transistors, at least three transistors need to be formed on the semiconductor substrate. The formation process of the three transistors is the same, and the lengths of the channel regions are different, and then the gates of the three transistors are respectively applied to work. Voltage and source apply a small source voltage to make the three transistors work in the linear region, and then perform a straight line fitting according to the obtained three source-drain resistances of the three transistors and the corresponding channel region lengths to obtain the external For parasitic resistance, the inventors found that this measurement method is relatively complicated and has low efficiency.

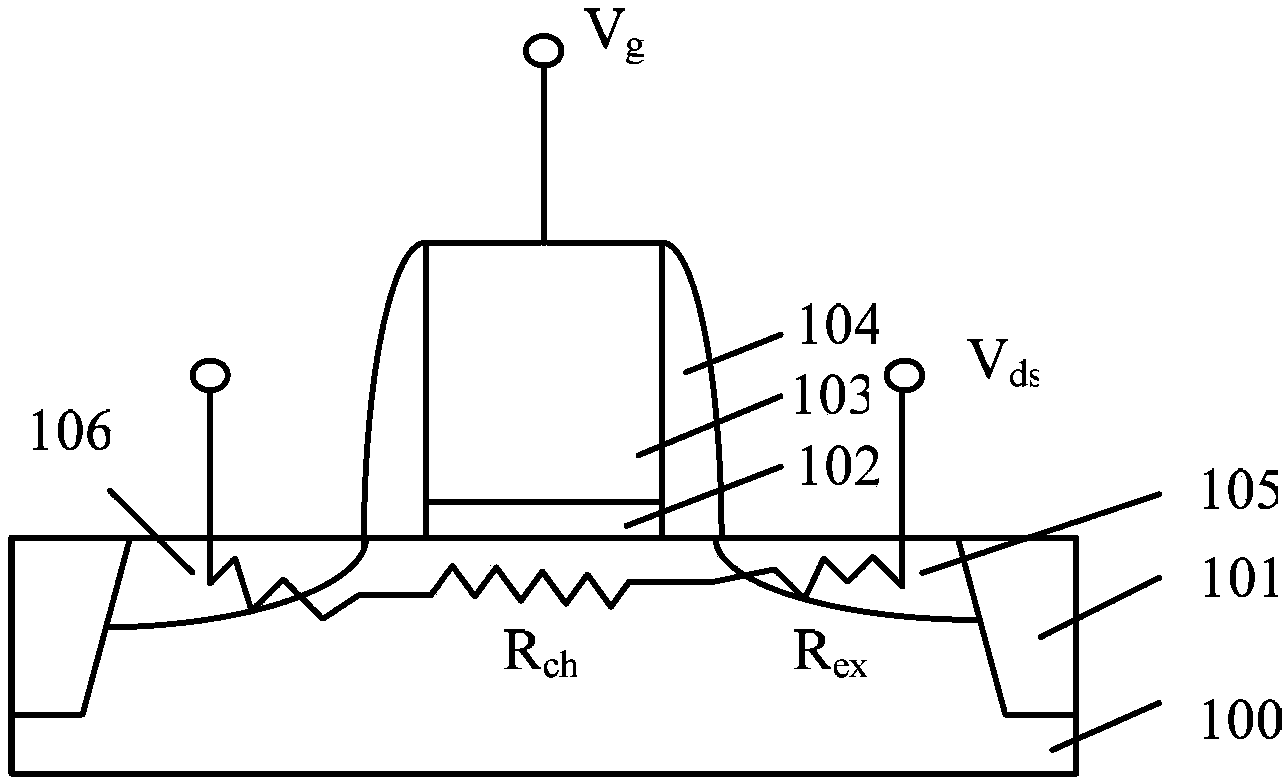

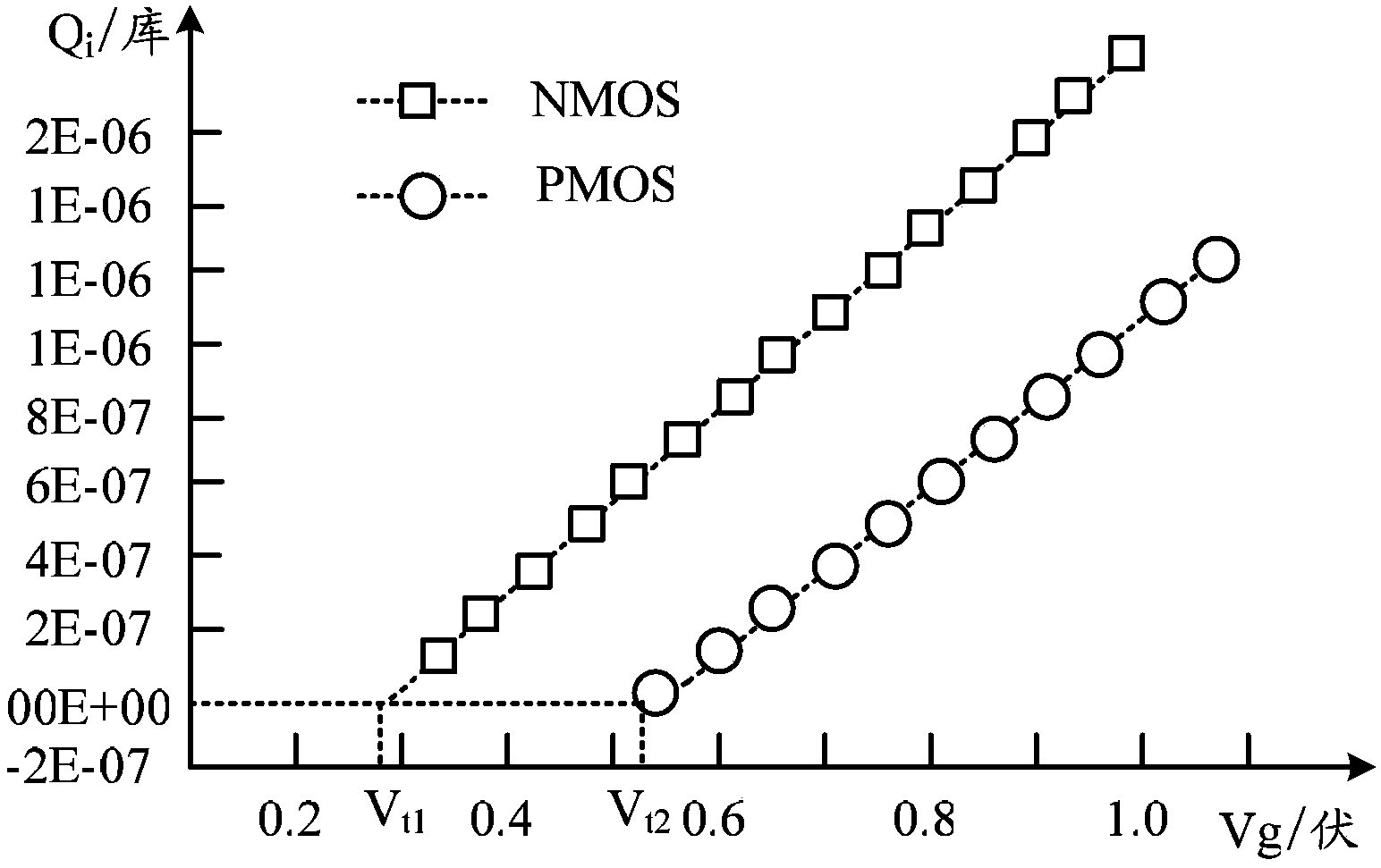

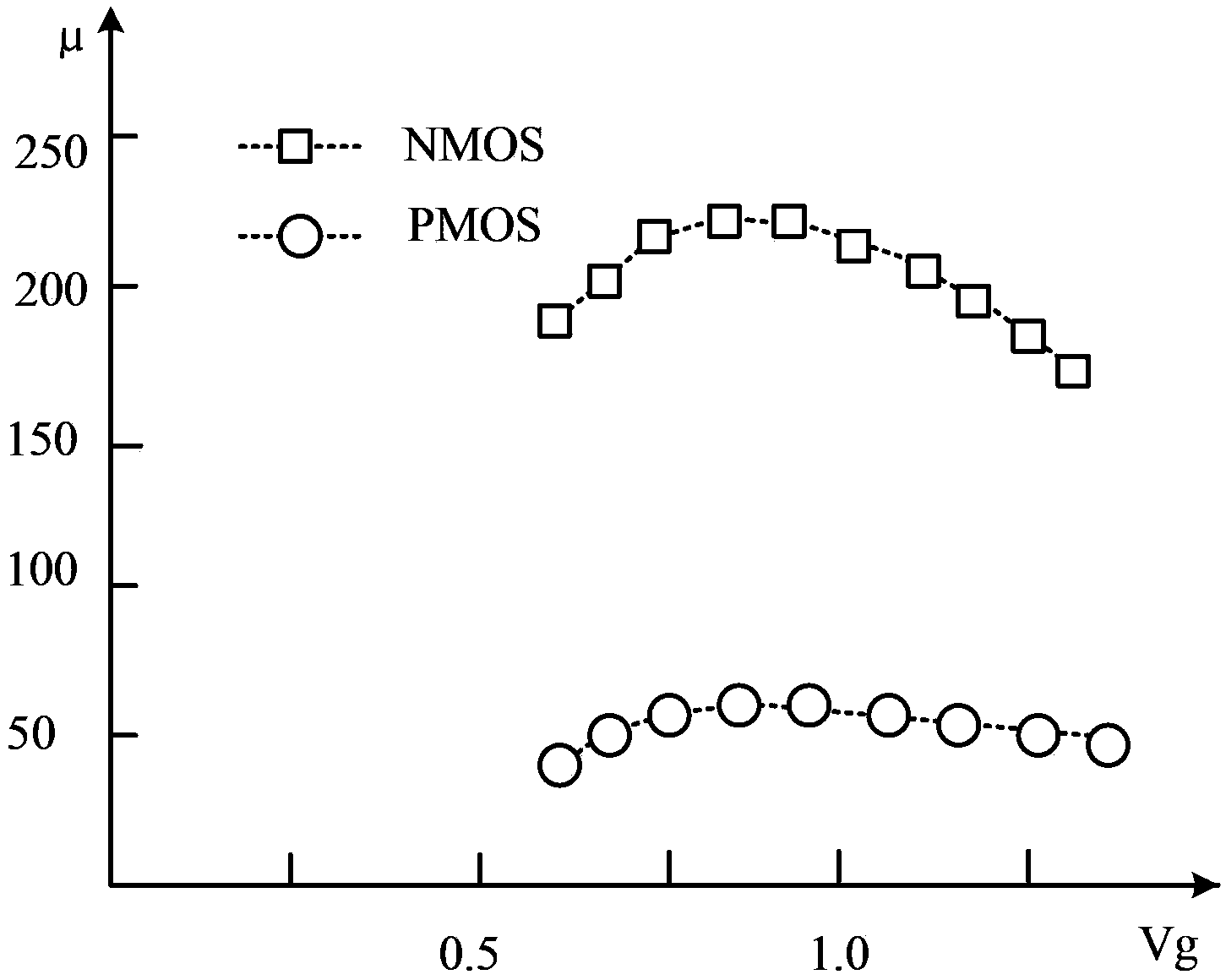

[0031] For this reason, the inventor proposes a method for measuring the external parasitic resistance of a MOS transistor, including: providing a semiconductor substrate, forming a MOS transistor on the semiconducto...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More