A fpga-based high-bandwidth ethernet ip core

An Ethernet, high-bandwidth technology, applied in the field of network communication, can solve the problem of low average communication rate and achieve the effect of complete architecture

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

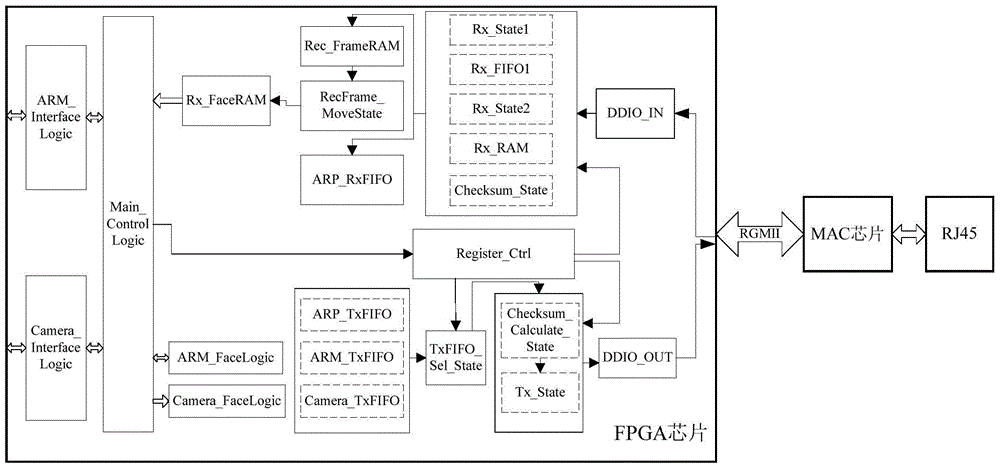

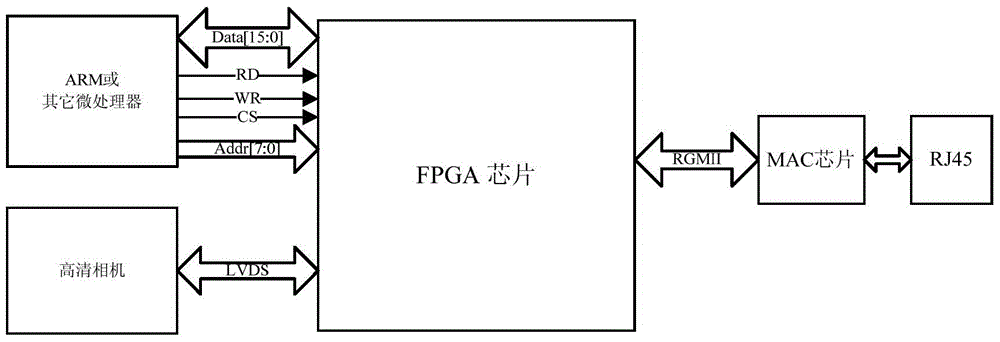

[0030] specific implementation plan

[0031] Ethernet IP core among the present invention is on the FPGA architecture system based on CycloneIII series, and the Ethernet PHY chip that circuit board adopts is 88E1111, adopts the RJ45 interface of HALO Company; The development board of CycloneIII series of Altera Company or meets following requirement The board can implement the system:

[0032] 1) Equipped with Gigabit Ethernet interface and PHY chip;

[0033] 2) With a custom IO interface;

[0034] 3) Onboard CycloneIII series FPGA chip.

[0035] After power supply, the FPGA uses the MDC / MDIO interface to configure the physical layer chip PHY. After the PHY chip completes the negotiation of transmission speed and related information, an effective and reliable connection is established.

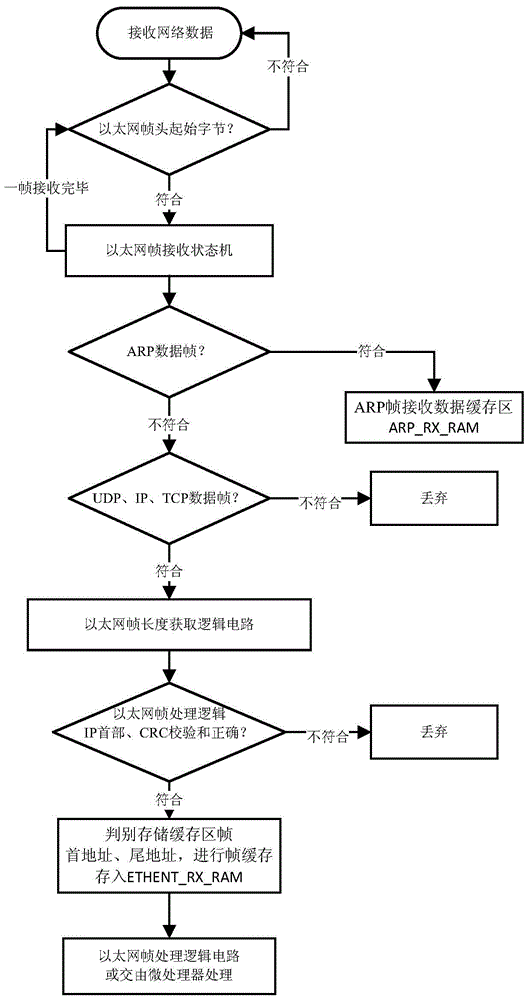

[0036] The Ethernet IP core receiving module among the present invention detects 8 initial bytes of the Ethernet frame header of the port in real time, after receiving the Ethernet frame he...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More