A delay sampling circuit with self-calibration function

A sampling circuit, delay circuit technology, applied in electrical components, electronic switches, pulse technology and other directions, can solve the problems of slow response time, phase deviation, stability and real-time performance of oscillation ring, to prevent measurement deviation, Improve the sampling accuracy, taking into account the effect of real-time and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

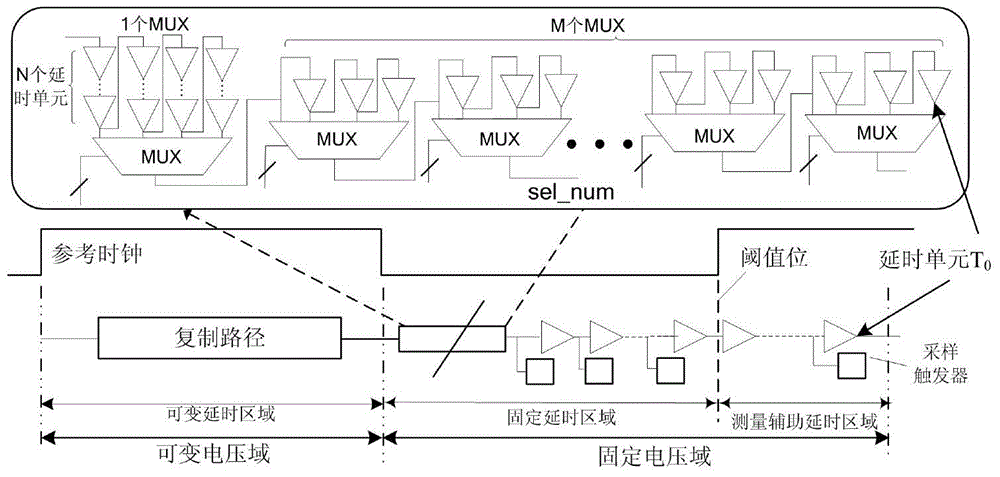

[0036] The technical solution of the present invention will be described in detail below with a specific design example under the CMOS 0.18 μm process.

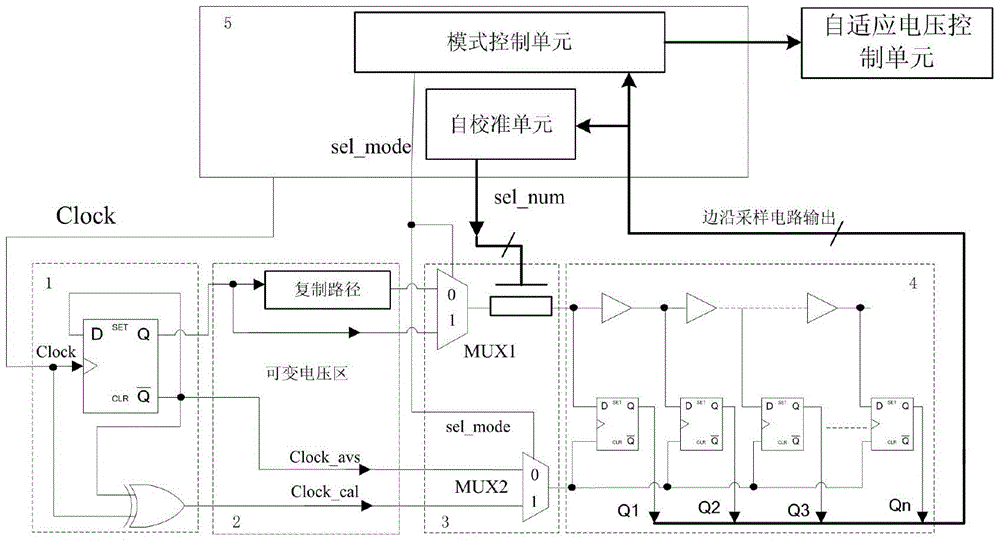

[0037] Such as figure 1 As shown, the delay sampling circuit with self-calibration function of the present invention includes a pulse generation circuit 1, a copy path unit 2, a calibration delay circuit 3, an edge sampling circuit 4 and a delay sampling control module 5, and the calibration delay The circuit 3 includes data selectors MUX1 and MUX2 to select one of the two.

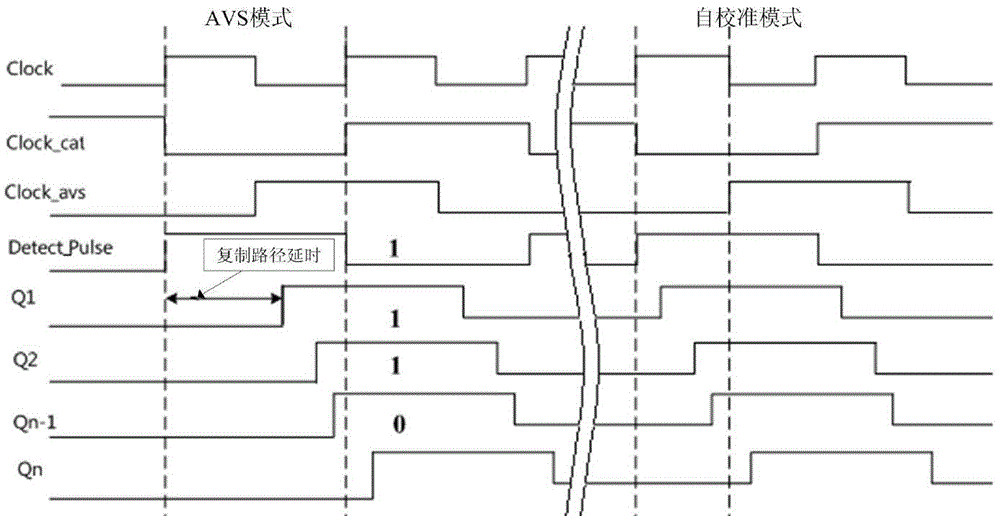

[0038] The pulse generation circuit 1 is composed of a flip-flop and an XOR logic unit. The Q non-output terminal of the flip-flop is connected to the D input terminal, and the output is the frequency division of the reference clock Clock, which is input to the copy path unit 2 as a pulse signal, and the Q non-output The terminal signal is used as the sampling clock Clock_avs in the adaptive adjustment mode, and the Q non-terminal signal is different fr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More