Multiplying unit

A technology of multipliers and adders, applied in the field of digital coding

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

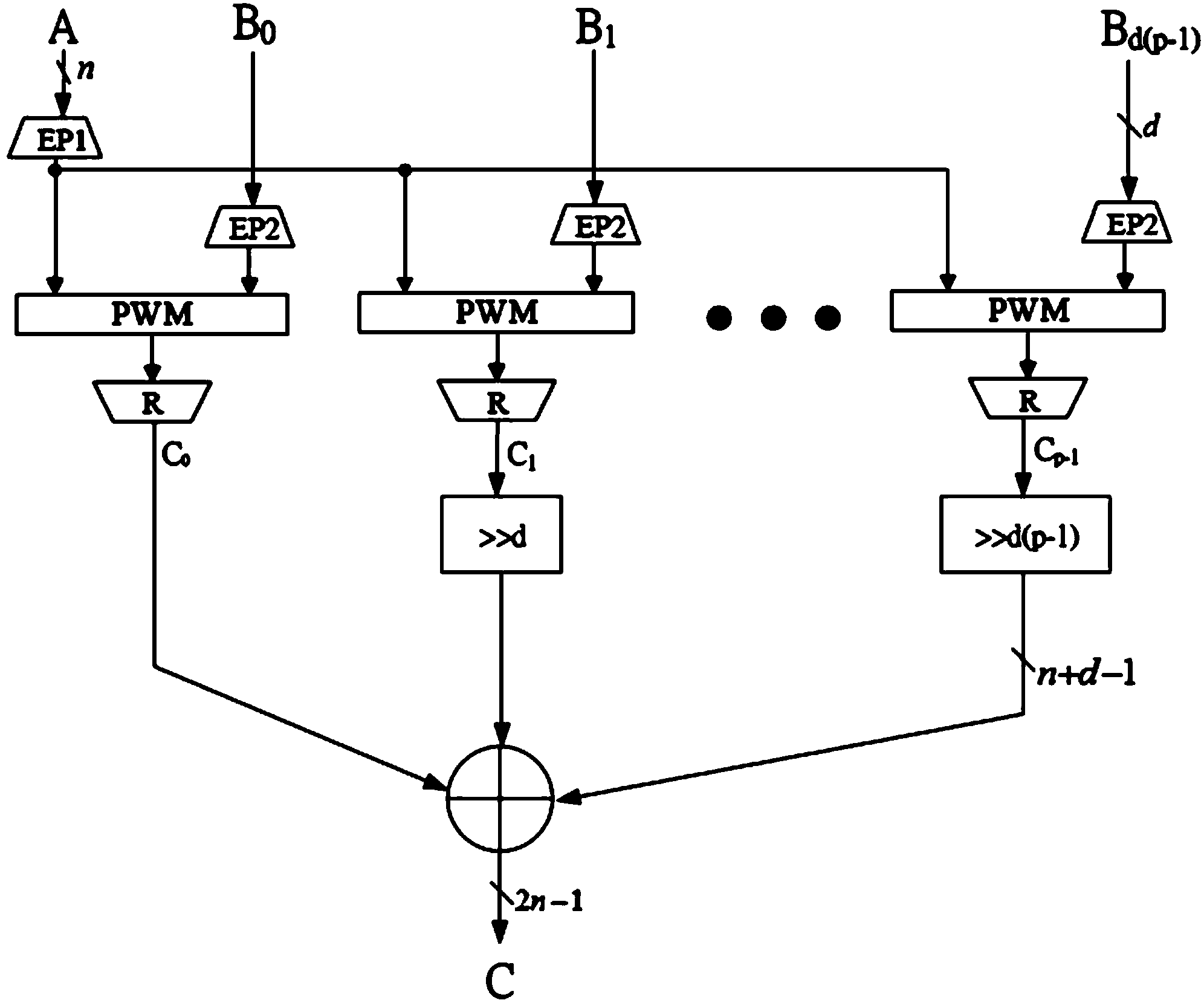

[0048] image 3 It shows a kind of digital parallel multiplier provided by the present invention, the digital parallel multiplier includes input terminal A, input terminal B 0 ...B P-2 B P-1 , the output terminal C and the calculation unit, the input terminal A and the input terminal B 0 ...B P-2 B P-1 Input calculation unit respectively, output from the output terminal C of described calculation unit after calculation processing, the calculation formula of described calculation unit output:

[0049] C=R(AB 0 +AB 1 x d +…+AB p-1 x d(p-1) )mod F(x), where R is a non-zero polynomial, x is a root of the irreducible polynomial F(x), d is the segmentation length, p is the segment number of segmentation, mod F(x) is the result obtained The reduction is the modulo operation.

[0050] The computing unit requires The clock cycle is used to complete the multiplication of A and B, where the interval of each clock cycle is T=T A +(1+3log b n)T X ,T A...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More