Method and circuit for integrating adaptive equalization parameter adjusting and transmission performance testing

A technology of adaptive equalization and transmission performance, applied in the direction of digital transmission system, transmission system, electrical components, etc., to achieve the effect of saving power consumption, reducing power consumption and reducing occupied area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

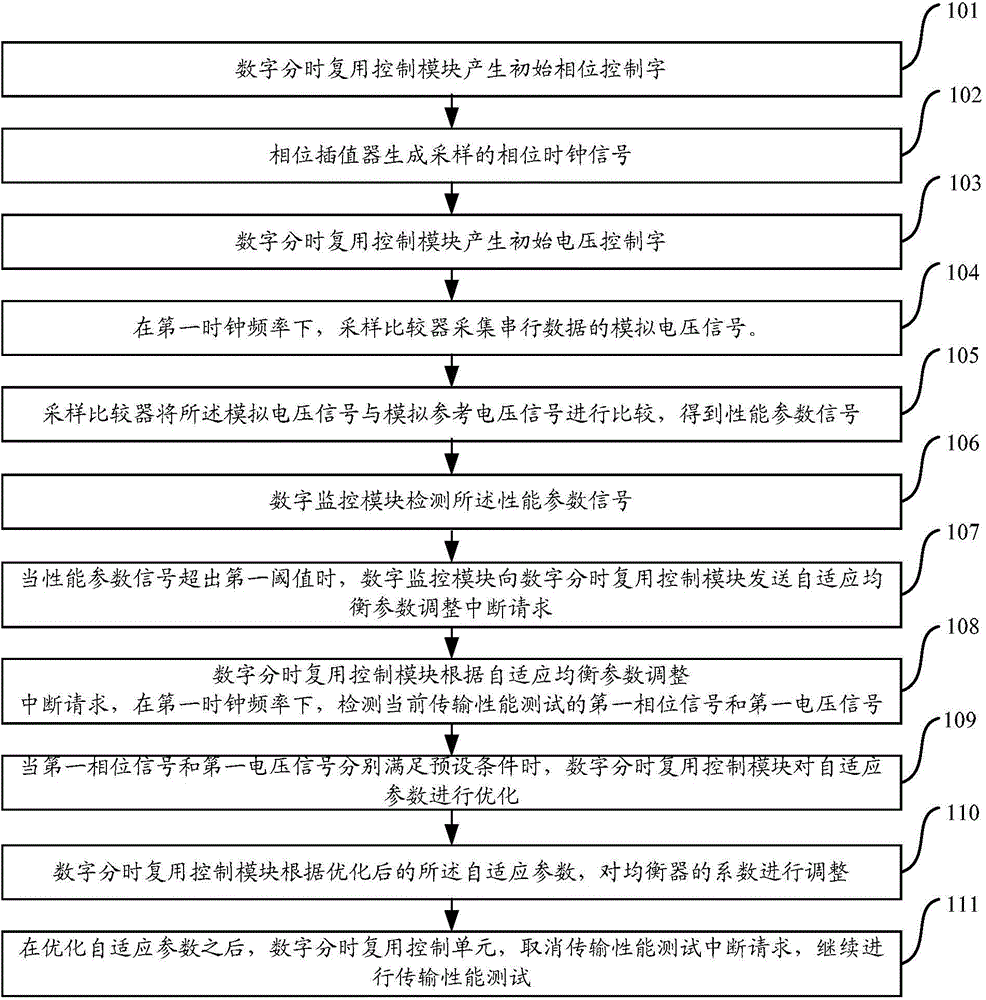

[0057] figure 1 It is a flow chart of an integrated method for adaptive equalization parameter adjustment and transmission performance test provided by Embodiment 1 of the present invention.

[0058] according to figure 1 As shown, the integrated method of adaptive equalization parameter adjustment and transmission performance test includes the following steps:

[0059] Step 101, the digital time-division multiplexing control module generates an initial phase control word.

[0060] Specifically, the initial phase control word is a phase control word that is pre-estimated and judged by the digital time-division multiplexing control module according to a preset accuracy or phase resolution; The number of phase points, the more phase points collected, the higher the accuracy and the higher the resolution.

[0061] Step 102, the phase interpolator generates a sampled phase clock signal according to the initial phase signal.

[0062] Specifically, according to the initial phase...

Embodiment 2

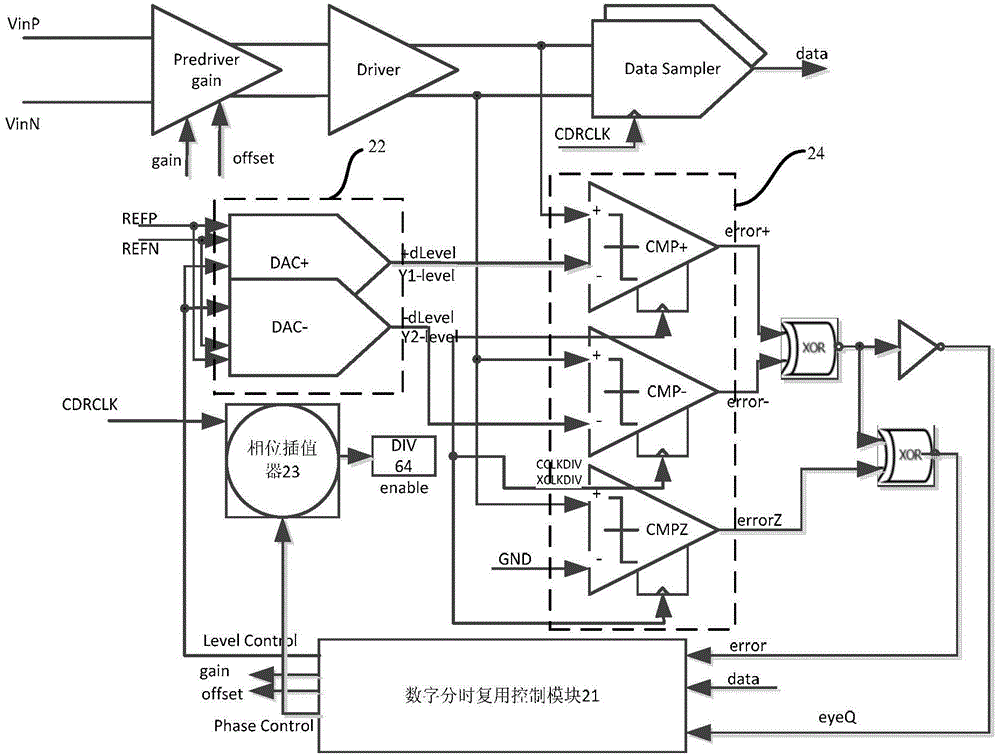

[0090] figure 2 A circuit integrating adaptive equalization parameter adjustment and transmission performance test provided by Embodiment 2 of the present invention. Such as figure 2 As shown, the circuit of the integrated adaptive equalization parameter adjustment and transmission performance test includes: digital time-division multiplexing control module 21, digital-to-analog converter 22, phase interpolator (Phase Interpolator) 23, sampling comparator 24 and digital monitoring module (not shown in the figure).

[0091] The sampling comparator 24 is configured to collect the analog voltage signal of the serial data at the first clock frequency.

[0092] The sampling comparator 24 is further configured to compare the analog voltage signal with an analog reference voltage signal to obtain a transmission performance parameter signal.

[0093] A digital monitoring module (not shown in the figure) is used to detect the transmission performance parameter signal; when the tra...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap