Transistors and methods of forming them

A technology of transistors and semiconductors, applied in the direction of semiconductor devices, semiconductor/solid-state device manufacturing, electrical components, etc., can solve the problems of unfavorable semiconductor device size reduction, large junction-free transistor size, chip integration, etc., to achieve short channel effect Effects of suppression, device density improvement, and integration improvement

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

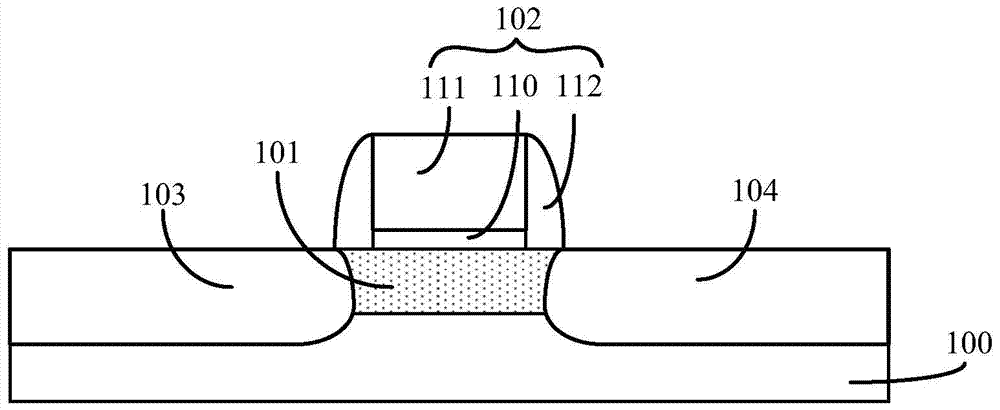

[0029] Such as figure 1 As shown, the existing junction-free transistors are planar transistors, so the size of the junction-free transistors is too large, which is not conducive to improving the integration of semiconductor devices.

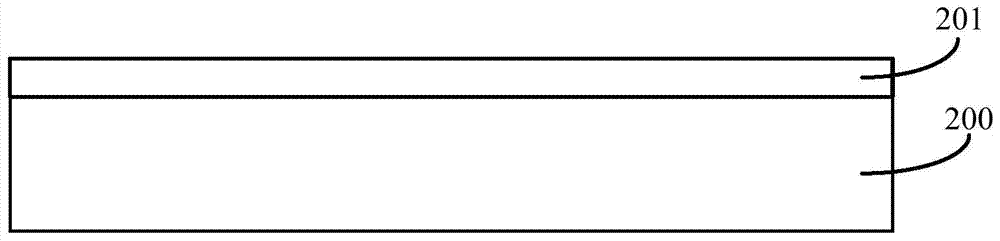

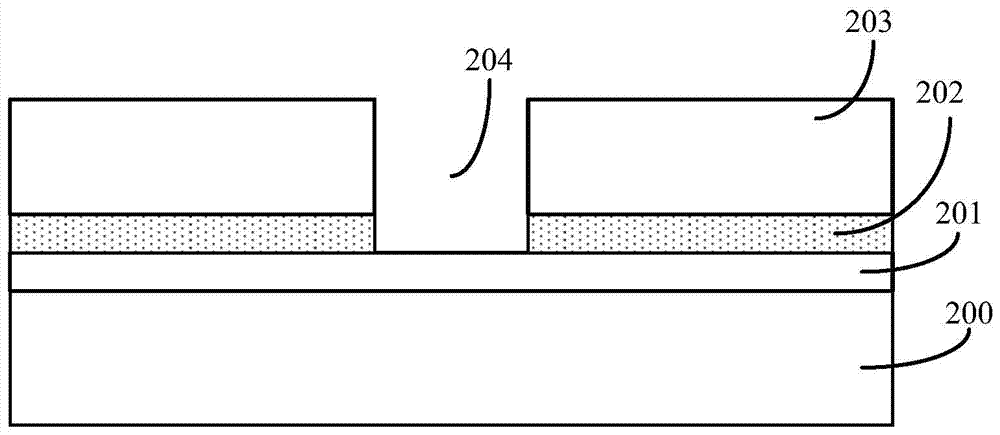

[0030]In order to reduce the size of the junctionless transistor, after research, a transistor is proposed, including: a first doped region located on the surface of the semiconductor substrate, the first doped region has first doped ions, so The first doping ions in the first doping region have a first concentration; the semiconductor layer located on a part of the surface of the first doping region and has the first doping ions, the first doping ions in the semiconductor layer Has a first concentration; a second doped region located in the semiconductor layer, the second doped region is located on the sidewall and top surface of the semiconductor layer, and has a first doped region in the second doped region Ions, the first doping ions in the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More