Multichannel synchronization and offset controllable circuit in single logic chip

A logic chip and multi-channel technology, applied in the direction of electrical digital data processing, instruments, etc., can solve the problems of no synchronization relationship, difficulty in meeting comprehensive performance requirements, multi-channel determinism and real-time performance cannot be guaranteed, and achieve real-time improvement Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0013] The technical solutions of the present invention are clearly and completely described below in conjunction with the accompanying drawings and specific embodiments. Obviously, the described embodiments are only a part of the embodiments of the present invention, not all of them. Based on the embodiments of the present invention, all other embodiments obtained by those skilled in the art without making creative work are all Belong to the protection scope of the present invention.

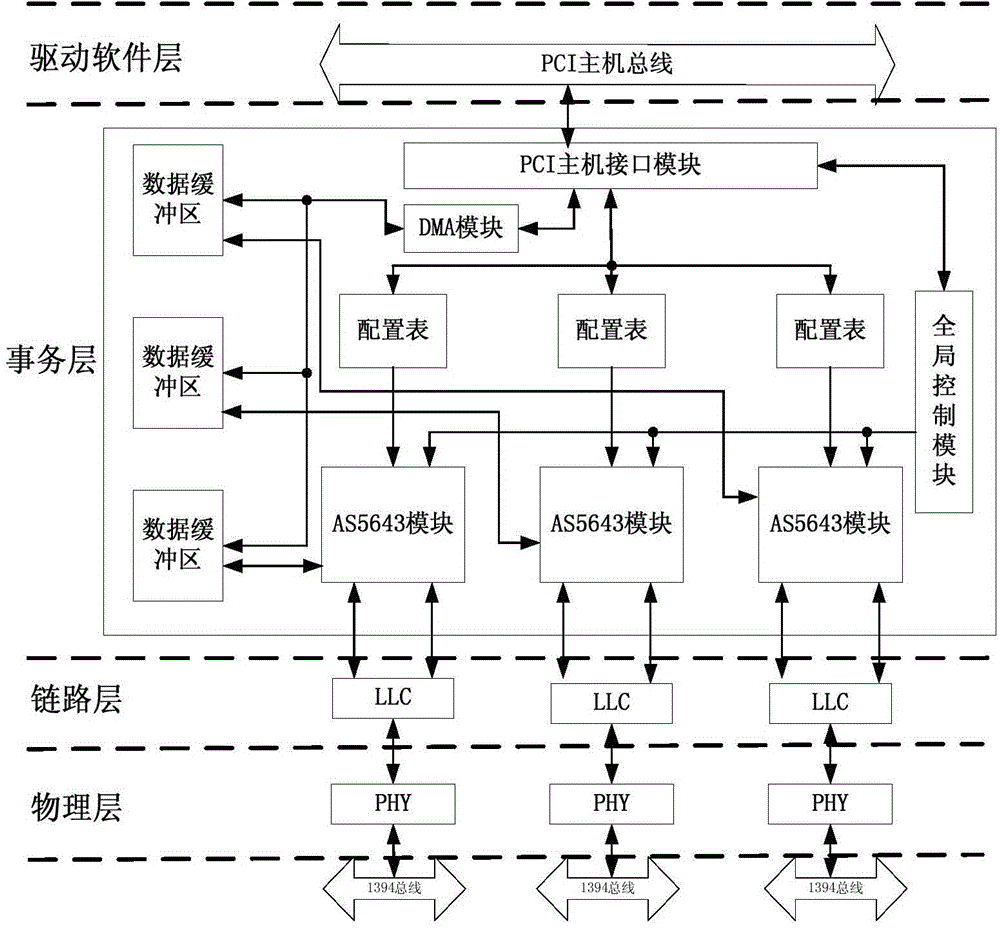

[0014] like figure 1 As shown, this embodiment provides a multi-channel synchronization and channel offset controllable circuit, which mainly includes the following modules:

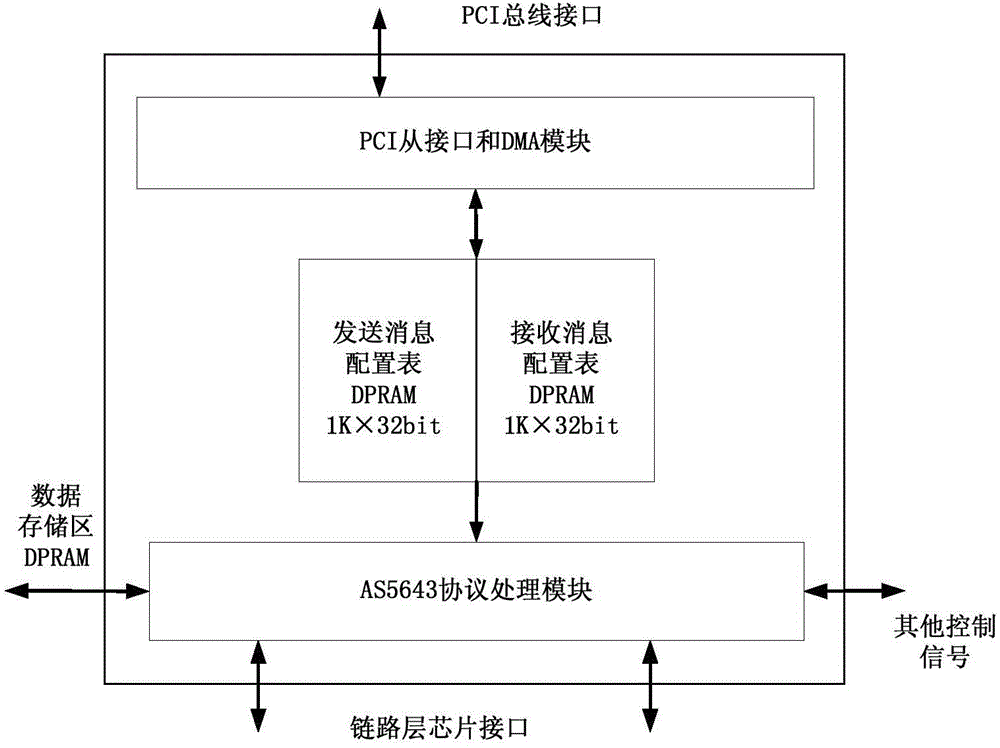

[0015] Host interface: The host interface adopts the standard PCI bus interface, which complies with the PCIv2.2 electrical specification and does not support hot swapping. The PCI slave interface module works as a slave device of the bus. The PCI host interface is mainly responsible for filling in the configuration tab...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More