Asynchronous cache method, asynchronous cache and integrated circuit

An asynchronous buffering and integrated circuit technology, applied in instruments, electrical digital data processing, data conversion, etc., can solve the problems of increasing the space occupied by FIFO buffers, wasting the addressing space of FIFO buffers, and being unfavorable for equipment miniaturization, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Example Embodiment

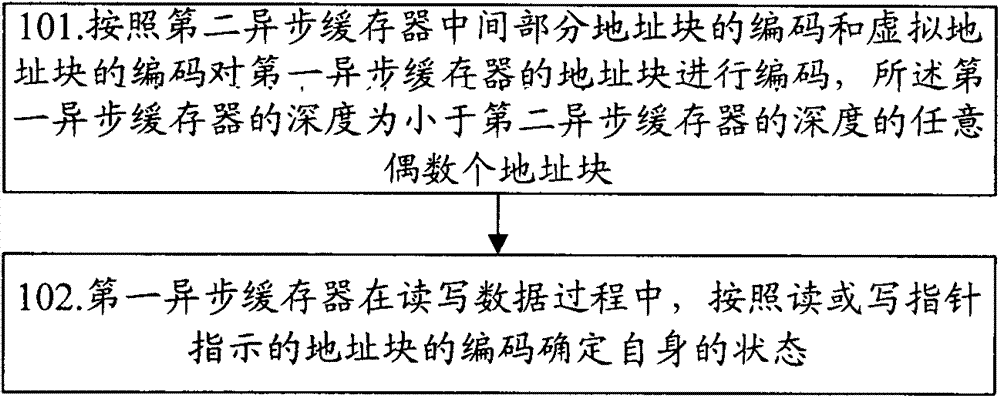

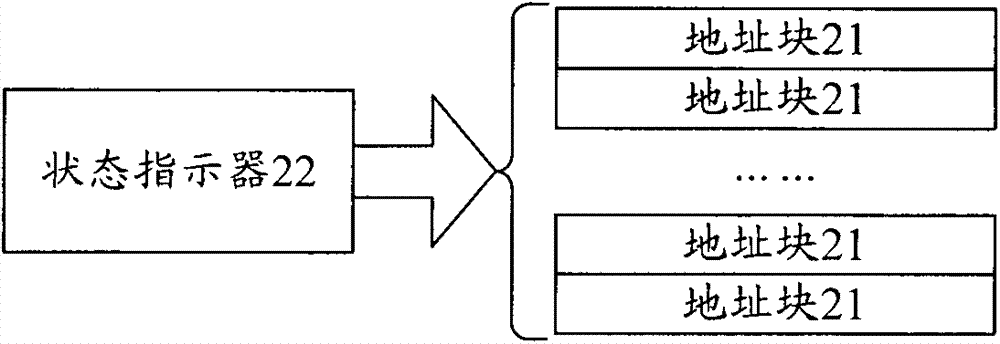

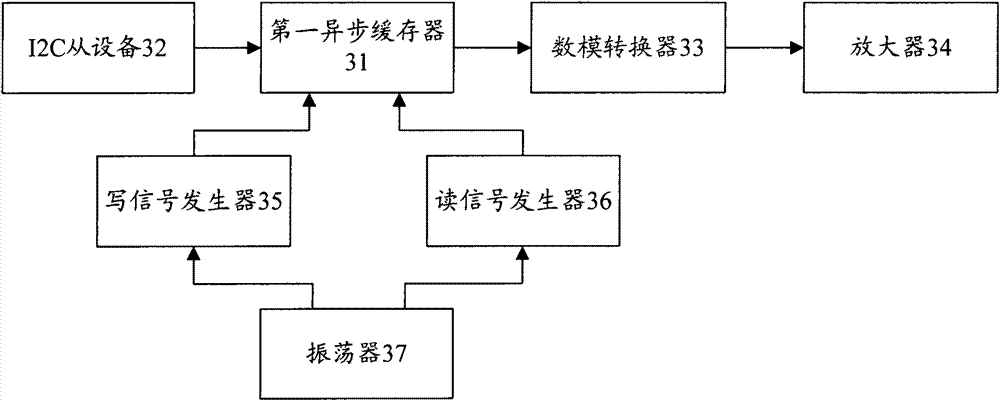

[0021] In the embodiment of the present invention, the address block of the first asynchronous buffer is encoded according to the encoding of the middle part of the second asynchronous buffer and the encoding of the virtual address block, and the depth of the first asynchronous buffer is smaller than that of the second asynchronous buffer. Any even number of address blocks of the depth of the buffer, the first asynchronous buffer determines its own state according to the code of the address block indicated by the read or write pointer in the process of reading and writing data.

[0022] Both the first asynchronous buffer and the second asynchronous buffer described in the embodiment of the present invention may be FIFO buffers.

[0023] Hereinafter, the present invention will be further described in detail through the drawings and specific embodiments.

[0024] The embodiment of the present invention implements an asynchronous caching method, such as figure 1 As shown, the method inc...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap