Circuit and method performed by the circuit

A circuit and residual voltage technology, applied in the field of analog-to-digital converters, can solve the problem of high consumption cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

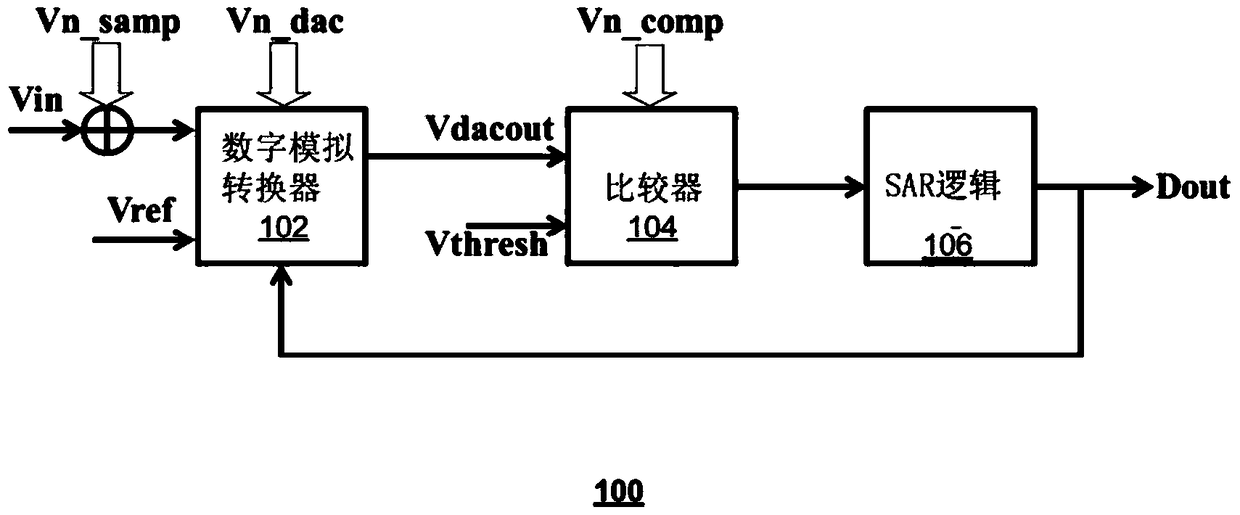

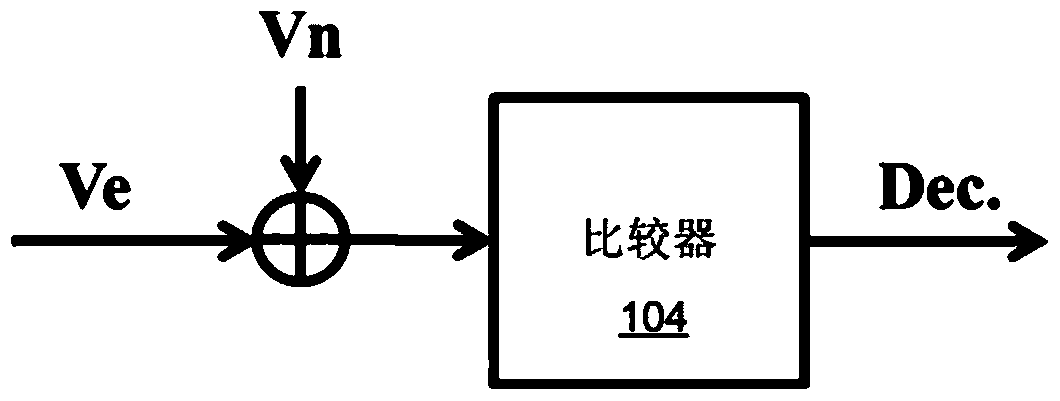

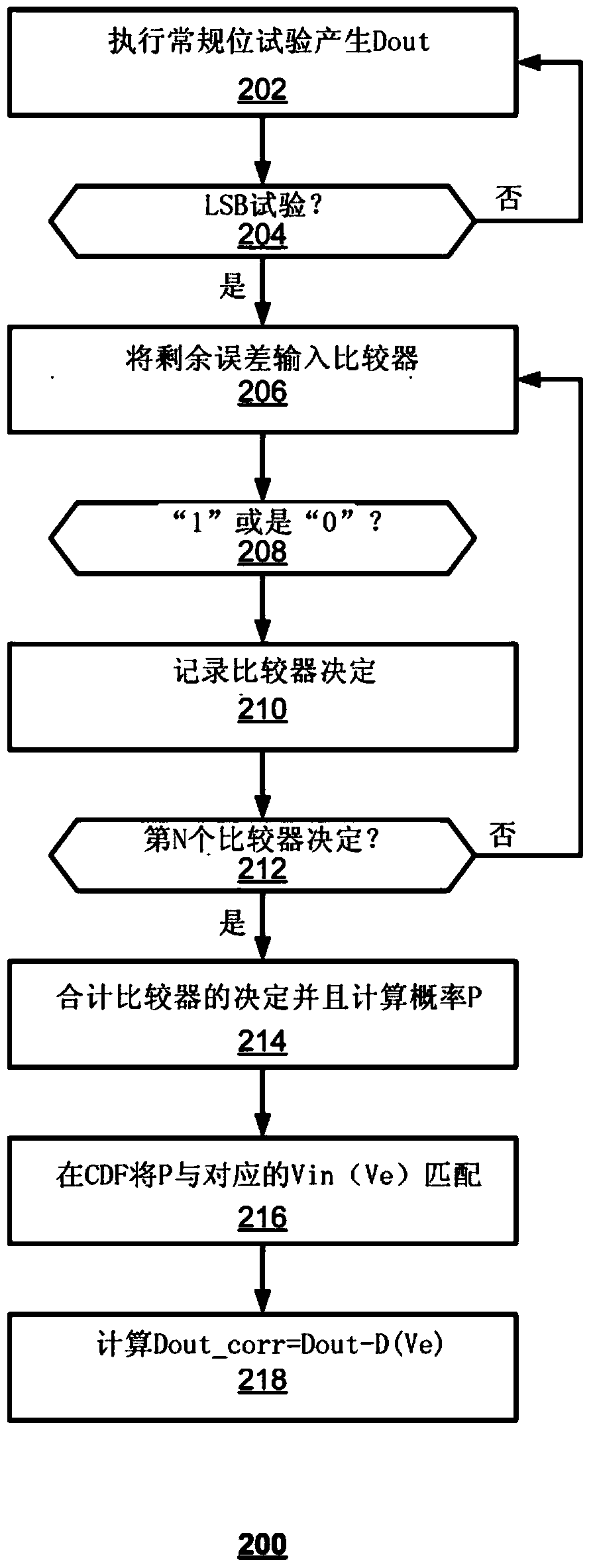

[0018] An example embodiment of the invention may provide a method comprising performing a bit trial, converting an analog input signal to a digital output signal using a SARADC including a comparator; after the bit trial is complete, measuring the residual voltage at the input of the comparator, and then based on the measured residual Error adjusted digital output signal.

[0019] An example embodiment of the present invention may provide a method comprising conventional bit trials performed to convert an analog input signal into a digital output signal using a SAR ADC from the MSB to a predetermined least significant bit of the ADC; after the predetermined least significant bit trial, equal to And / or execute the additional bit test when it is less than the predetermined low significant bit test range; and combine the results of the conventional bit test and the additional bit test to generate a digital output signal based on the corresponding bit weight.

[0020] Exemplary e...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More