A Parallel Pseudo-CSD Encoder for Variable Coefficient Multipliers

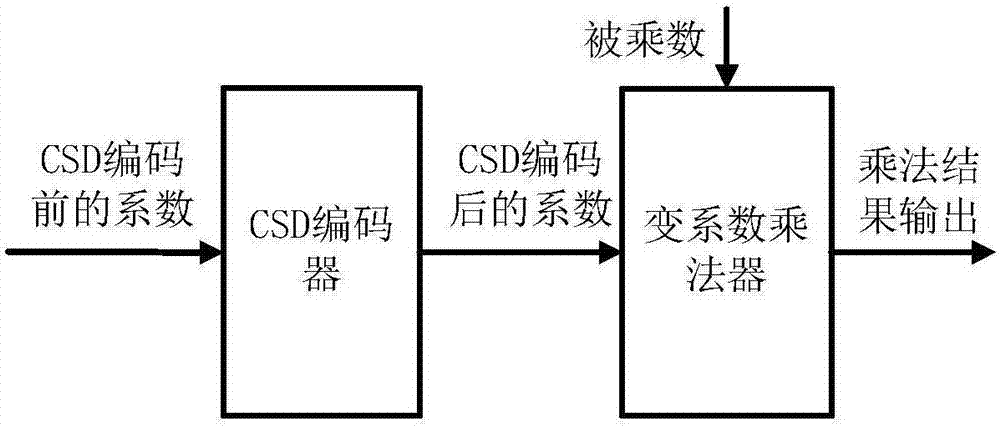

A multiplier and variable coefficient technology, which is applied in the field of integrated circuits, can solve the problems of limited number of code bits in data throughput, restrict the working speed and data throughput of multipliers, and achieve the effect of improving data throughput and operation speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The present invention is described in detail below in conjunction with accompanying drawing

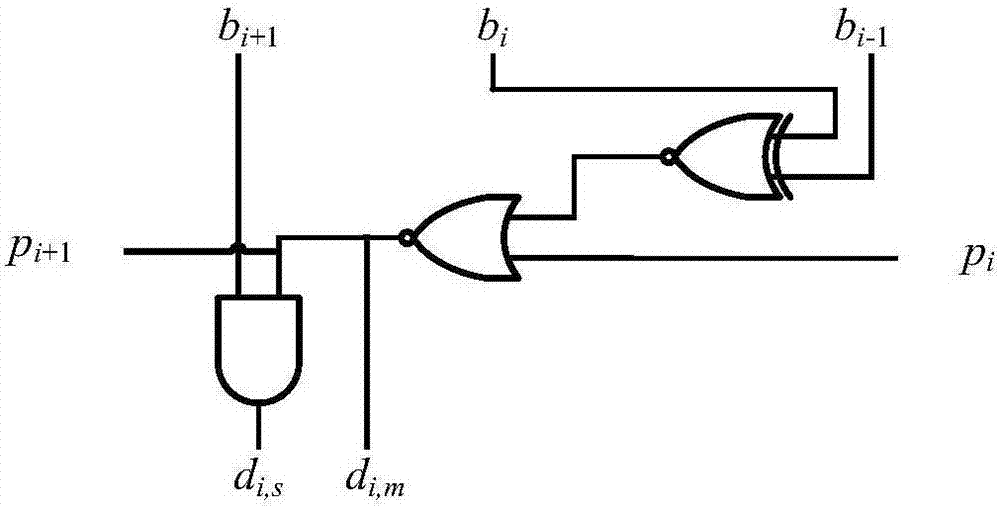

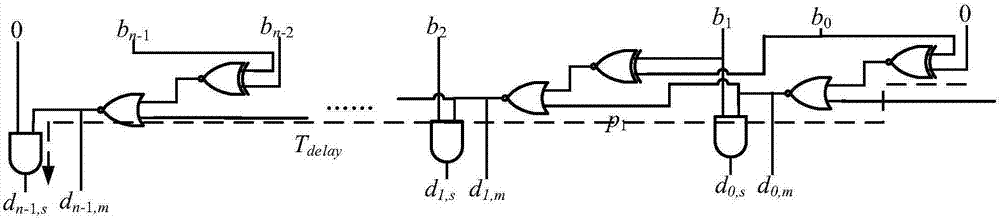

[0025] In order to eliminate the delay caused by the recursive transfer generated by the carry logic used by the traditional CSD encoder, the invention changes the traditional CSD coding algorithm and adopts a parallel calculation mode without carry logic. Pseudo-CSD encoding is almost the same as traditional CSD encoding, the only difference is: for a sequence composed of two consecutive "1", that is, "0110" sequence, traditional CSD encoding obtains a signed number sequence of "1010", and this special The sequence remains "0110" in the pseudo-CSD encoding, thus achieving the same number of non-zero bits as in the traditional CSD encoding. At the same time, the pseudo-CSD coding algorithm proposed by the present invention eliminates the carry logic, thereby realizing parallel operation.

[0026] This example works as follows:

[0027] In this example, it is mainly divided in...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More