Device and method for predicting function return address

A return address and return address stack technology, applied in electrical digital data processing, program control design, instruments, etc., can solve problems such as limited function size, and achieve the effect of reducing costs and improving processor performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

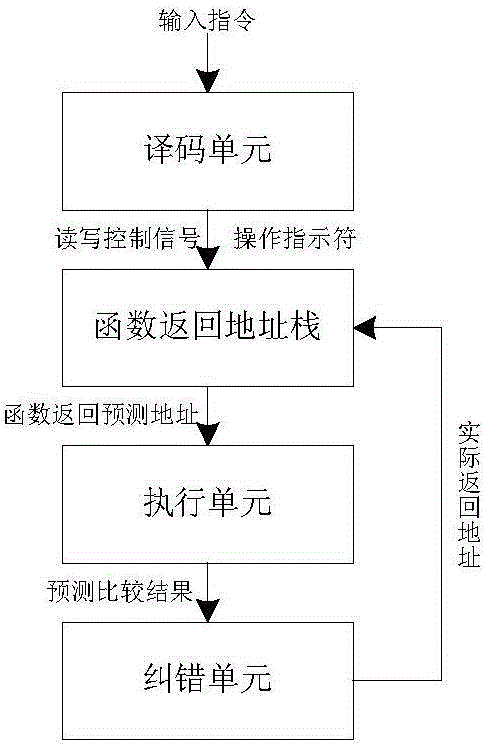

[0033] refer to Figure 1 ~ Figure 4 A function return address prediction device includes a decoding unit, a function return address stack, an execution unit and an error correction unit.

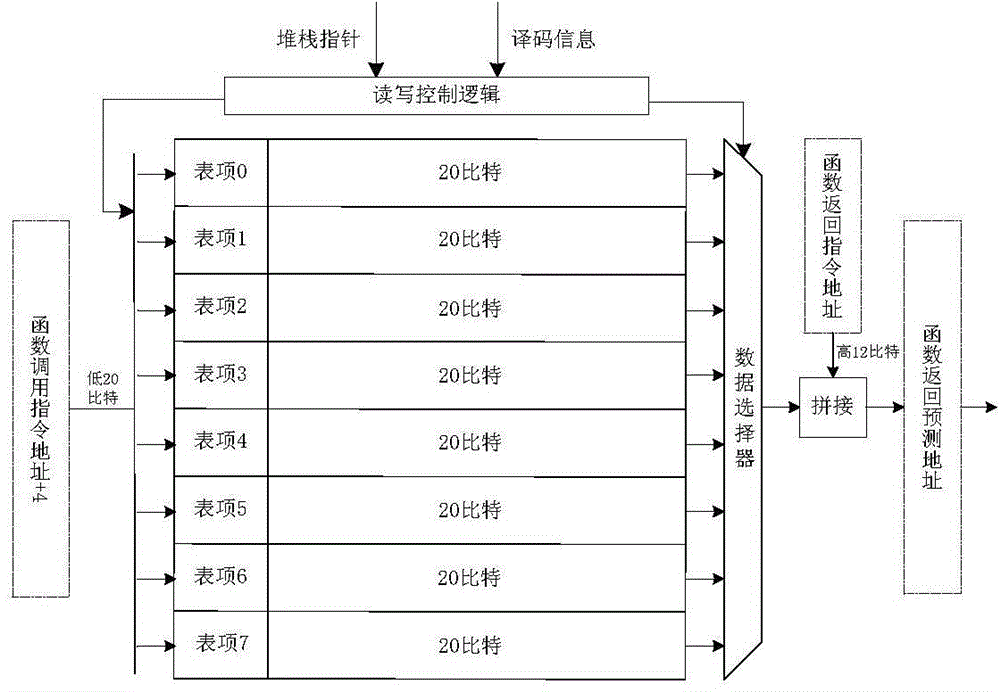

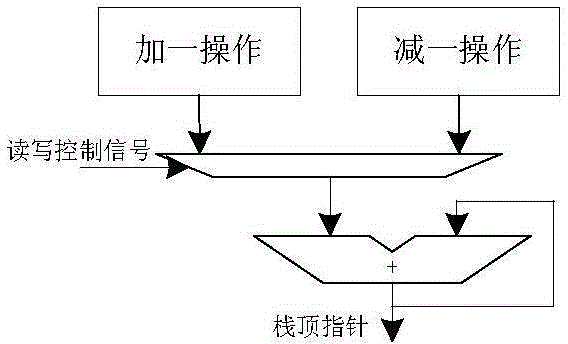

[0034] The instruction decoding unit decodes the input instruction to obtain operation indicator, register index and other information. The operation indicator includes instruction type, operand type, operand number and so on. Instruction types can include arithmetic instructions, memory access instructions, conditional transfer instructions, unconditional transfer instructions, and indirect transfer instructions. Among them, the function call and function return instructions in the indirect transfer instructions must be decoded by the decoding unit. Register index information helps determine function return instructions and provides address information for indirect branch instructions. When the instruction decoding unit decodes the current input instruction as a function call instructio...

Embodiment 2

[0040] refer to Figure 5 , a method for function return address prediction, the method includes the following steps:

[0041] 1) Decode the instruction, decode the function call instruction and the function return instruction, and generate an operation indicator;

[0042] 2) When the instruction is decoded as a function call instruction, the low M bits of the address of the next instruction are intercepted and stored in the function return address stack; when the instruction is decoded as a function return instruction, the latest entry is popped from the function return address stack The M-bit address of the stack table entry is spliced with the high (N-M) bit address of the function return instruction, encapsulated to generate the predicted address A of the function return instruction, and the table entry index X corresponding to the predicted address A is recorded;

[0043] 3) When the operation indicator indicates a function return instruction, it is judged whether the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More