Patents

Literature

37results about How to "Reduce data width" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

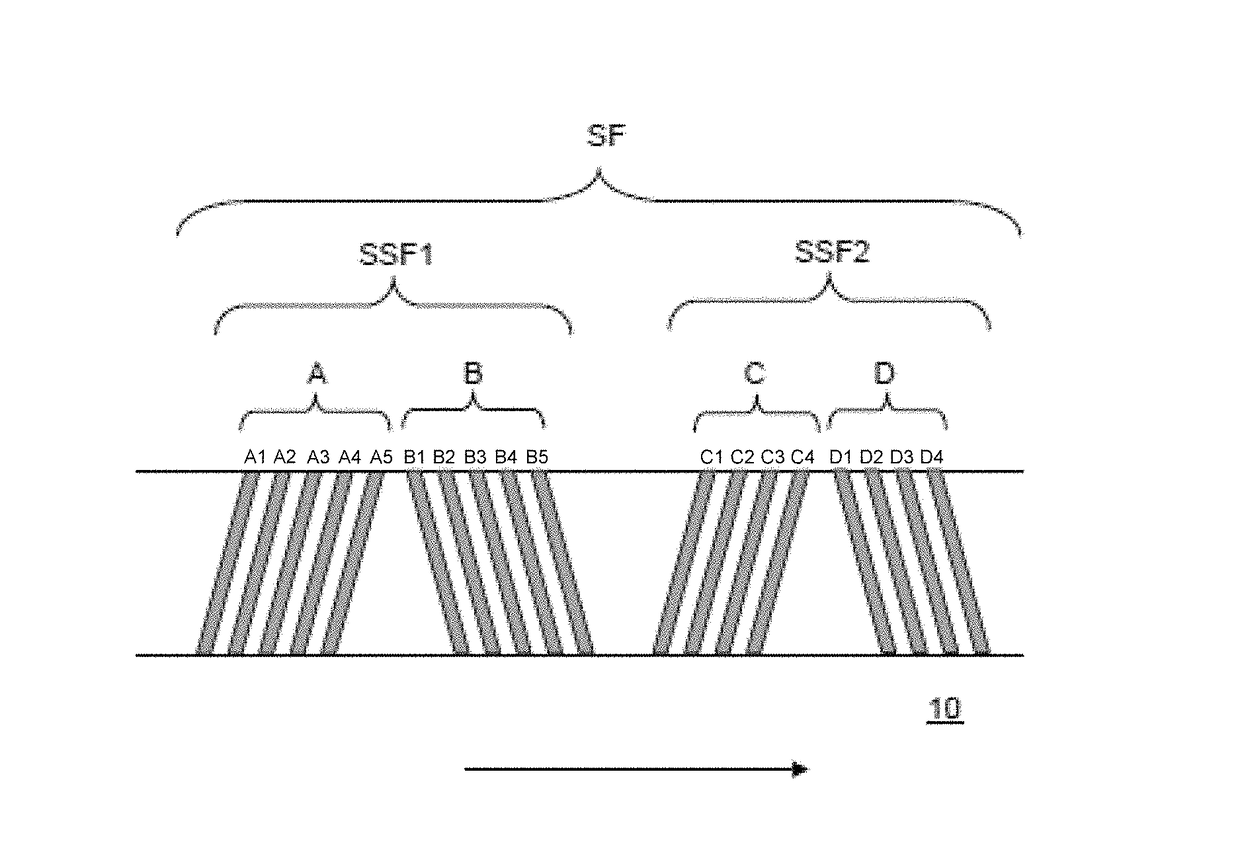

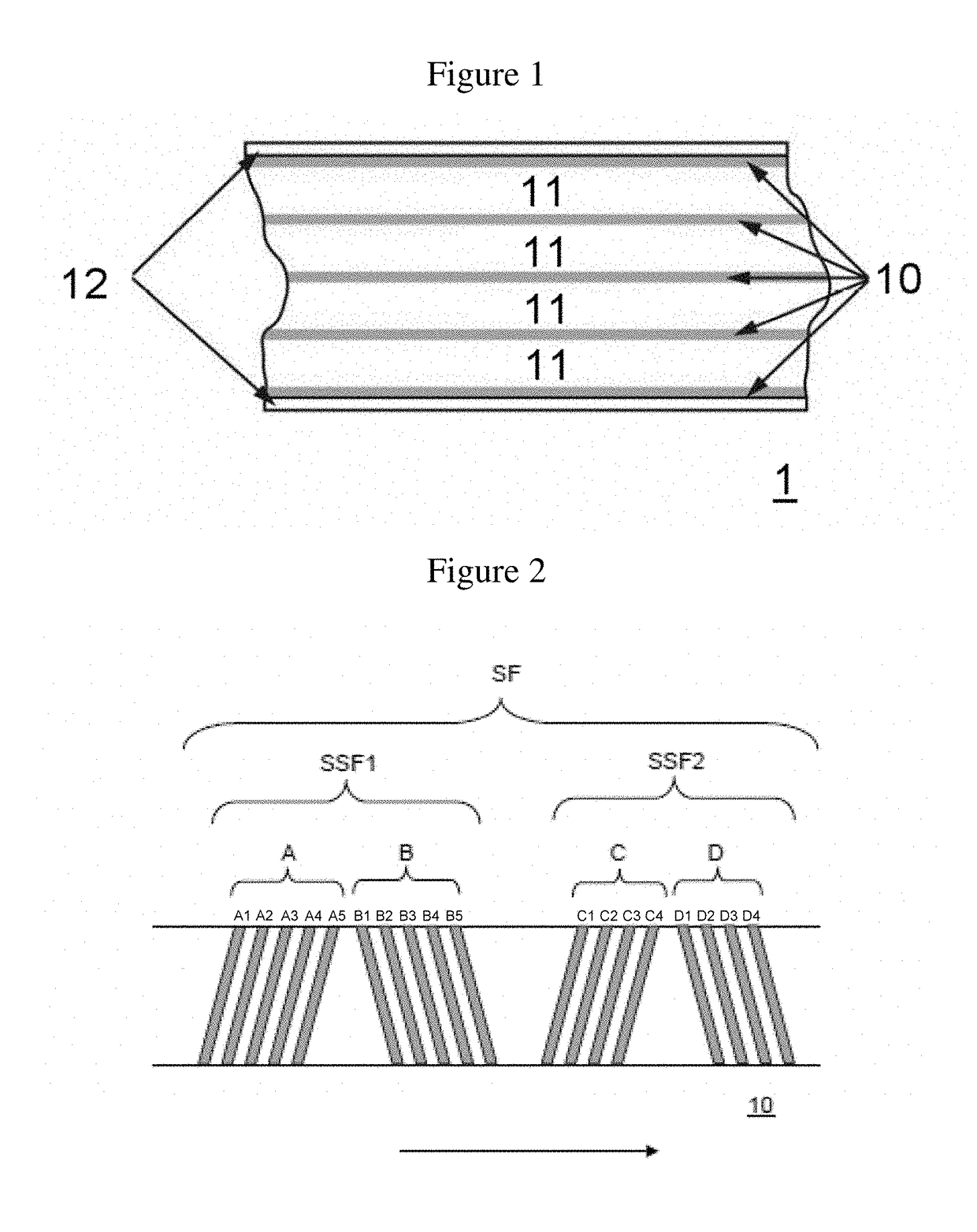

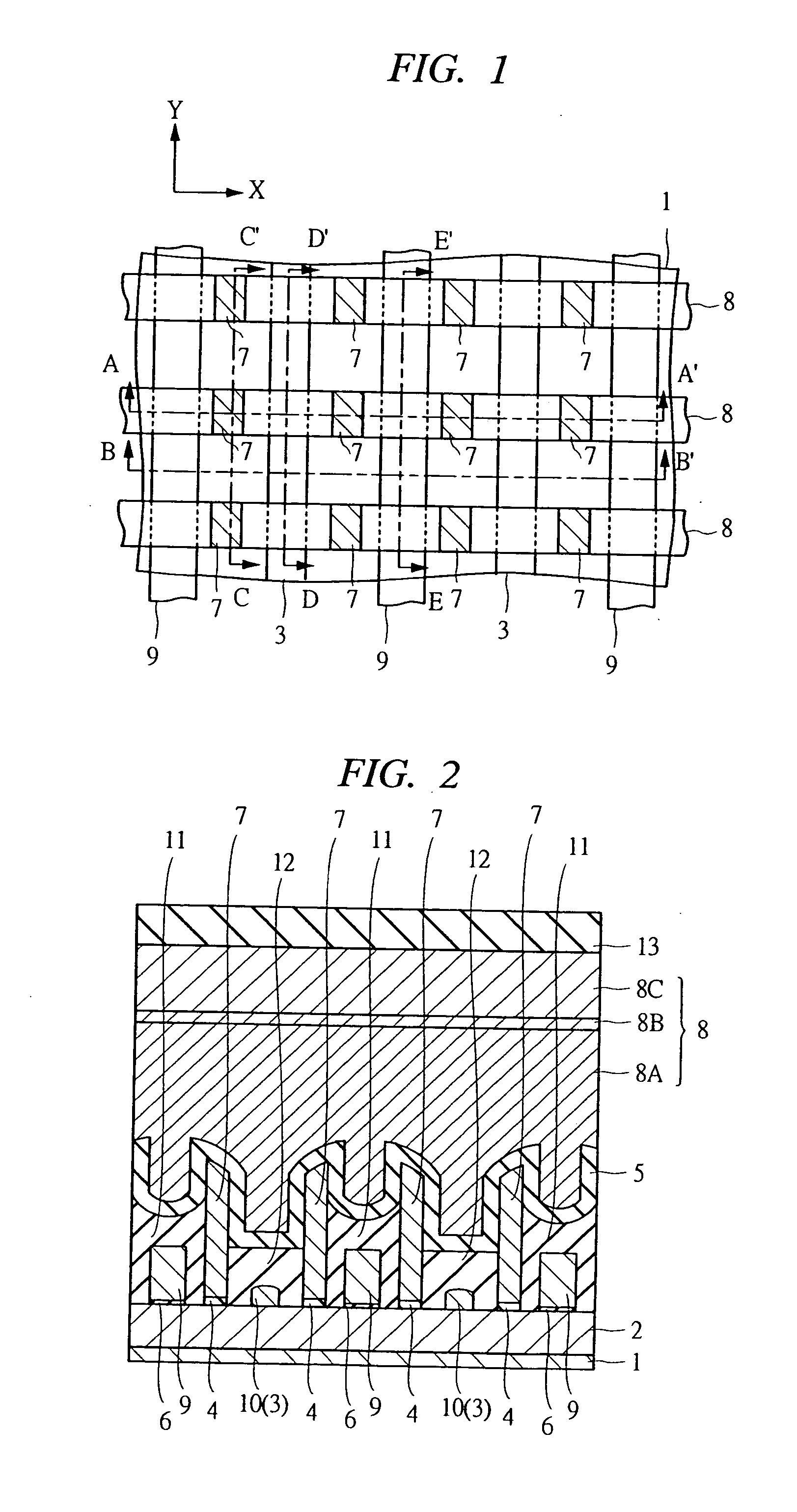

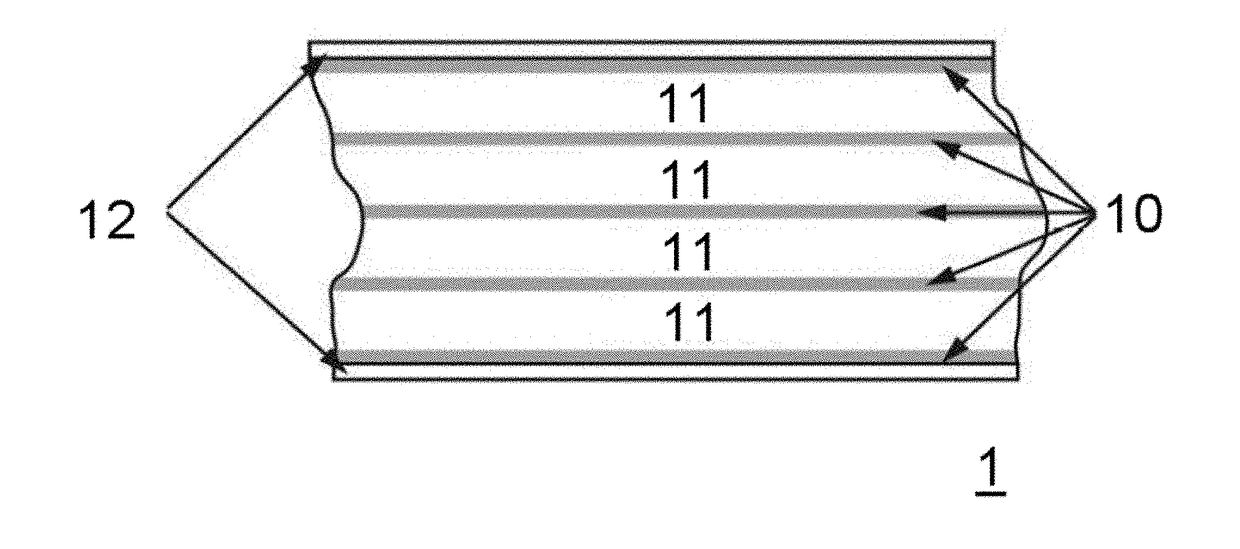

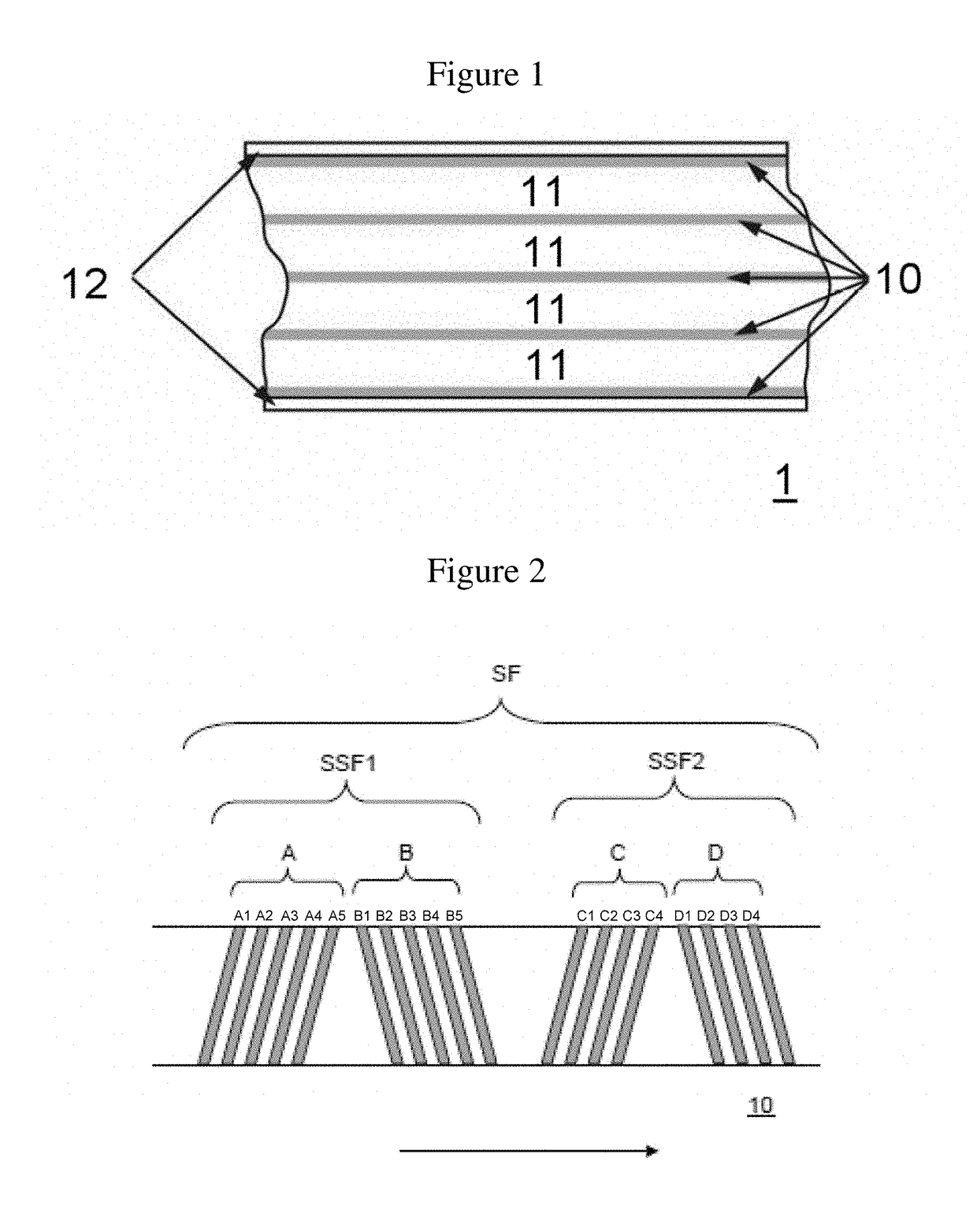

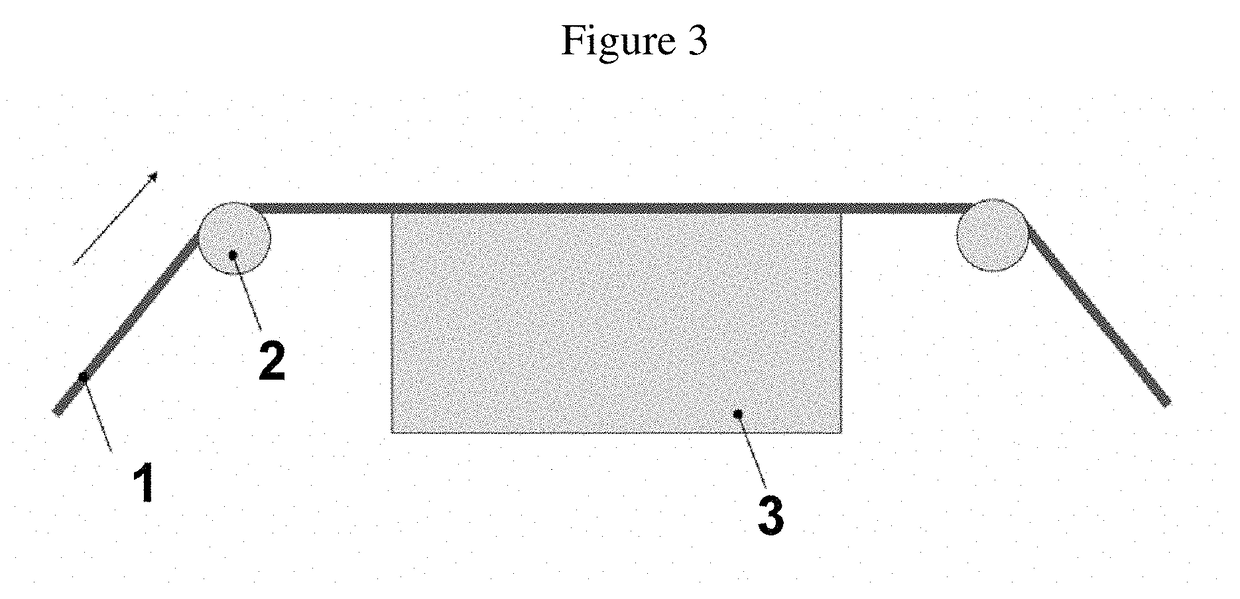

Magnetic tape and magnetic tape device

ActiveUS9837116B2Increase the number ofIncrease recording capacityAlignment for track following on tapesRecord information storageMagnetic tapeSurface roughness

Owner:FUJIFILM CORP

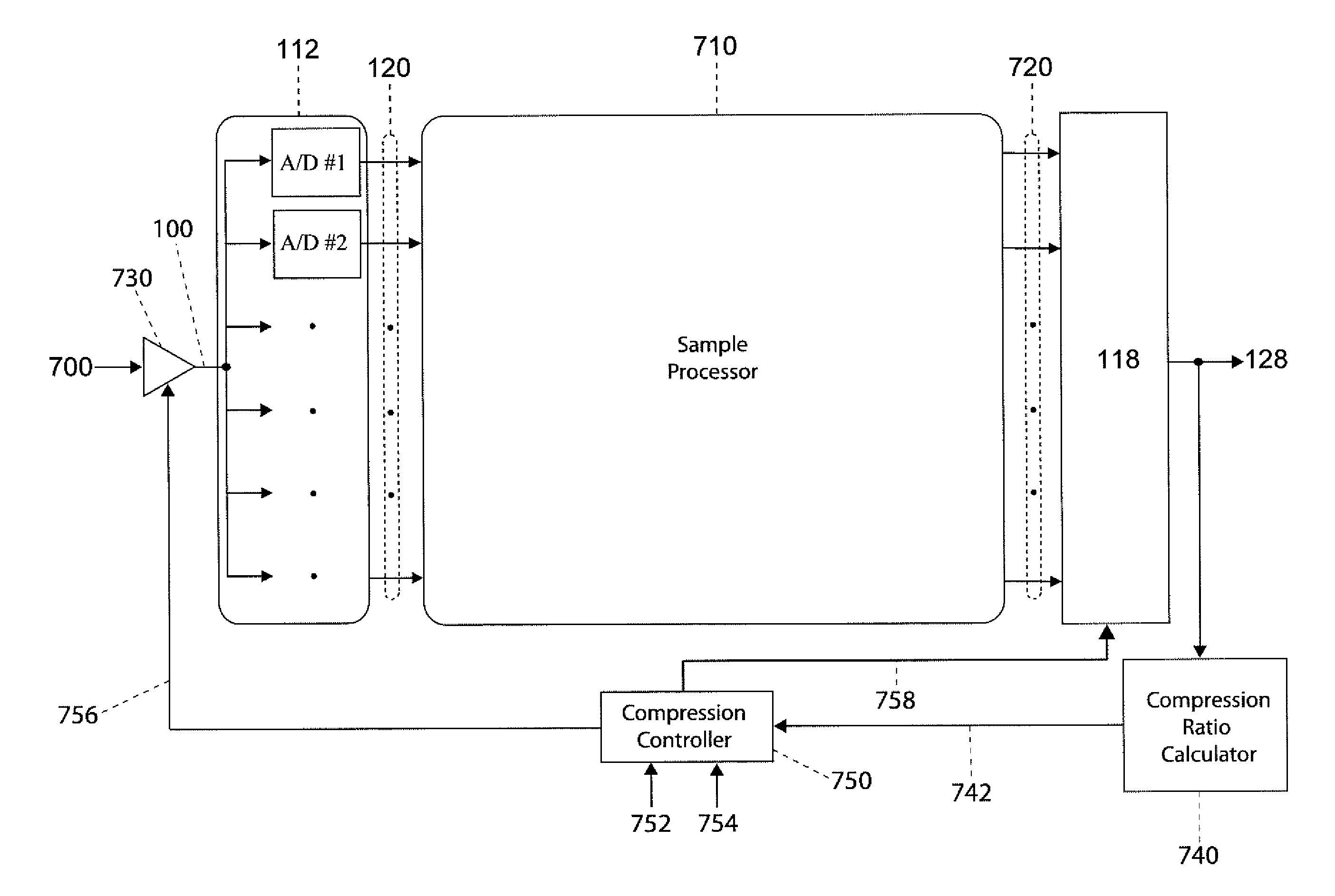

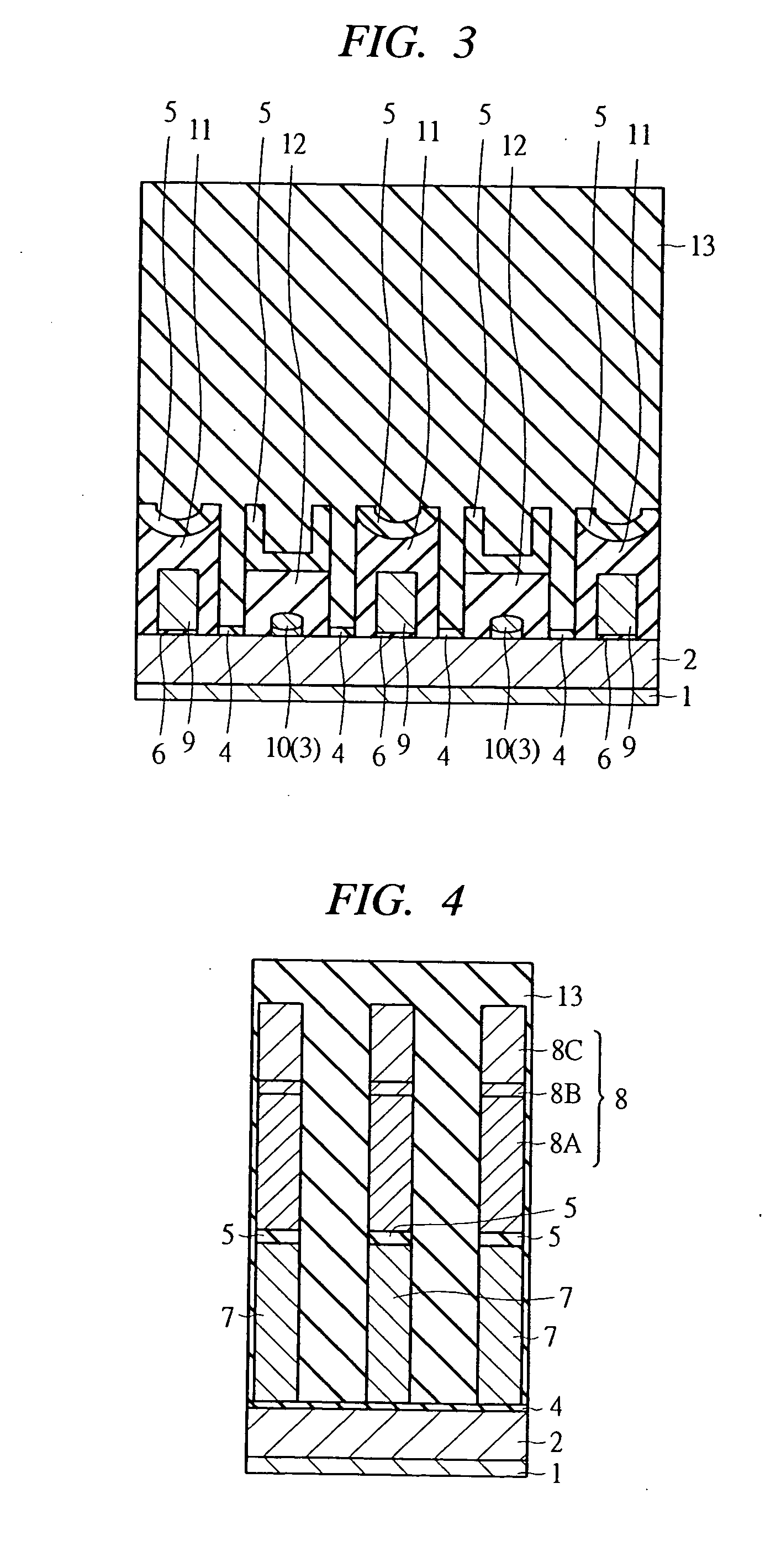

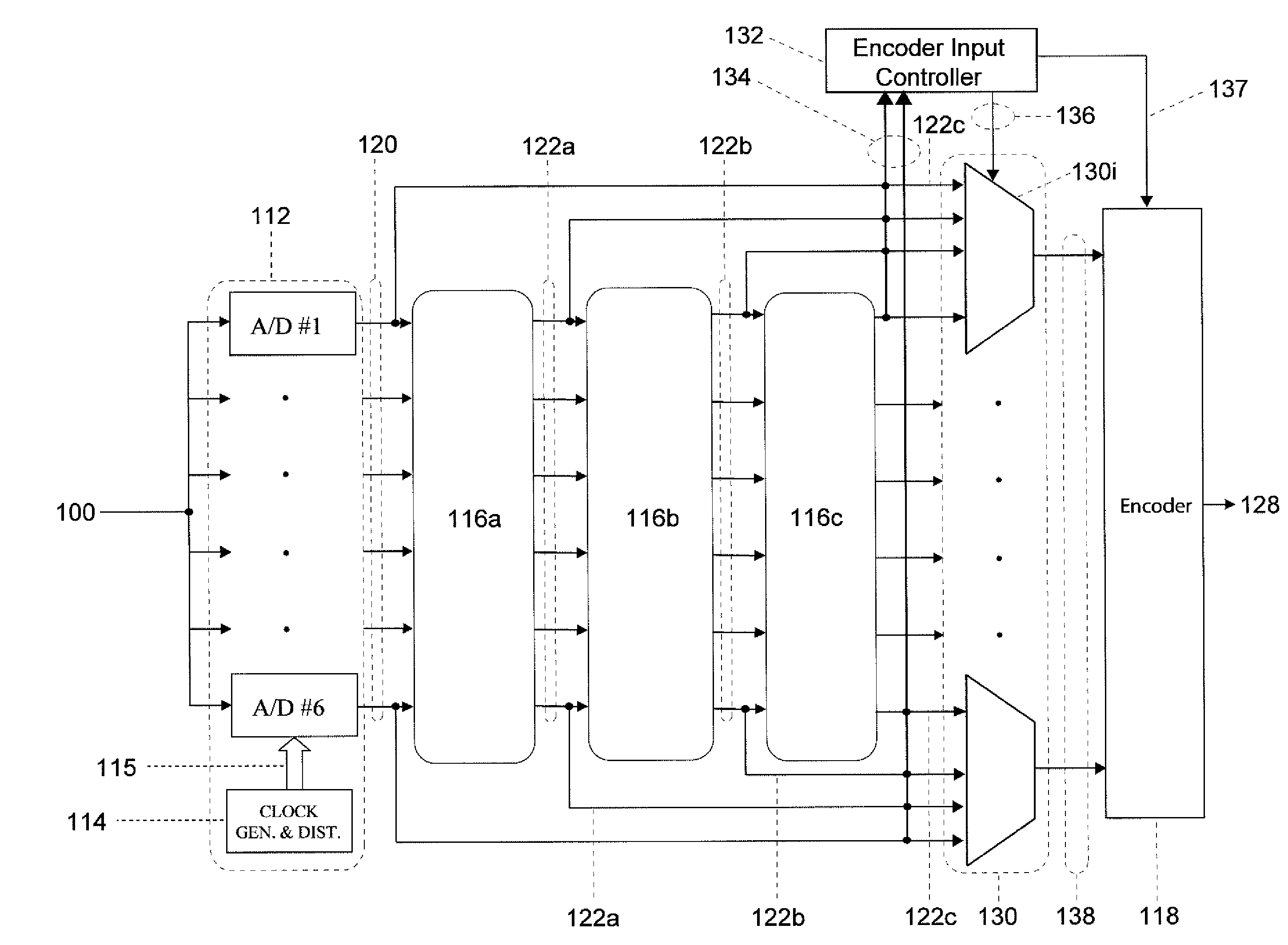

Enhanced Time-Interleaved A/D Conversion Using Compression

InactiveUS20080018502A1Increase the compression ratioDegrade signal qualityAnalogue/digital conversionBinary multiplierAnalog signal

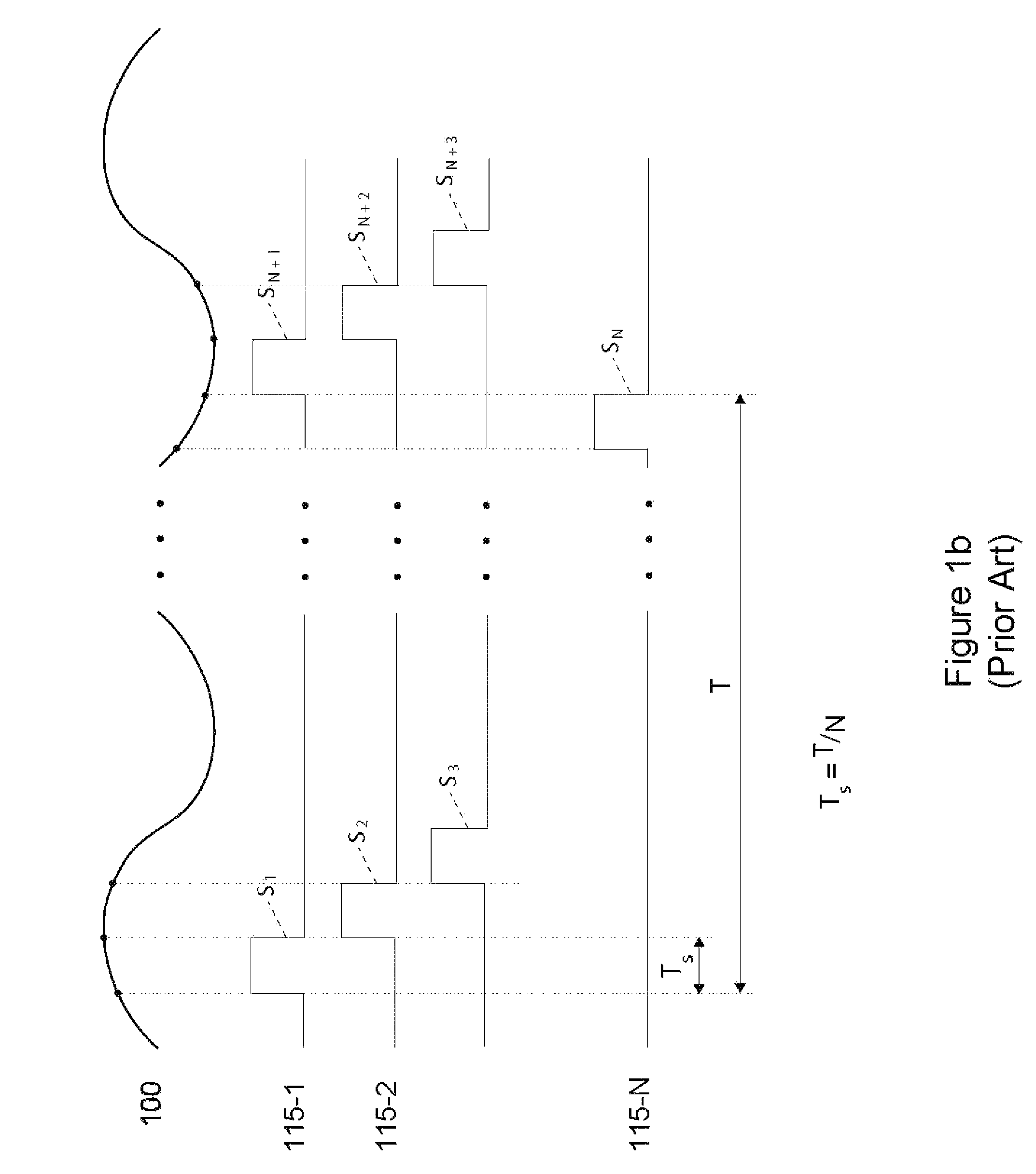

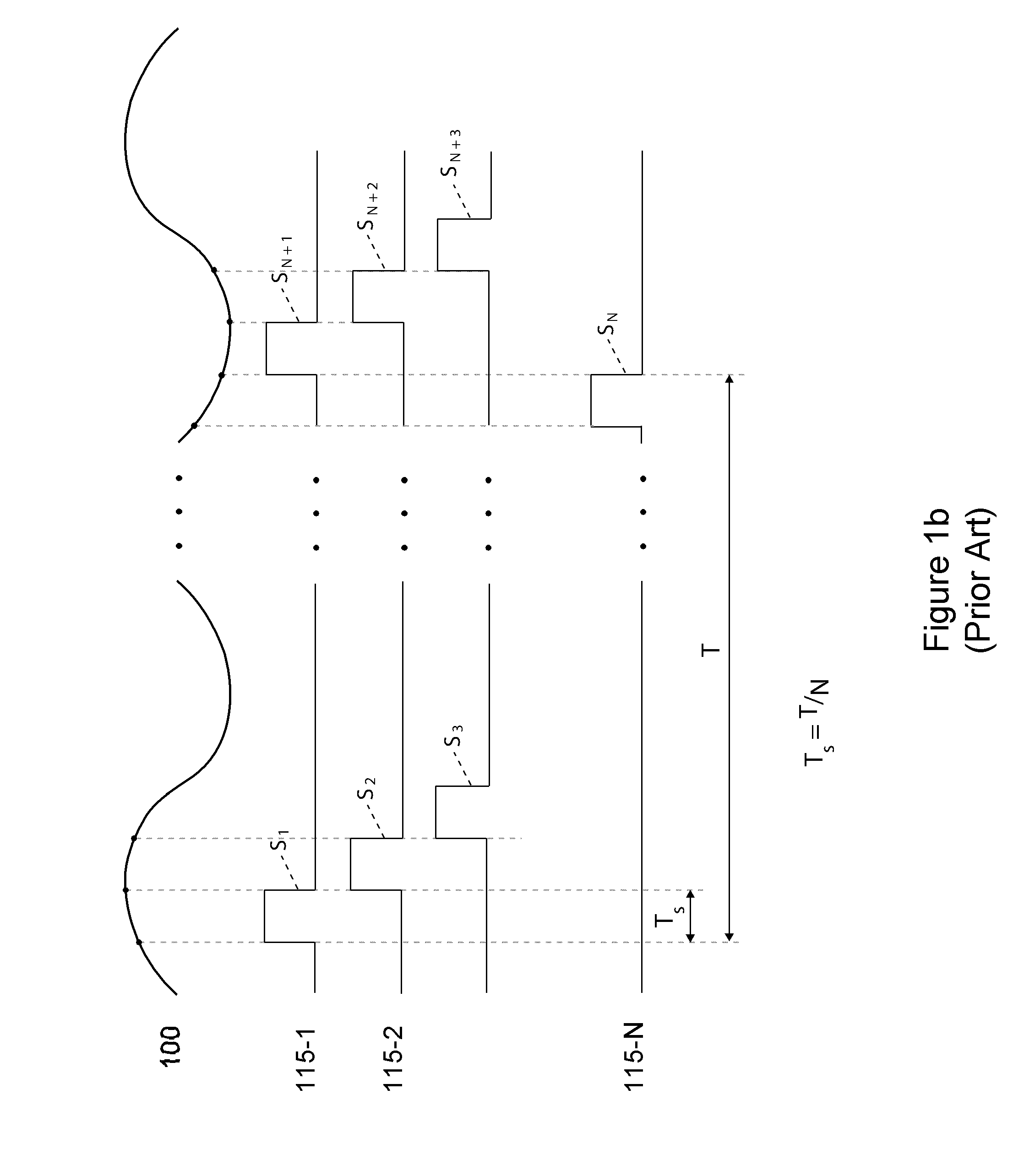

Compression of signal samples output from a parallel, time-interleaved analog to digital converter (TIADC) for a baseband signal, includes calculating first or higher order differences of consecutive signal samples followed by lossless or lossy encoding of the difference samples to produce compressed samples. Compression of a TIADC output signal with a nonzero center frequency, includes calculating sums or differences of pairs of signal samples separated by an appropriate number of sampling intervals followed by lossless or lossy encoding. The sums or differences of the signal samples have lower magnitudes than the original samples, allowing more efficient compression. Lossy compression alternatives produce compressed data with a fixed bit rate or with a fixed quality in the decompressed samples. Alternatives for lossy compression include attenuating the analog signal before sampling by the TIADC, applying bit shifters or multipliers after sampling to reduce the magnitudes of the signal samples, and lossy encoding.

Owner:ALTERA CORP

Enhanced time-interleaved A/D conversion using compression

InactiveUS7541950B2Improve efficiencyReduce data widthAnalogue/digital conversionBinary multiplierAnalog signal

Owner:ALTERA CORP

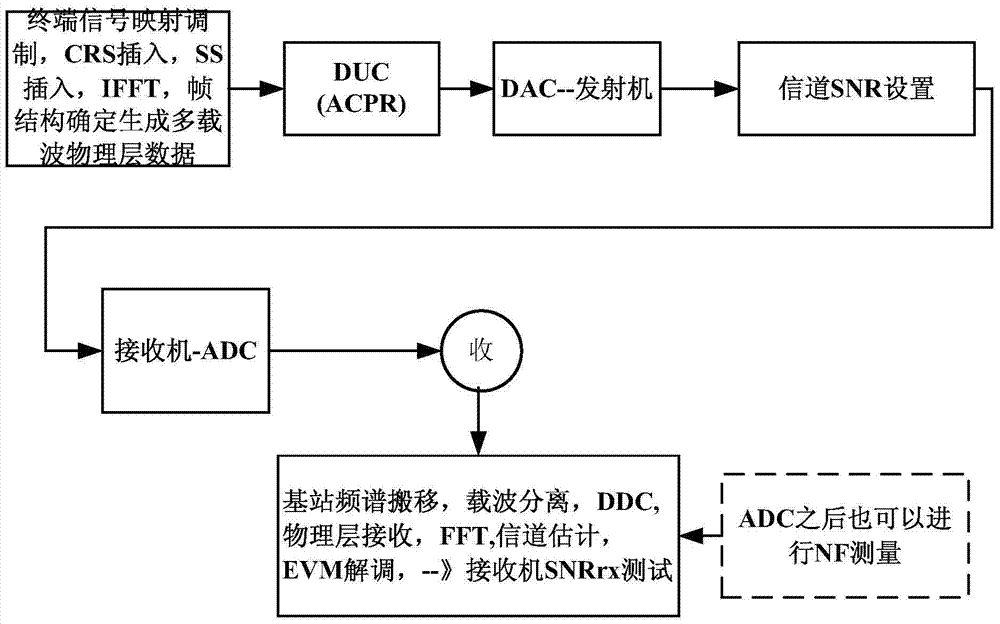

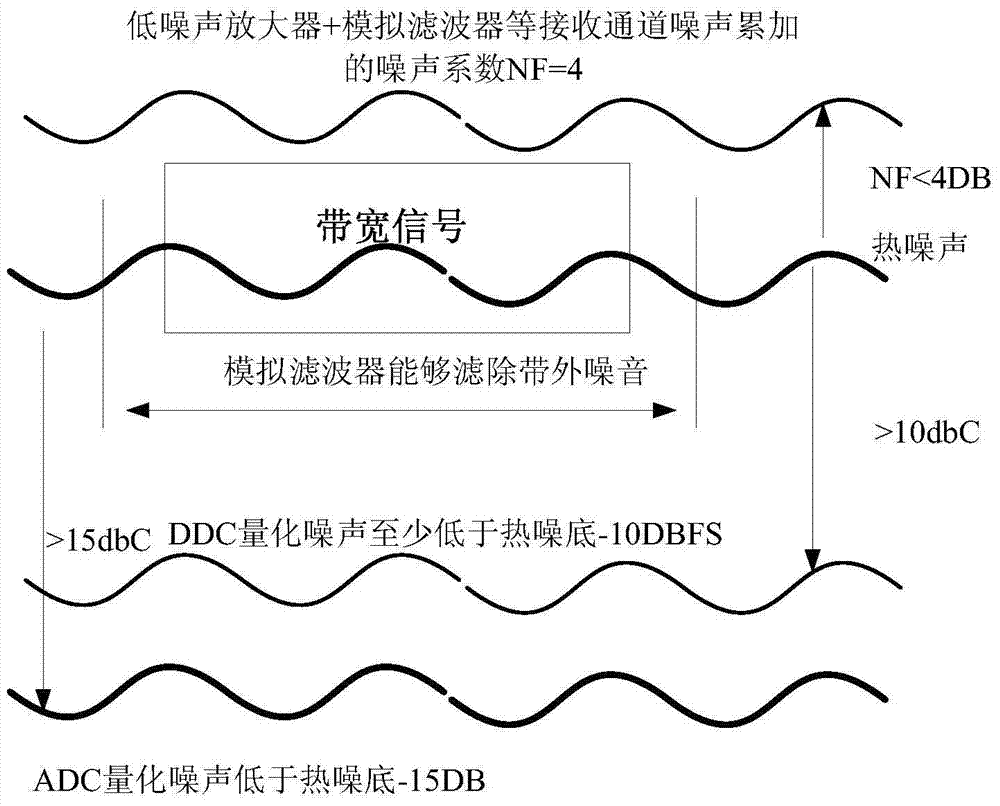

Uplink receiver of LTE base station system and data processing method thereof

InactiveCN103428149AReduce transmission costsSave resourcesMulti-frequency code systemsWireless communicationTraffic capacityData transmission

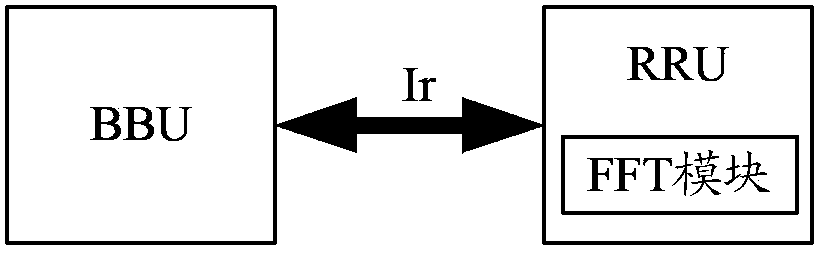

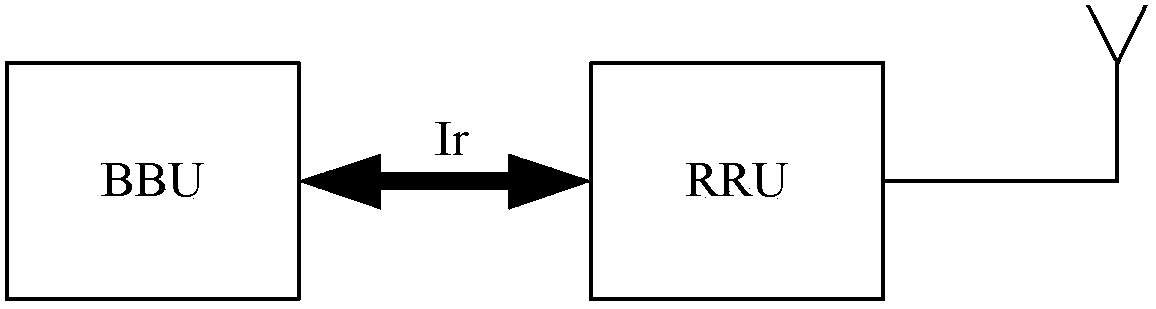

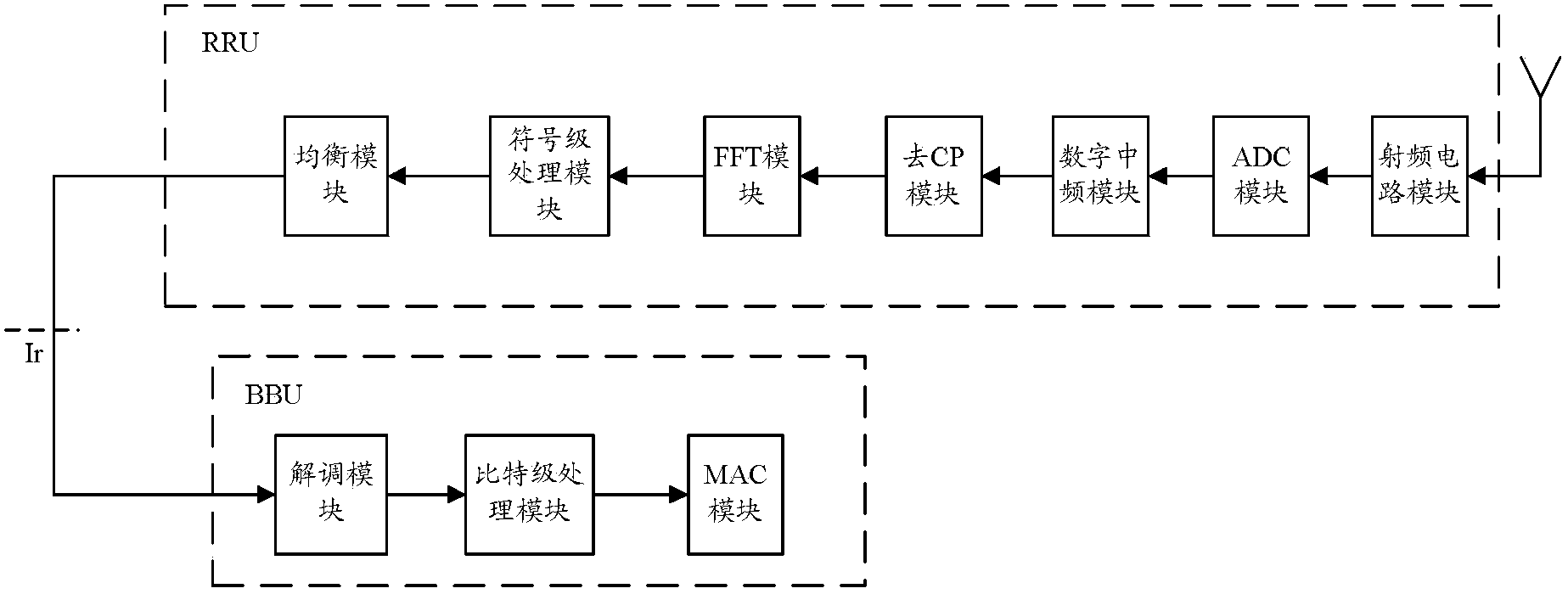

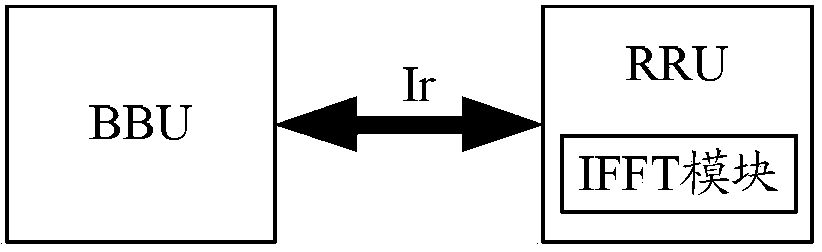

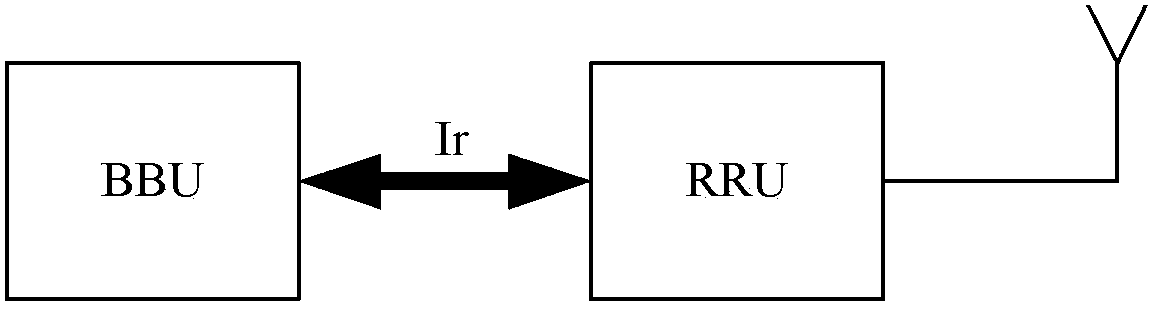

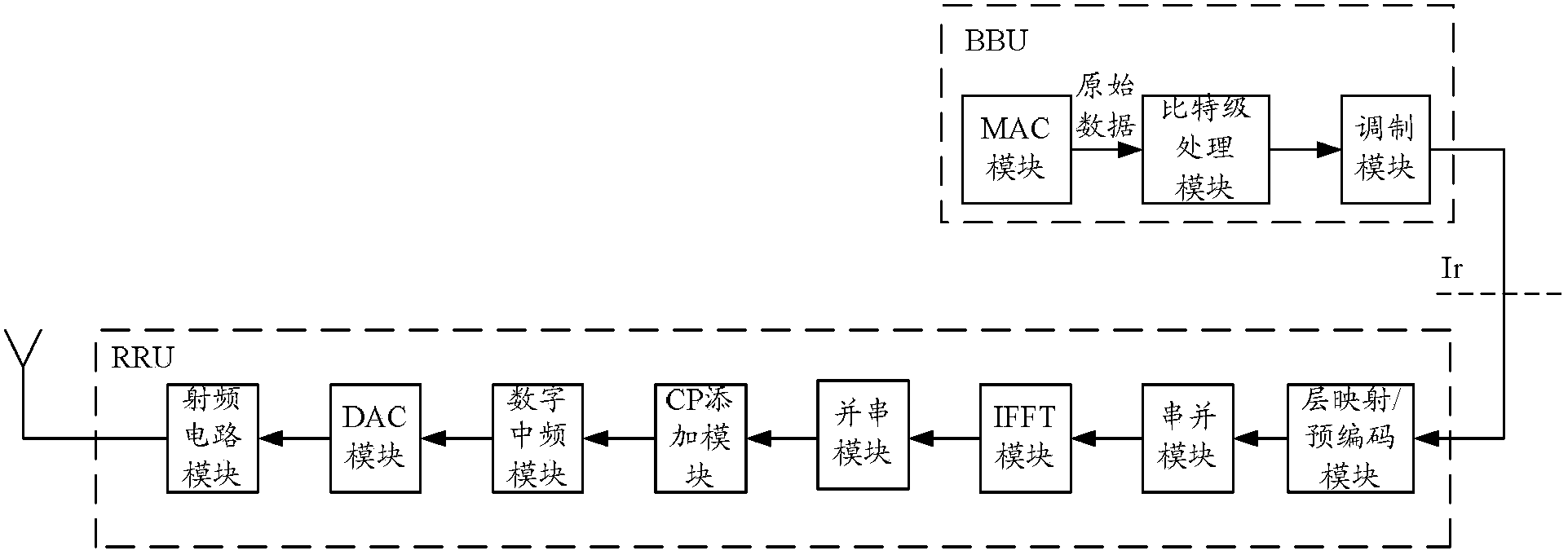

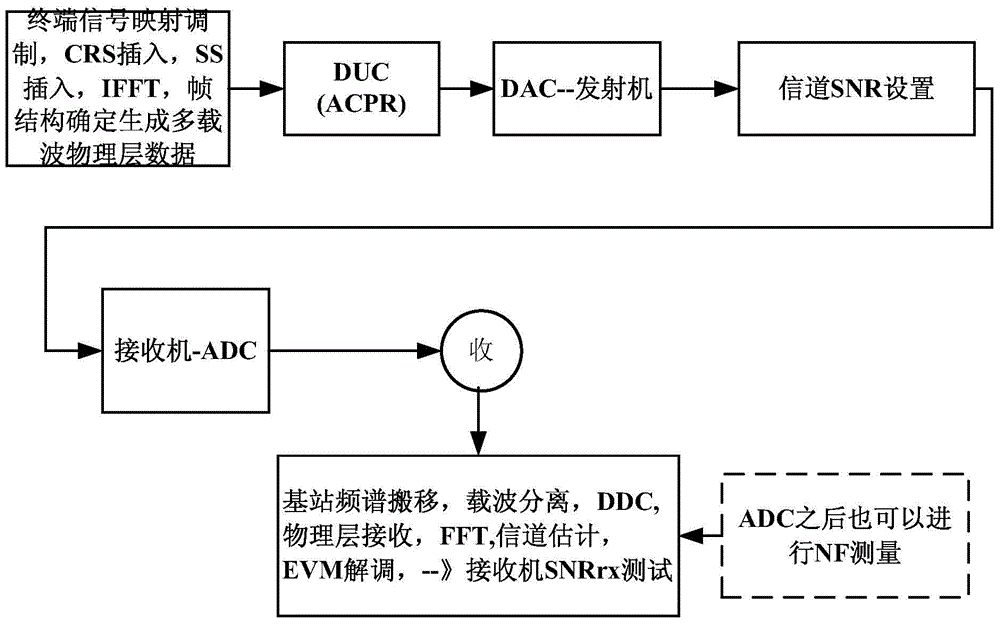

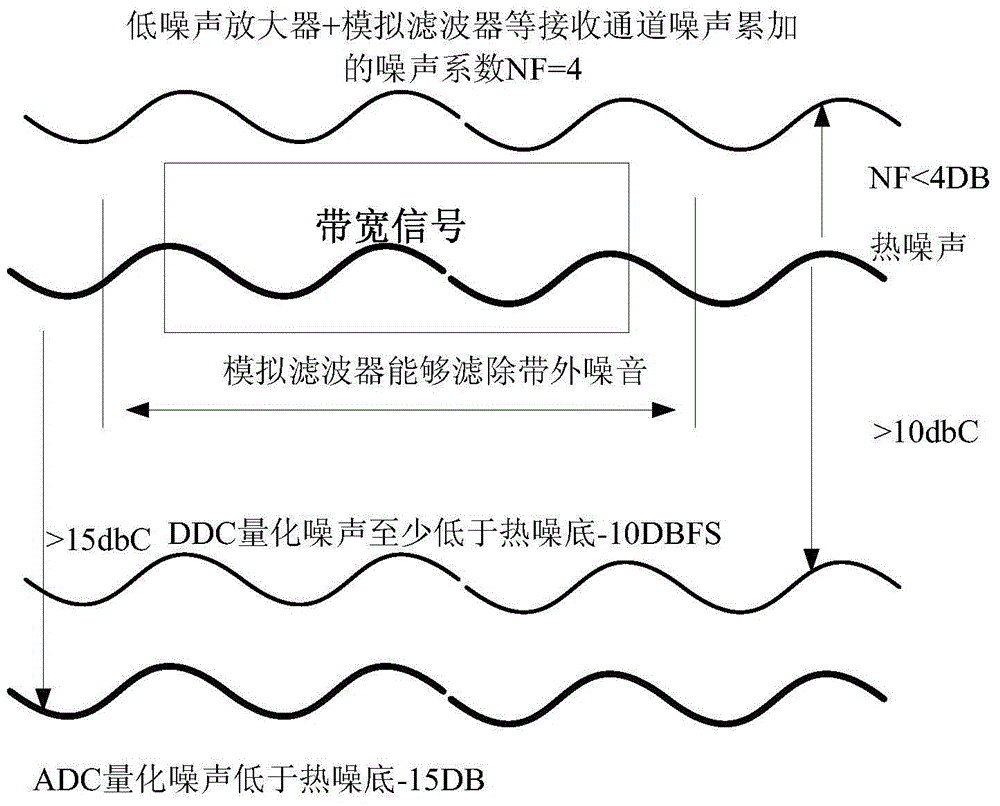

The invention discloses an uplink receiver of a long term evolution (LTE) base station system. The uplink receiver comprises a base band unit (BBU) and a remote radio unit (RRU); the BBU and the RRU are connected by an interface Ir (interface between the RRU and the BBU). The RRU includes a fast fourier transformation (FFT) module. The RRU is used for receiving data, carrying out FFT processing on the received data, and sending the processed data to the BBU by the Ir; and the BBU is used for receiving the data from the RRU by the Ir. Correspondingly, the invention also discloses a data processing method of the uplink receiver. The sampling rate and the data bit width are reduced. Therefore, the Ir uplink data transmission flow is effectively reduced, the cost of transmission from the RRU to the BBU is lowered, and the optical fiber resources laid at the Ir are saved; and thus an objective of saving of the equipment cost and the maintenance cost is achieved.

Owner:ZTE CORP

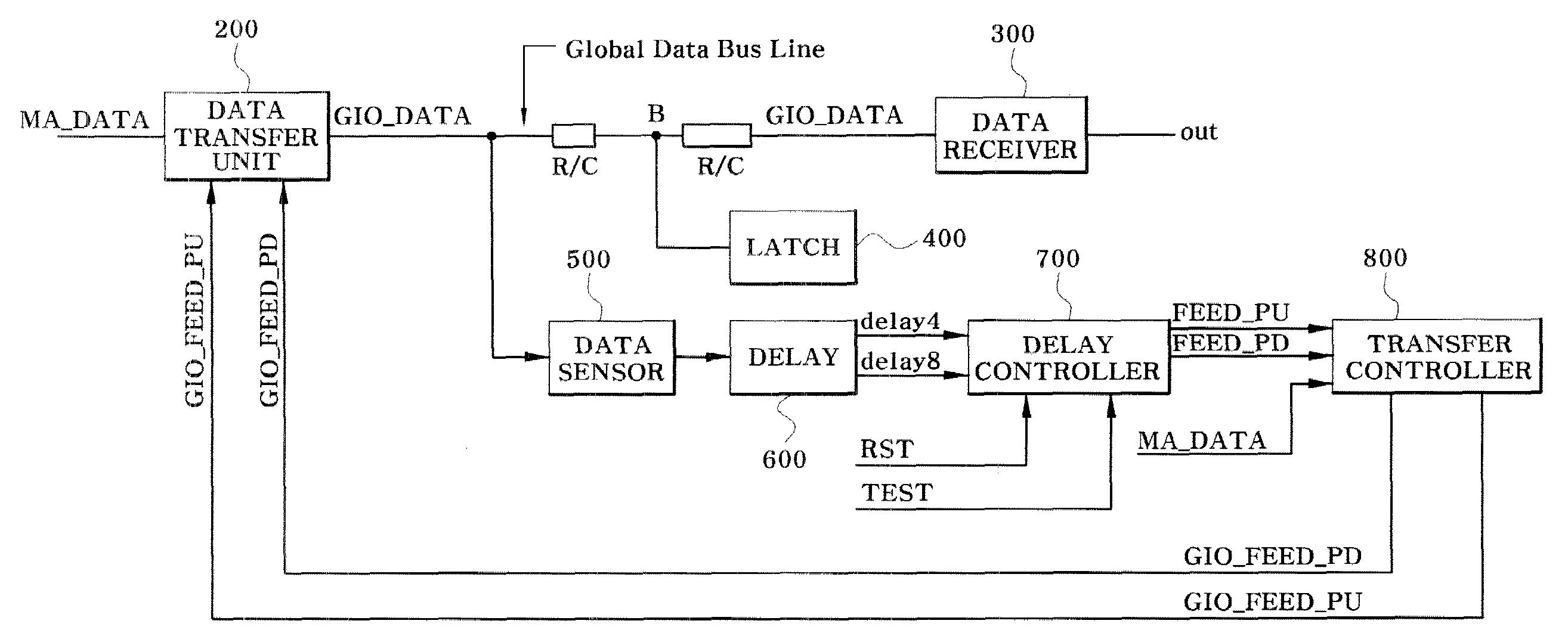

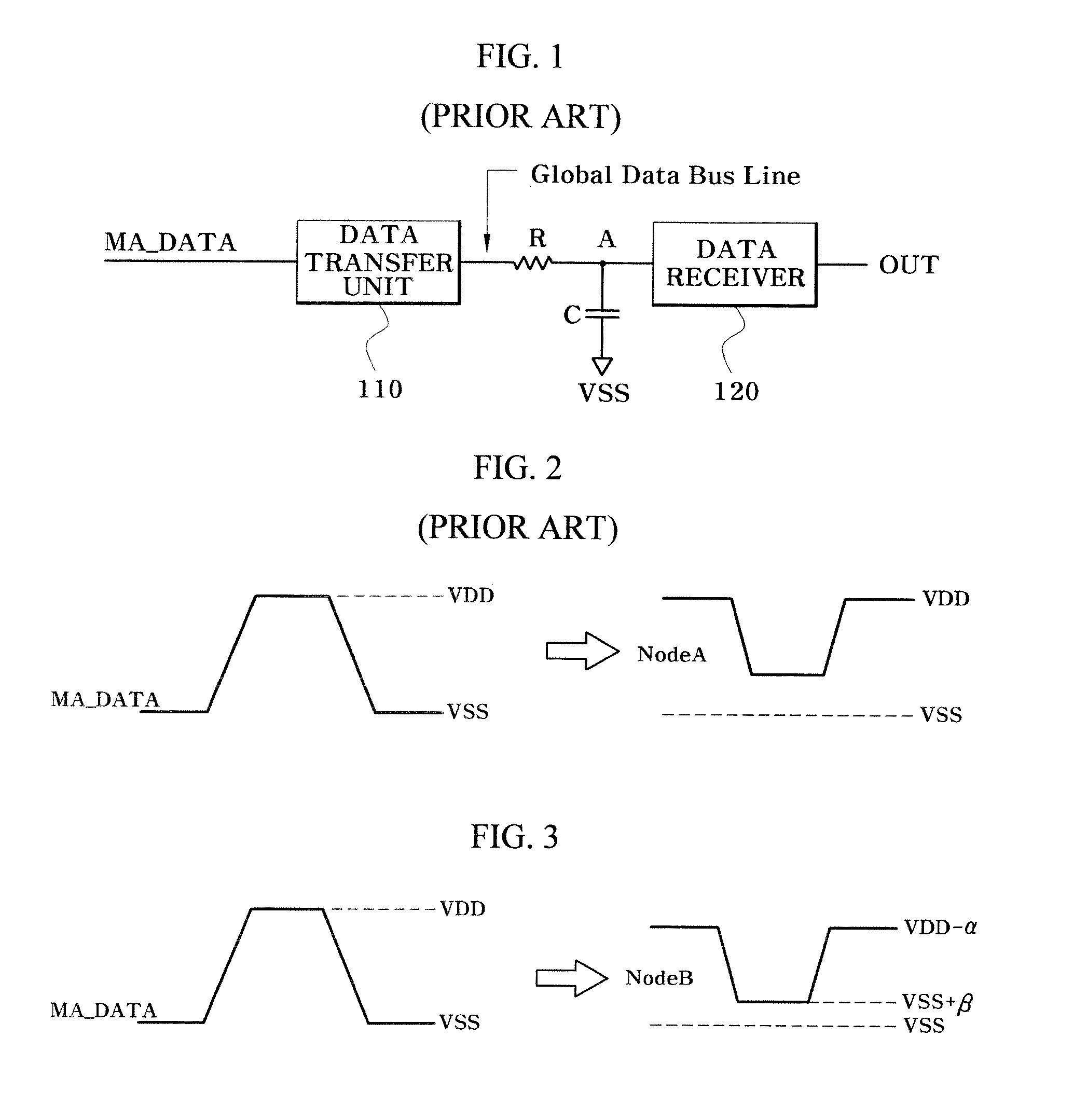

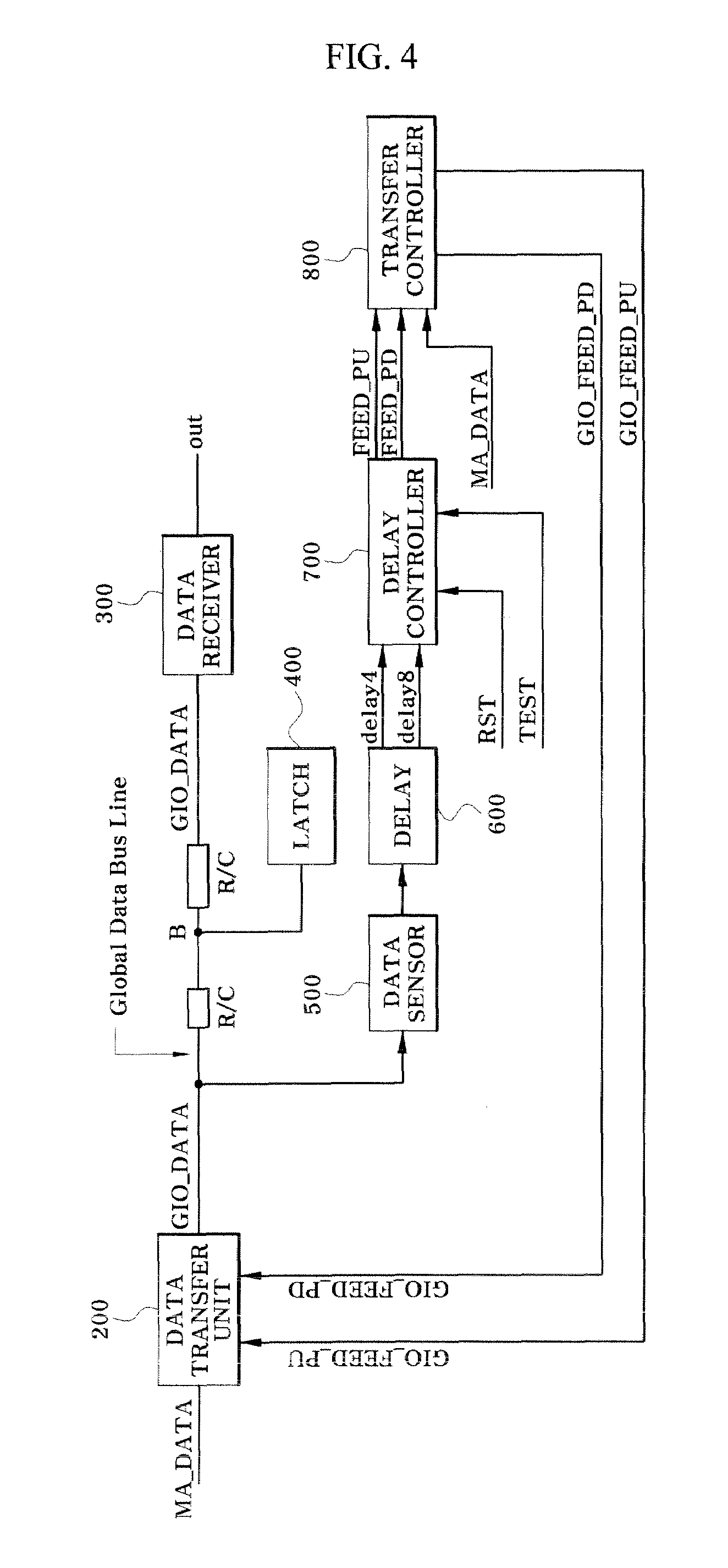

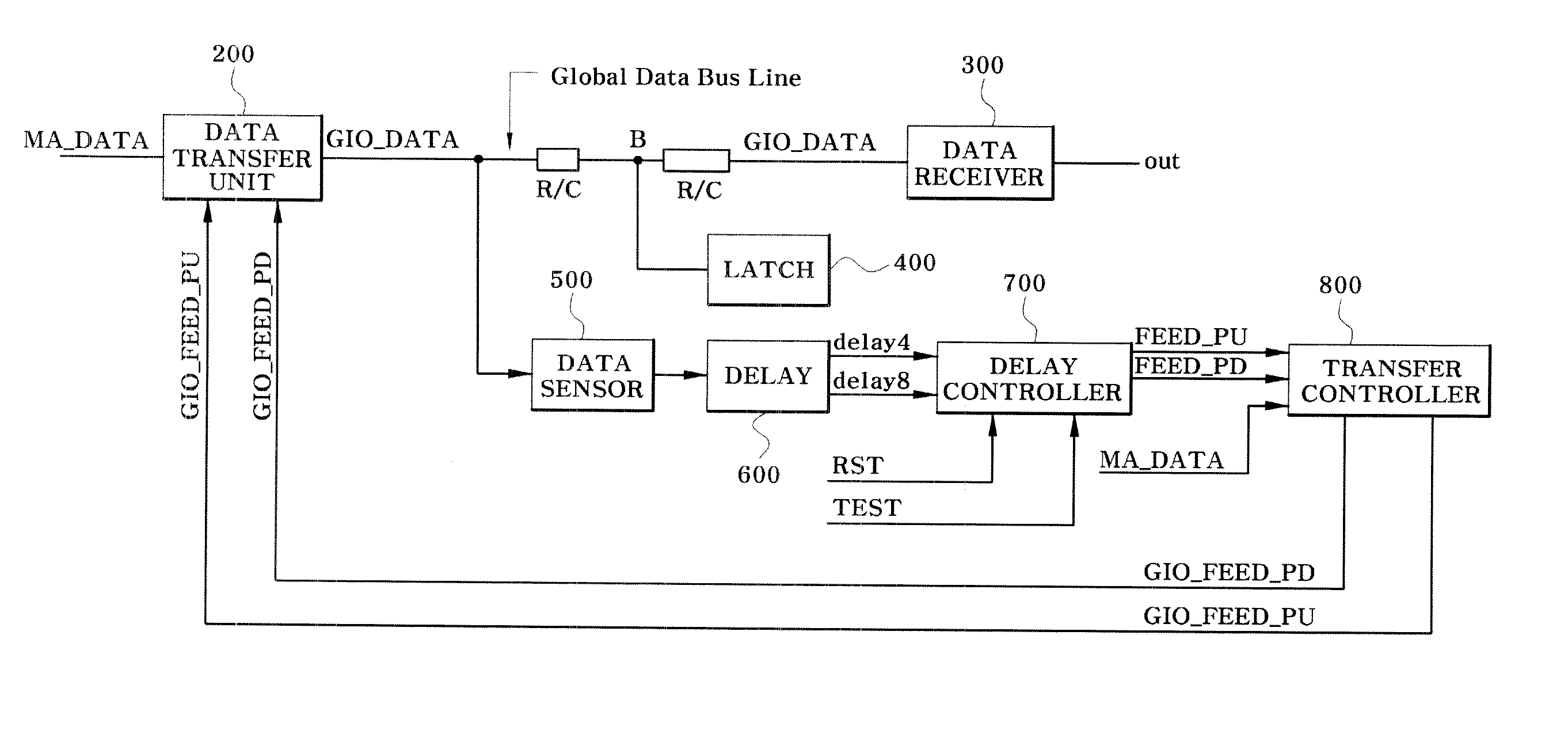

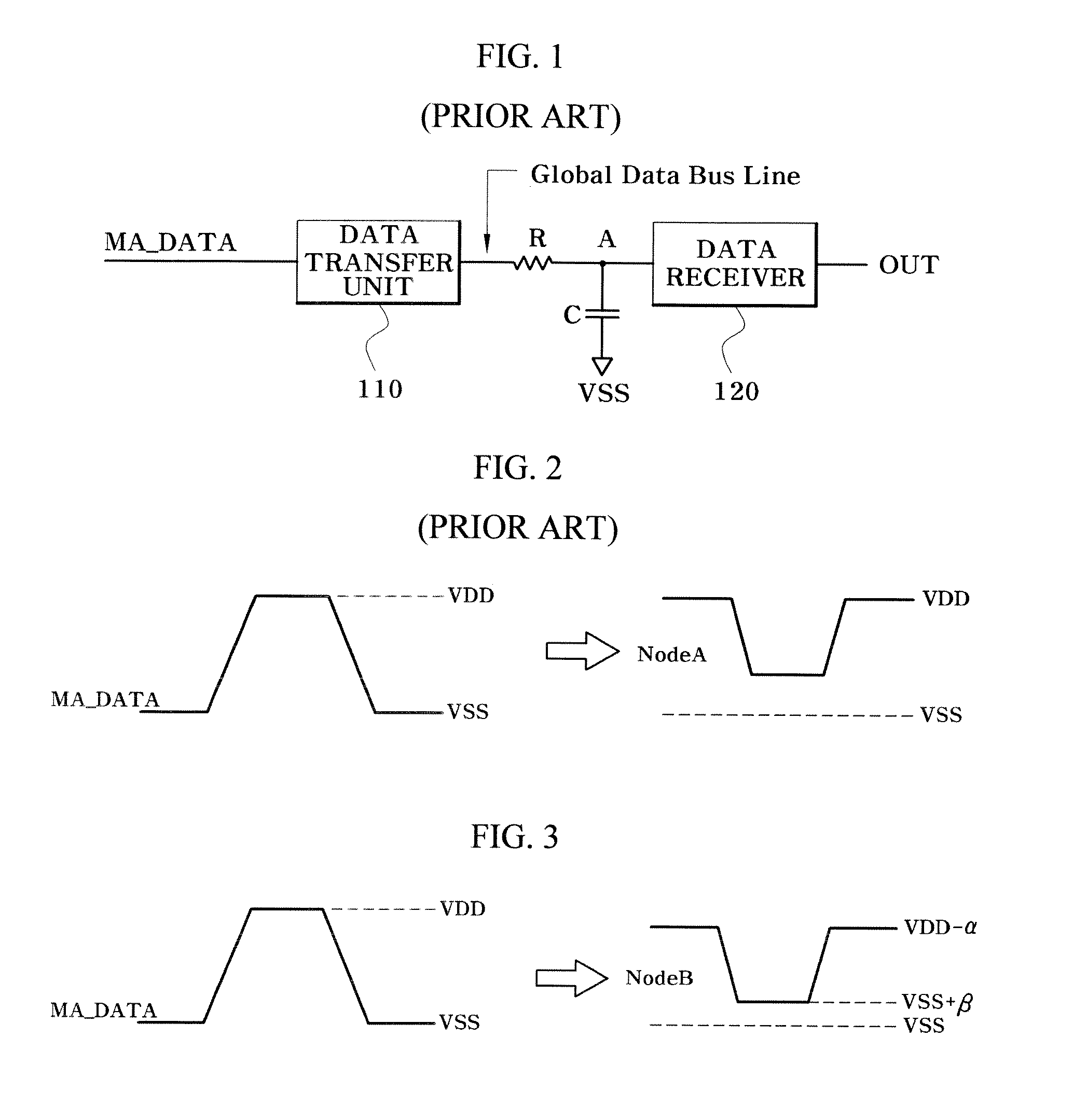

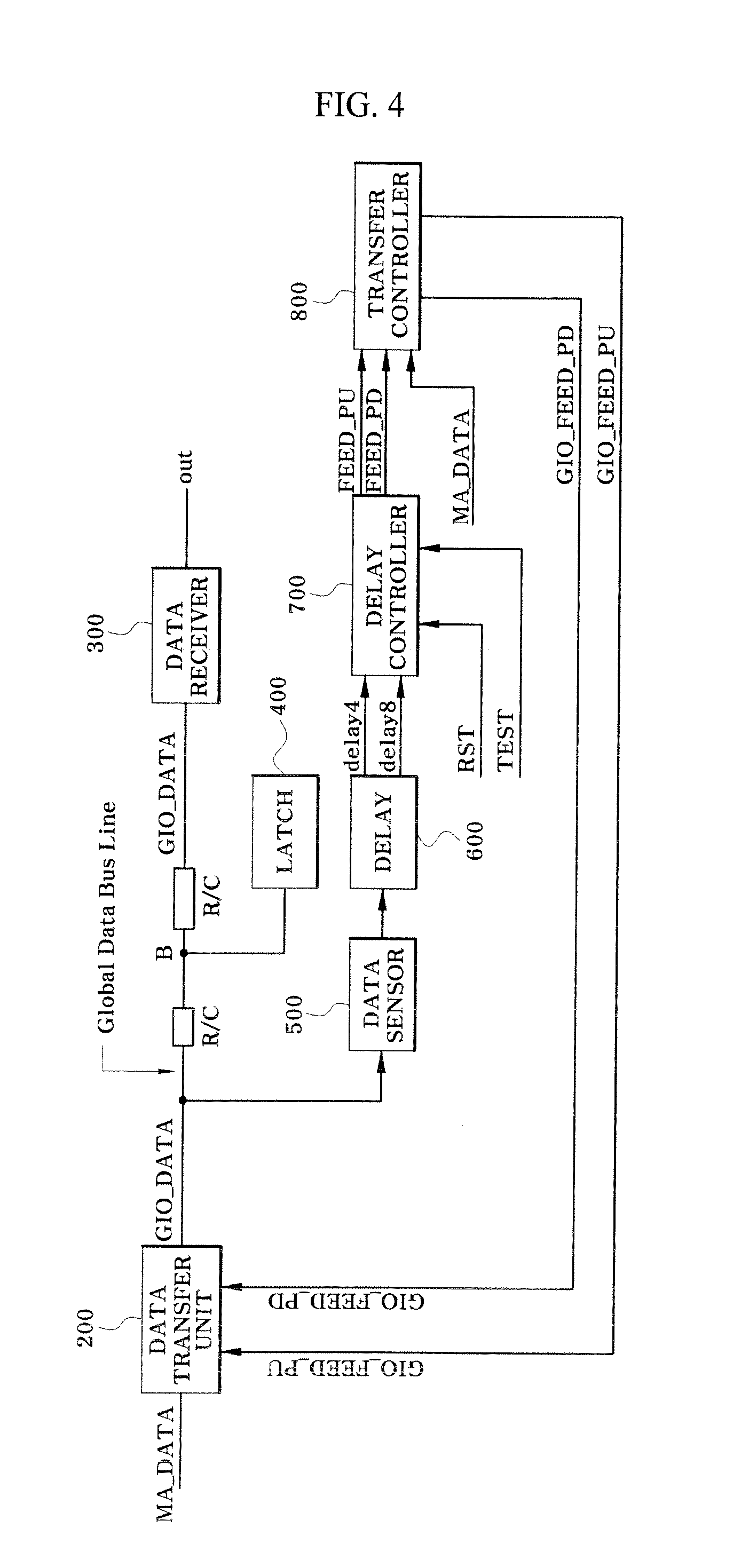

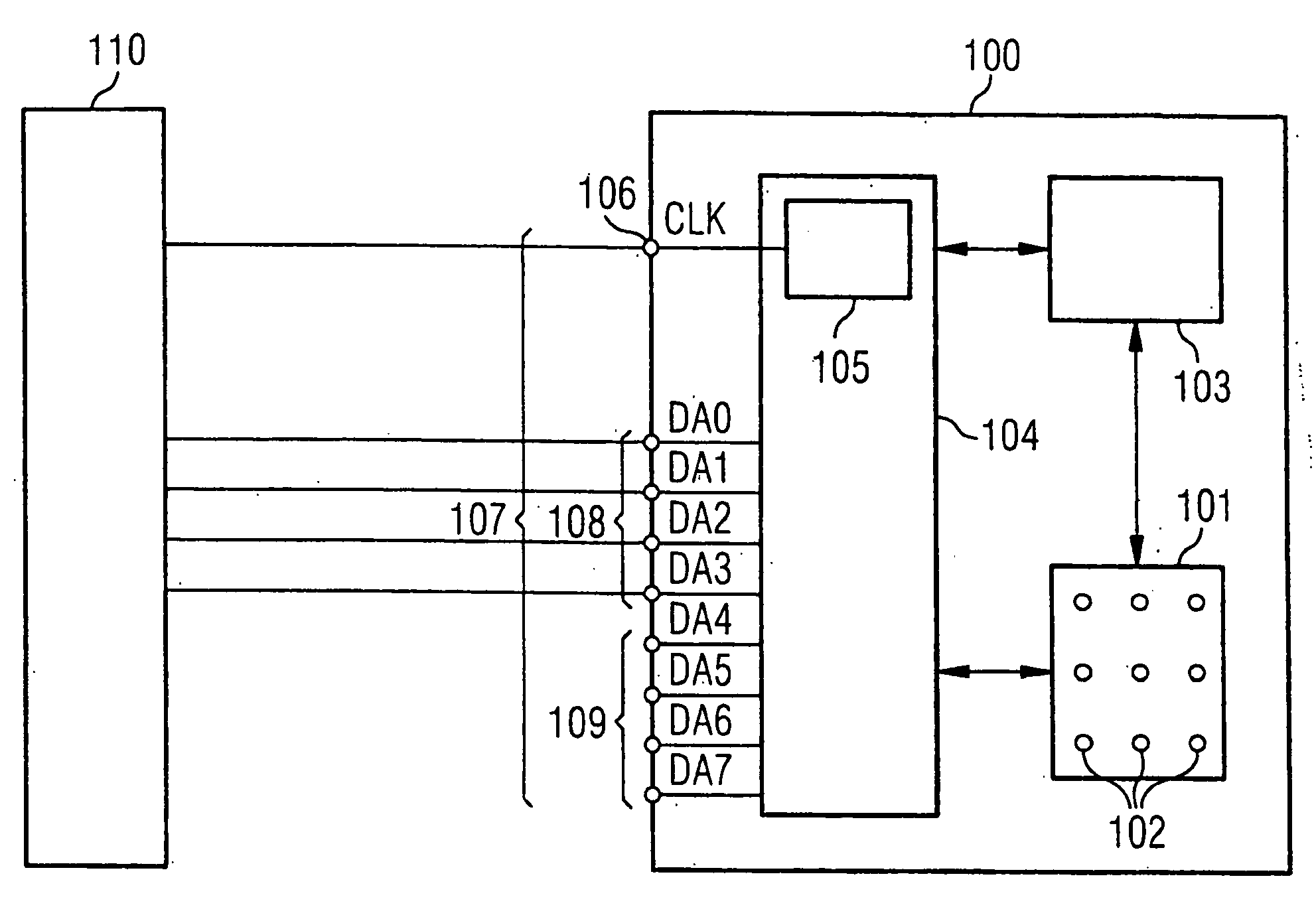

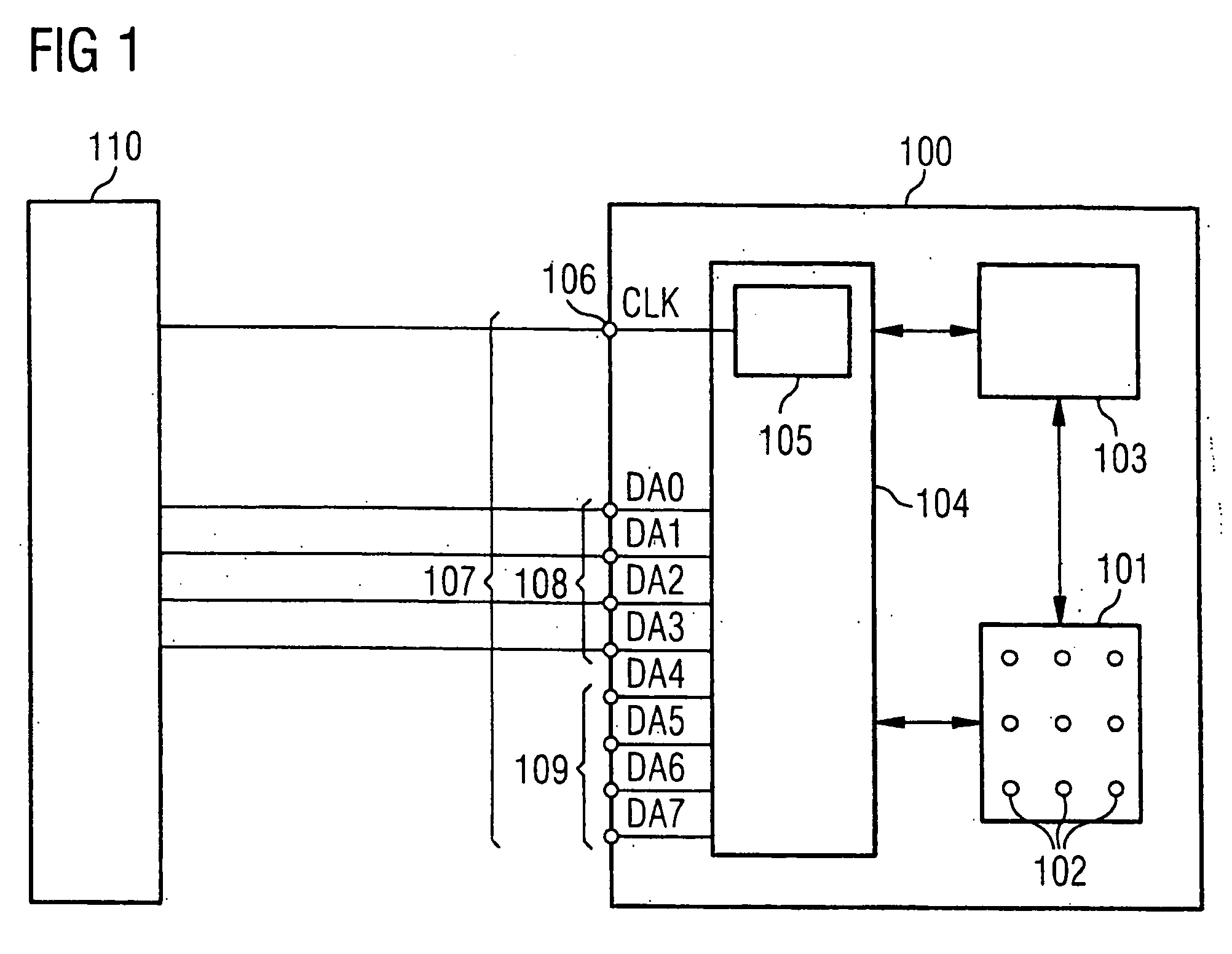

Semiconductor device

ActiveUS7423920B2Suppress generationImprove data transfer rateSolid-state devicesDigital storageAudio power amplifierControl signal

A semiconductor device is disclosed which increases the data transfer rate in transferring data output from an input / output sense amplifier via a global data bus line by reducing the swing width of the data placed on the global data bus line. The semiconductor device may include a data transfer unit which receives first data, and outputs second data obtained by driving the first data to a predetermined level to a data transfer line; a data receiver which receives the second data transferred via the data transfer line; a delay which outputs a plurality of delay signals respectively obtained by delaying the second data outputted from the data transfer unit by different delay periods; a delay controller which selects one of the delay signals in accordance with an operation mode of the semiconductor device, and outputs at least one adjustment signal for adjusting a driving period of the data transfer unit for the first data based on the delay period of the selected delay signal; and a transfer controller which receives the first data and the at least one adjustment signal, and outputs at least one transfer control signal for controlling the operation of the data transfer unit, based on the received first data and adjustment signal.

Owner:SK HYNIX INC

Downlink transmitter of LTE base station system and data processing method thereof

InactiveCN103428148AReduce transmission costsSave resourcesError preventionMulti-frequency code systemsTraffic capacityFast Fourier transform

The invention discloses a downlink transmitter of a long term evolution (LTE) base station system. The downlink transmitter comprises a base band unit (BBU) and a remote radio unit (RRU), wherein the BBU and the RRU are connected by an Ir ( interface between the RRU and the BBU). The BBU is used for carrying out bit-level processing and modulation processing on original data and sending the processed data to the RRU by the Ir; and the RRU including an inverse fast fourier transform (IFFT) / inverse discrete fourier transform (IDFT) module is used for receiving the data sent by the BBU through the Ir, carrying out IFFT or IDFT processing on the data and emitting the data. Correspondingly, the invention also discloses a data processing method of the downlink transmitter. The sampling rate and the data bit width are reduced. Therefore, the Ir downlink data transmission flow is effectively reduced, the cost of transmission from the BBU to the RRU is lowered, and the optical fiber resources laid at the Ir are saved; and thus an objective of saving of the equipment cost and the maintenance cost is achieved.

Owner:ZTE CORP

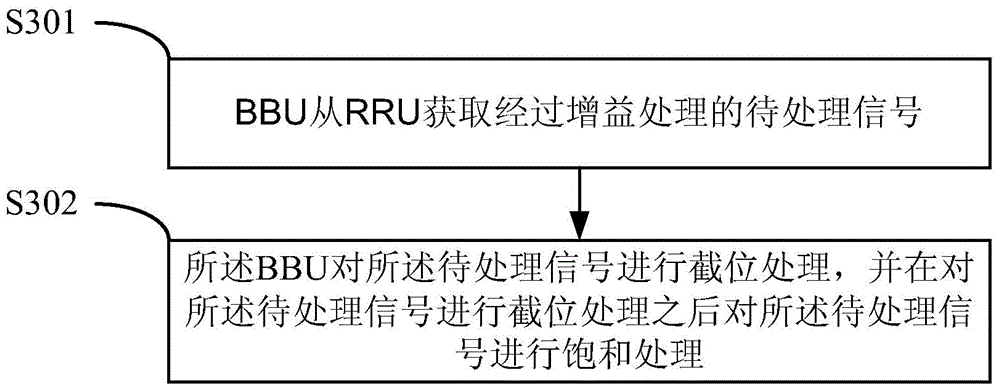

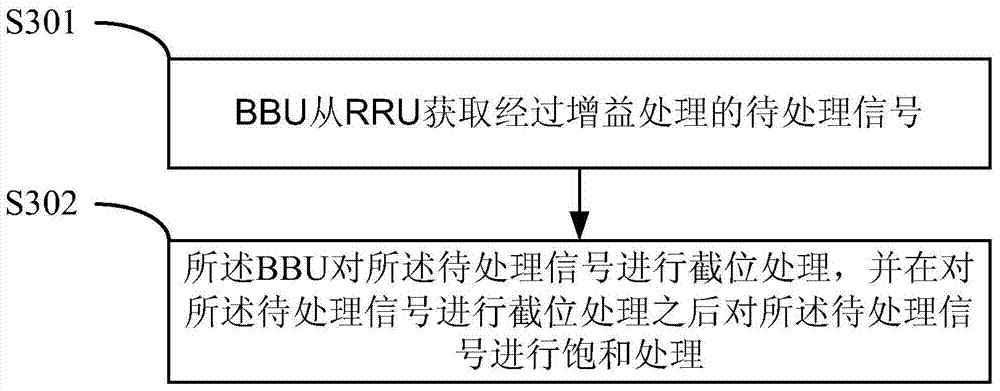

Signal processing method and device

ActiveCN104821861AAvoid quantization errorDoes not increase sensitivity to effectsError preventionBit slicingComputer science

The invention discloses a signal processing method. The method comprises the following steps: a BBU performing bit-slicing processing on a to-be-processed signal after acquiring the to-be-processed signal after gain processing from a RRU, and performing saturation processing on the to-be-processed signal after performing the bit-slicing processing, thereby avoiding quantization error of a signal caused by transmission between boards, meeting the requirement of a system index while reducing data bit width transmitted between the boards, and guaranteeing that the bit-slicing error cannot increase the influence of the quantization error to the sensitivity of a receiver. And meanwhile, the method further comprises the step of adjusting linkage gain according to average power of a signal acquired by an ADC so as to prevent signal from oversaturating in the premise of guaranteeing the precision of the sensitivity of the receiver.

Owner:DATANG MOBILE COMM EQUIP CO LTD

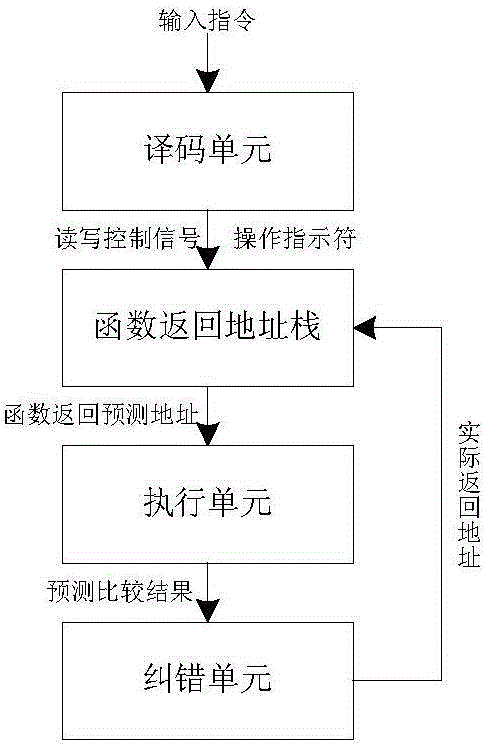

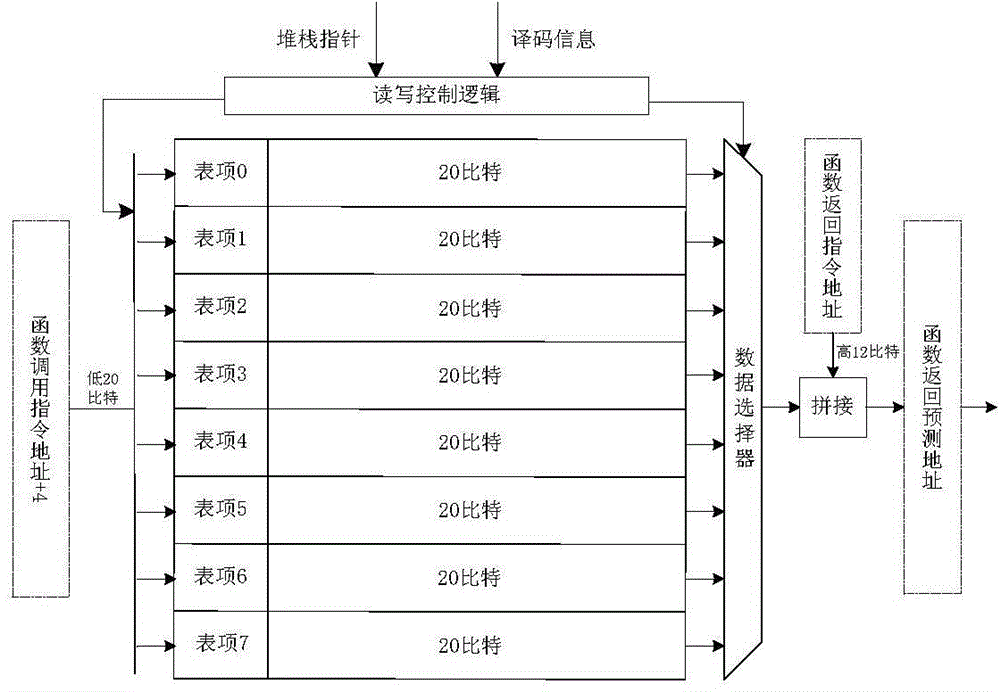

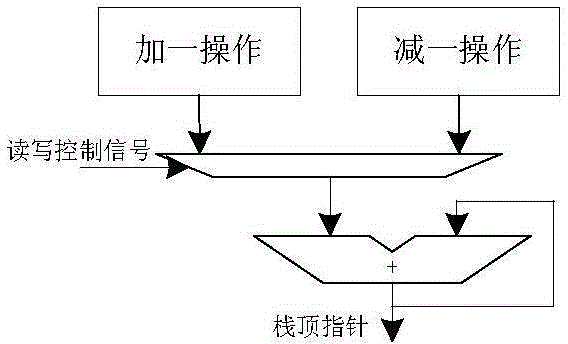

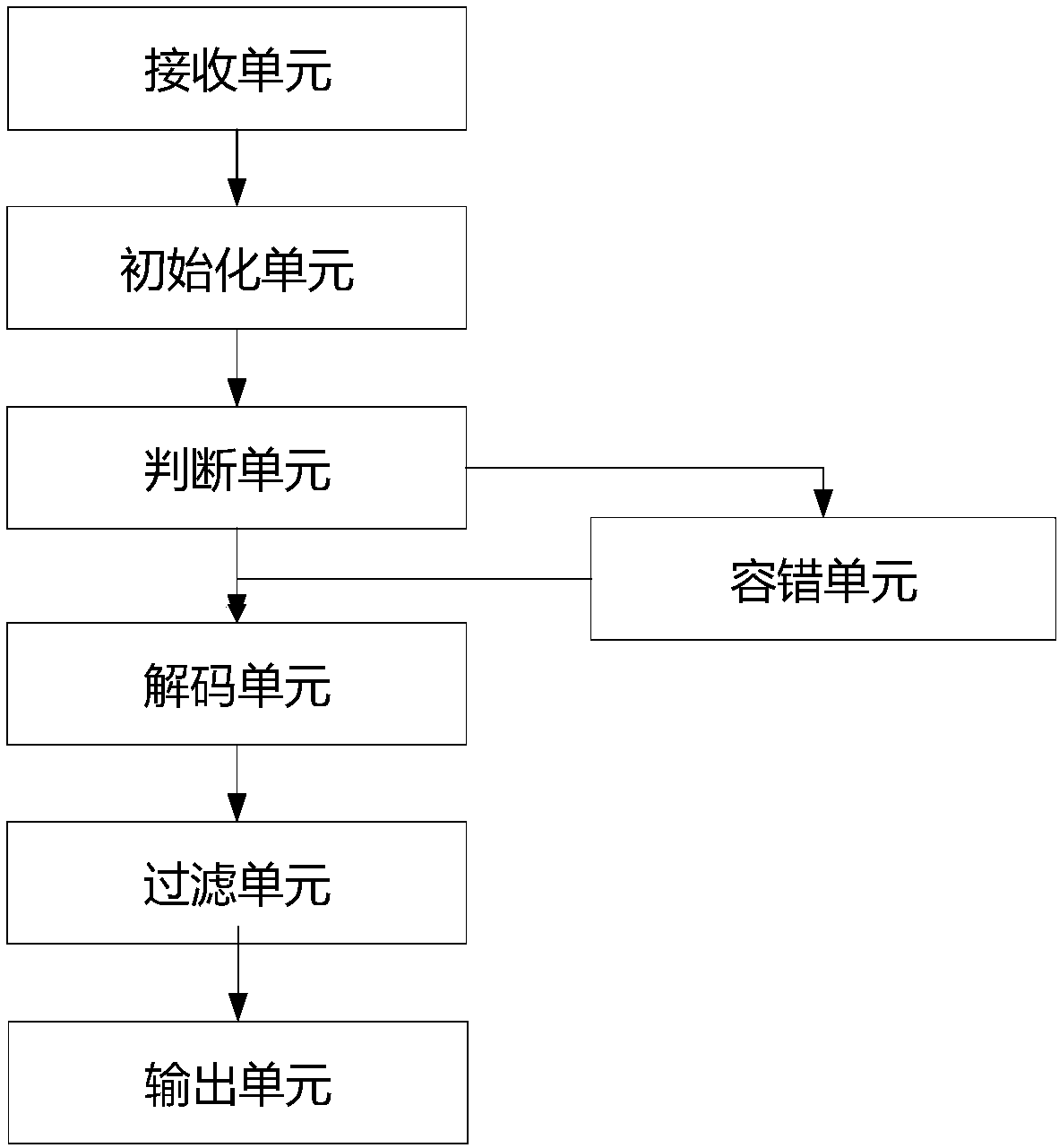

Device and method for predicting function return address

InactiveCN104572024ALow costImprove processor performanceProgram controlMemory systemsOperating systemReturn address stack

A device for predicting a function return address comprises an instruction decoding unit, a function return address stack, an execution unit and an error correction unit. The instruction decoding unit is used for decoding an input instruction to generate an operation indicator; the function return address stack comprises S table entries and is used for performing return address prediction on a function return instruction to generate a predicated address A and a corresponding table entry index X; the execution unit is used for receiving the operation indicator of the instruction decoding unit and the predicated address A and the table entry index X of the function return address stack, judging whether the address A is predicated correctly or not when the operation indicator indicates the function return instruction, and generating prediction correctness information and an actual skip address; the error correction unit is used for receiving output of the execution unit, and correcting content directed by the table entry index X in the function return address stack by the actual address B when the function return address is predicated mistakenly. The invention further provides a method for predicting the function return address. By the device and the method, cost of the function return address stack is reduced effectively, and processor performance is improved.

Owner:C SKY MICROSYST CO LTD

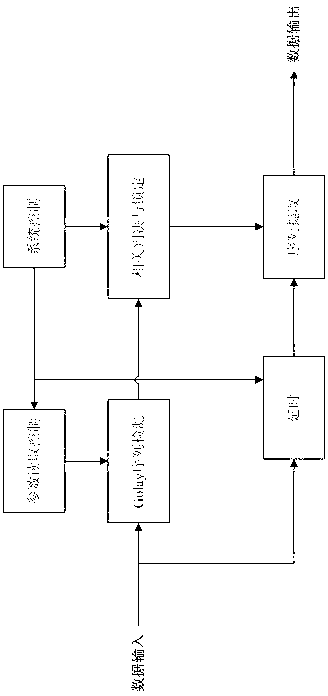

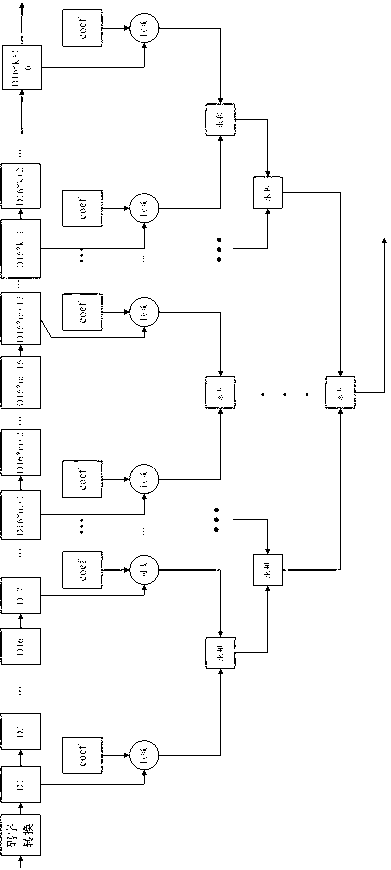

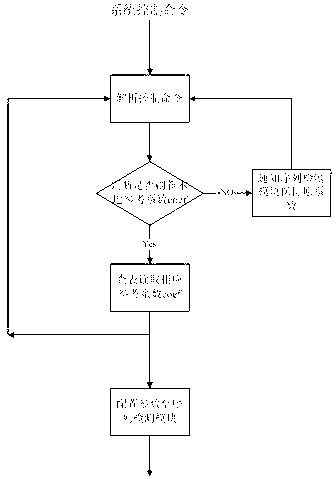

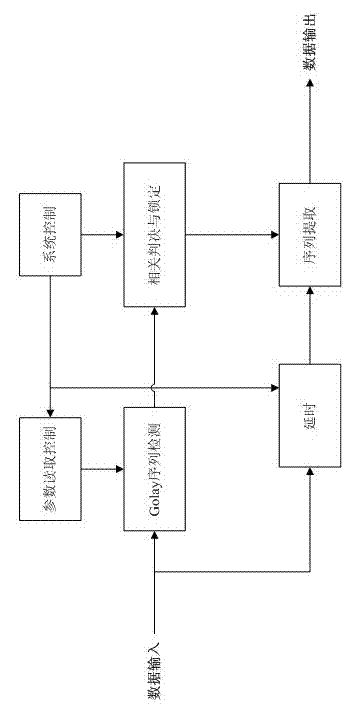

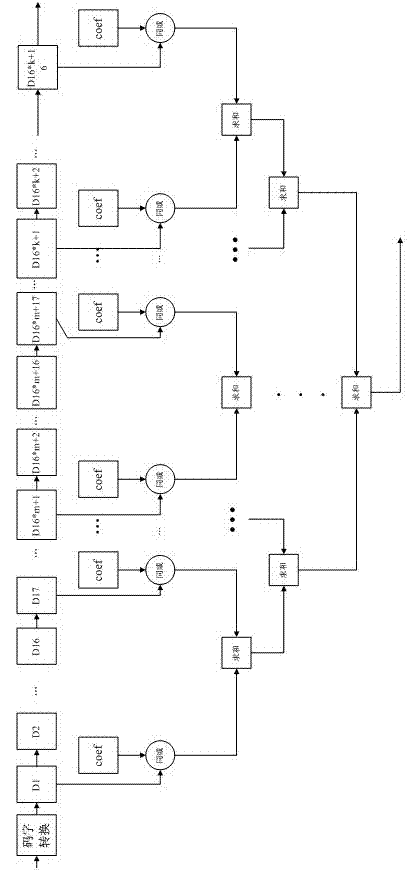

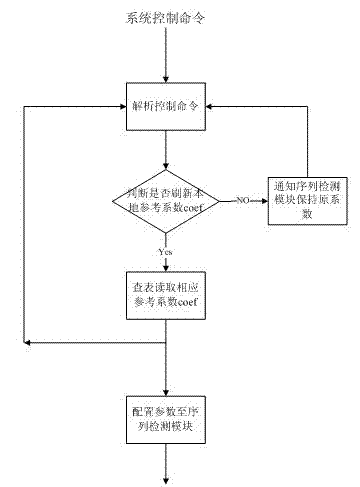

Field programmable gate array (FPGA) based method for achieving synchronous detection of oversampling Golay sequence

ActiveCN103023529AExcellent autocorrelation performanceReduce occupancyTransmissionMultiplexingShift register

The invention relates to a field programmable gate array (FPGA) based method for achieving synchronous detection of an oversampling Golay sequence. A hardware system established on the basis of FPGA comprises a Golay sequence detector module, a parameter read control module, a system control module, a related judgement and locking module, a time delay module and a sequence extraction module, the Golay sequence is used as a synchronous sequence, the possibility of false synchronization and false loss of synchronism can be reduced, a detecting module uses a special not exclusive or algorithm, 50% of shifting registers occupied by a slippage correlation operation can be freed, by means of the parameter read control module, multiplexing of correlation operation of the Golay sequence with various lengths and parameters is achieved, similarly, FPGA on-chip resources occupied by a synchronizing system are reduced, the sequence detection operation interval can be flexibly adjusted by the system according to different oversampling ratios, and the synchronous detection supporting 1 to 16 times oversampling is achieved.

Owner:TOEC TECH

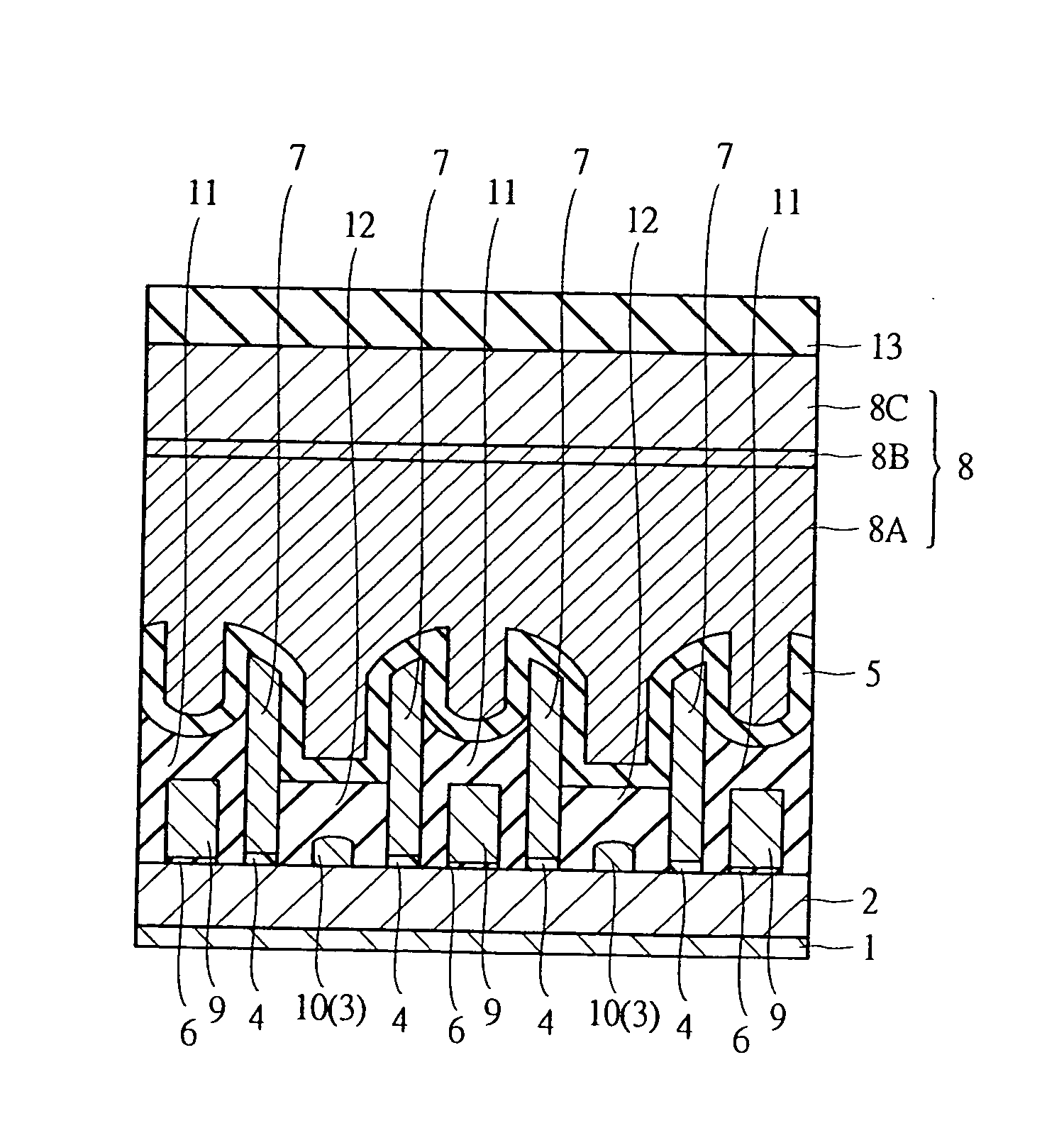

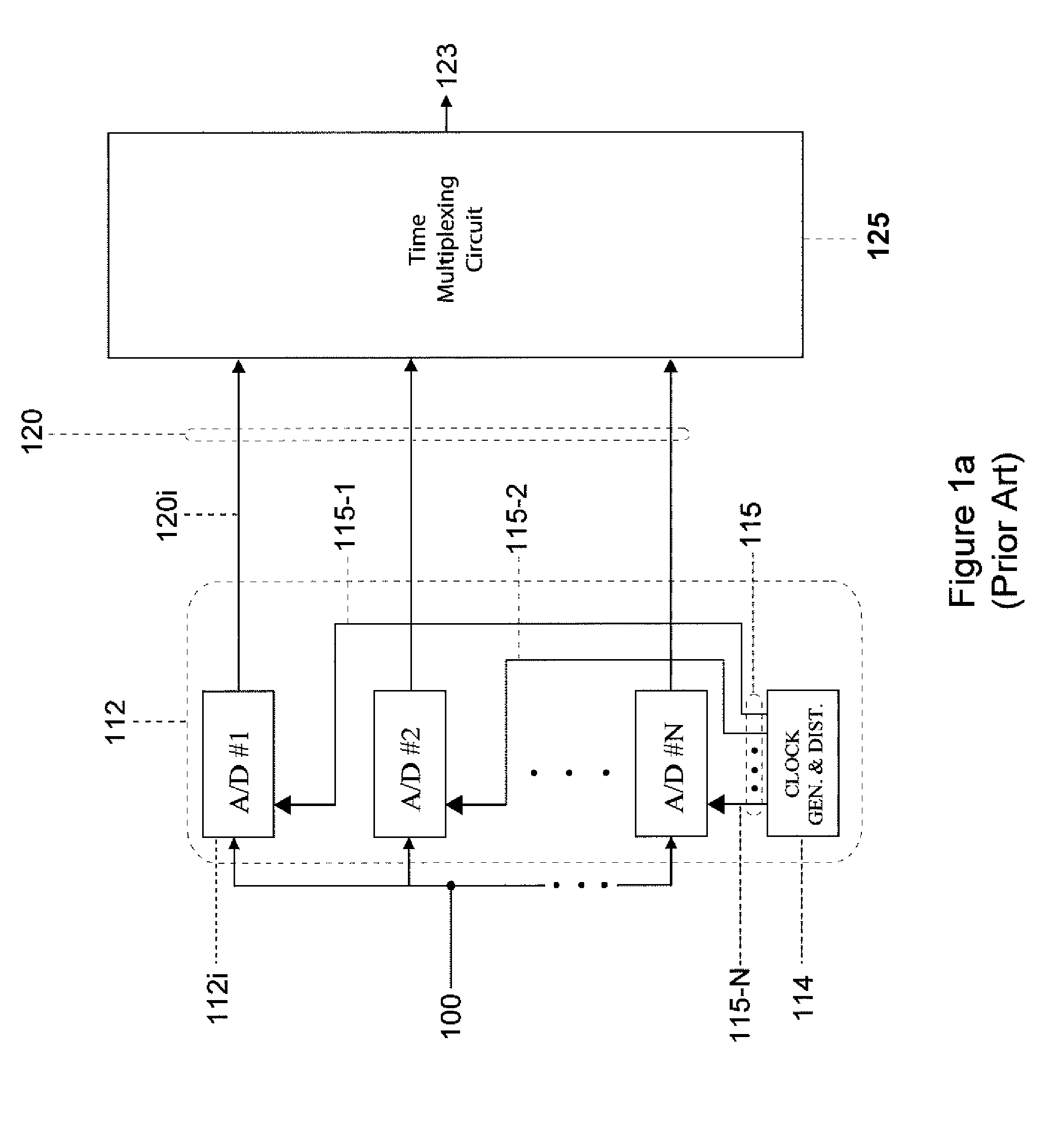

Semiconductor device and method for producing the same

InactiveUS20070205440A1Reduced Junction Leakage CurrentImprove punch-through enduranceTransistorSolid-state devicesInsulation layerDevice material

Owner:RENESAS TECH CORP

Enhanced time-interleaved a/d conversion using compression

InactiveUS20090201181A1Improve efficiencyReduce data widthAnalogue/digital conversionTransmissionBinary multiplierAnalog signal

Compression of signal samples output from a parallel, time-interleaved analog to digital converter (TIADC) for a baseband signal, includes calculating first or higher order differences of consecutive signal samples followed by lossless or lossy encoding of the difference samples to produce compressed samples. Compression of a TIADC output signal with a nonzero center frequency, includes calculating sums or differences of pairs of signal samples separated by an appropriate number of sampling intervals followed by lossless or lossy encoding. The sums or differences of the signal samples have lower magnitudes than the original samples, allowing more efficient compression. Lossy compression alternatives produce compressed data with a fixed bit rate or with a fixed quality in the decompressed samples. Alternatives for lossy compression include attenuating the analog signal before sampling by the TIADC, applying bit shifters or multipliers after sampling to reduce the magnitudes of the signal samples, and lossy encoding.

Owner:ALTERA CORP

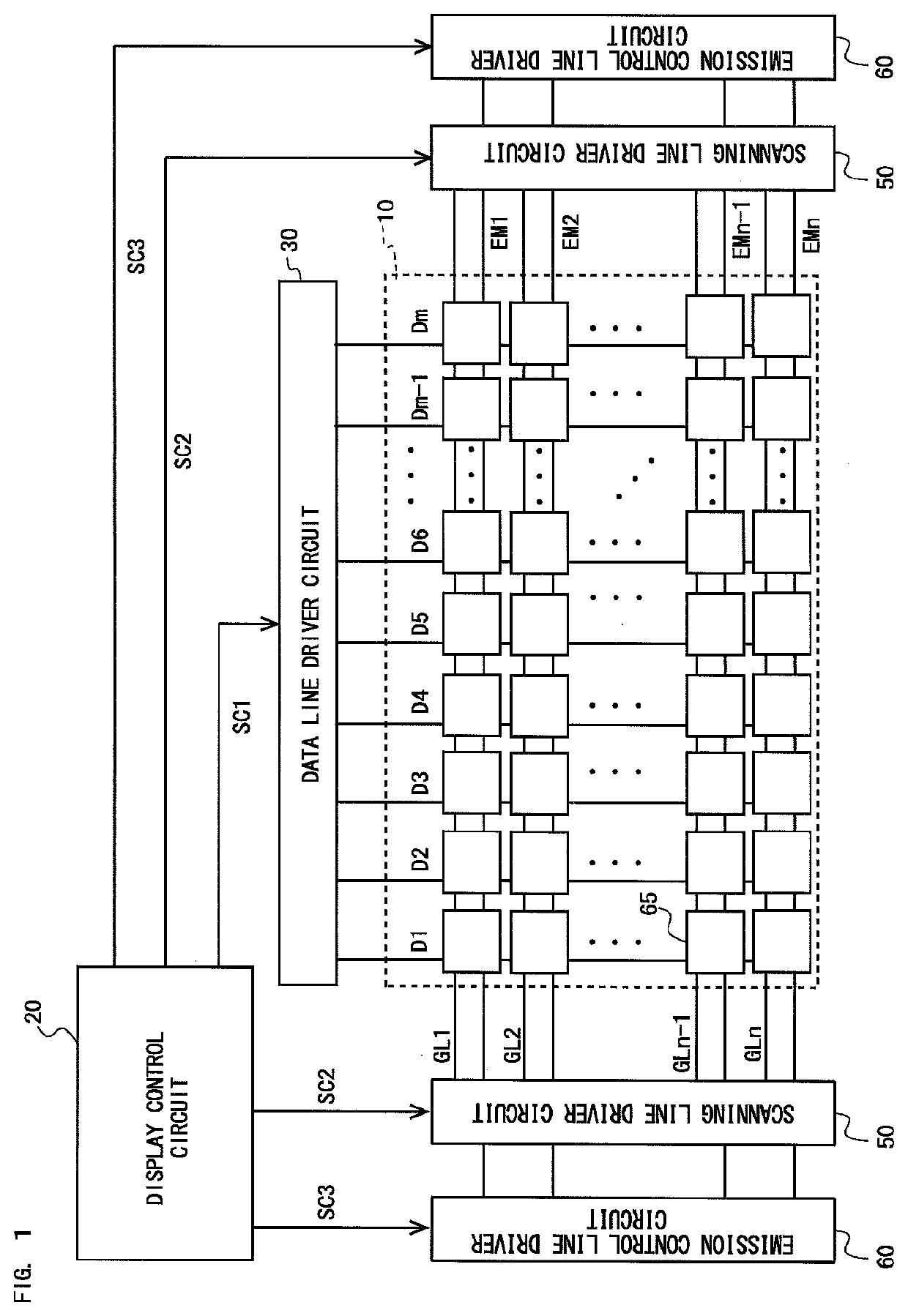

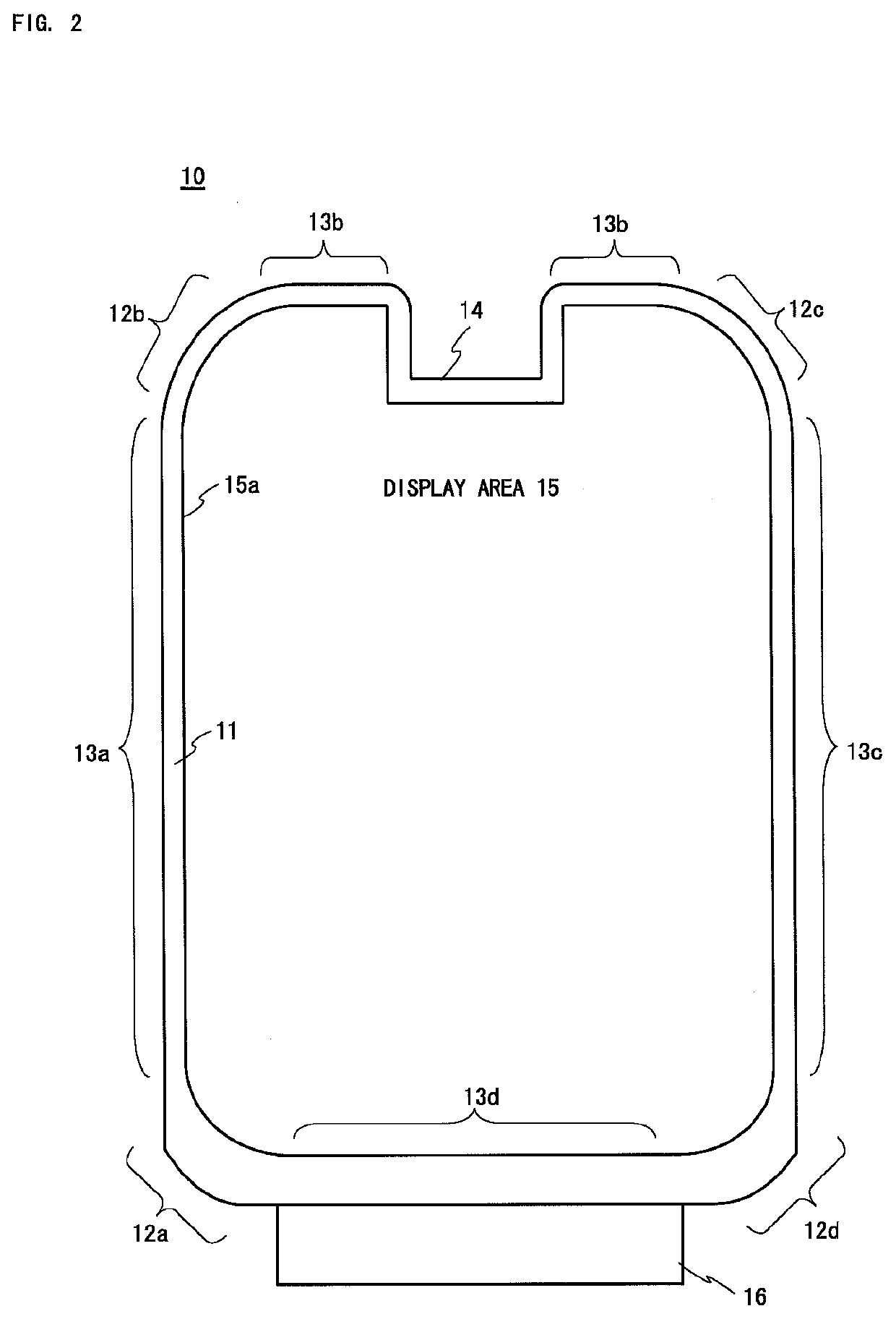

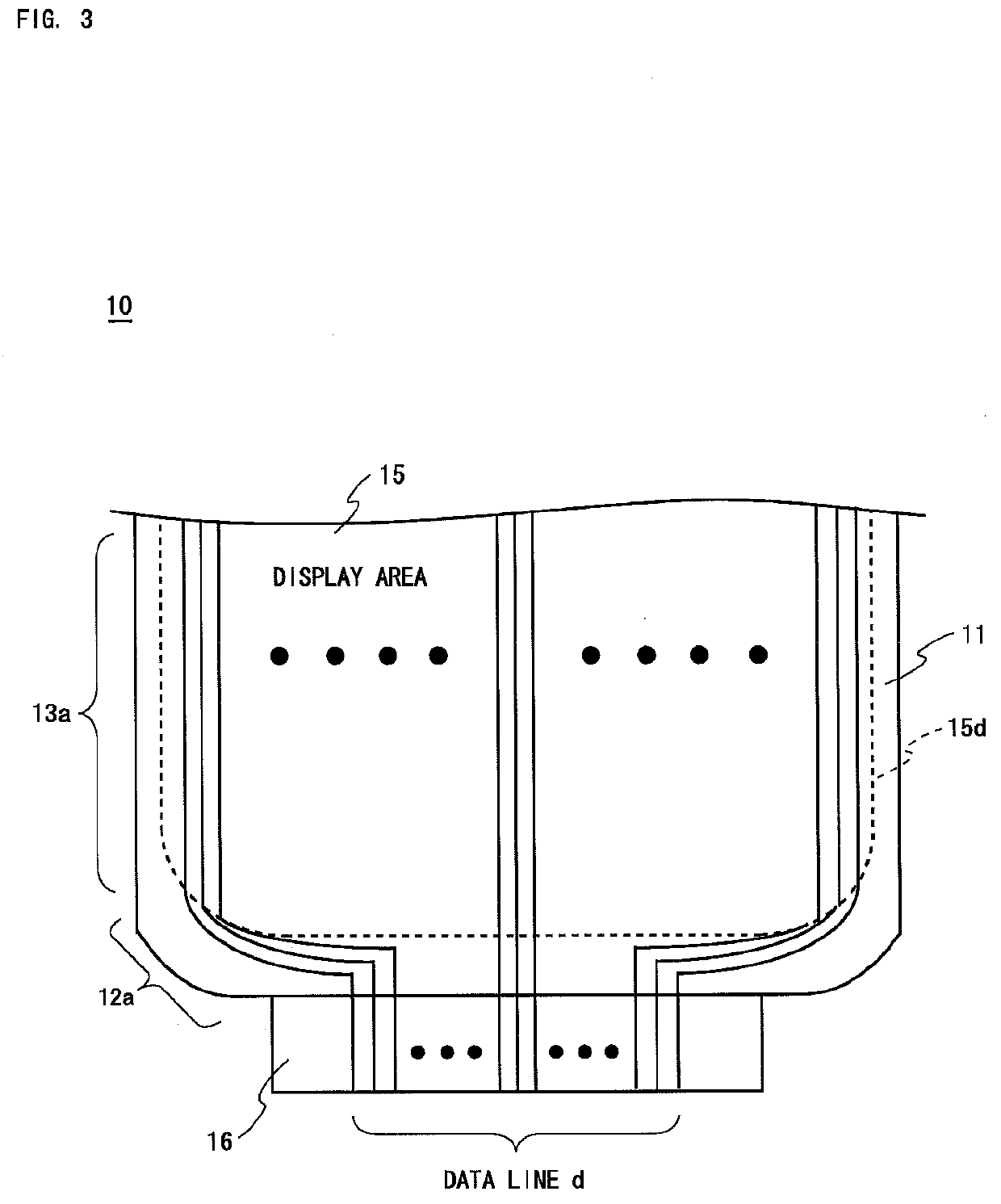

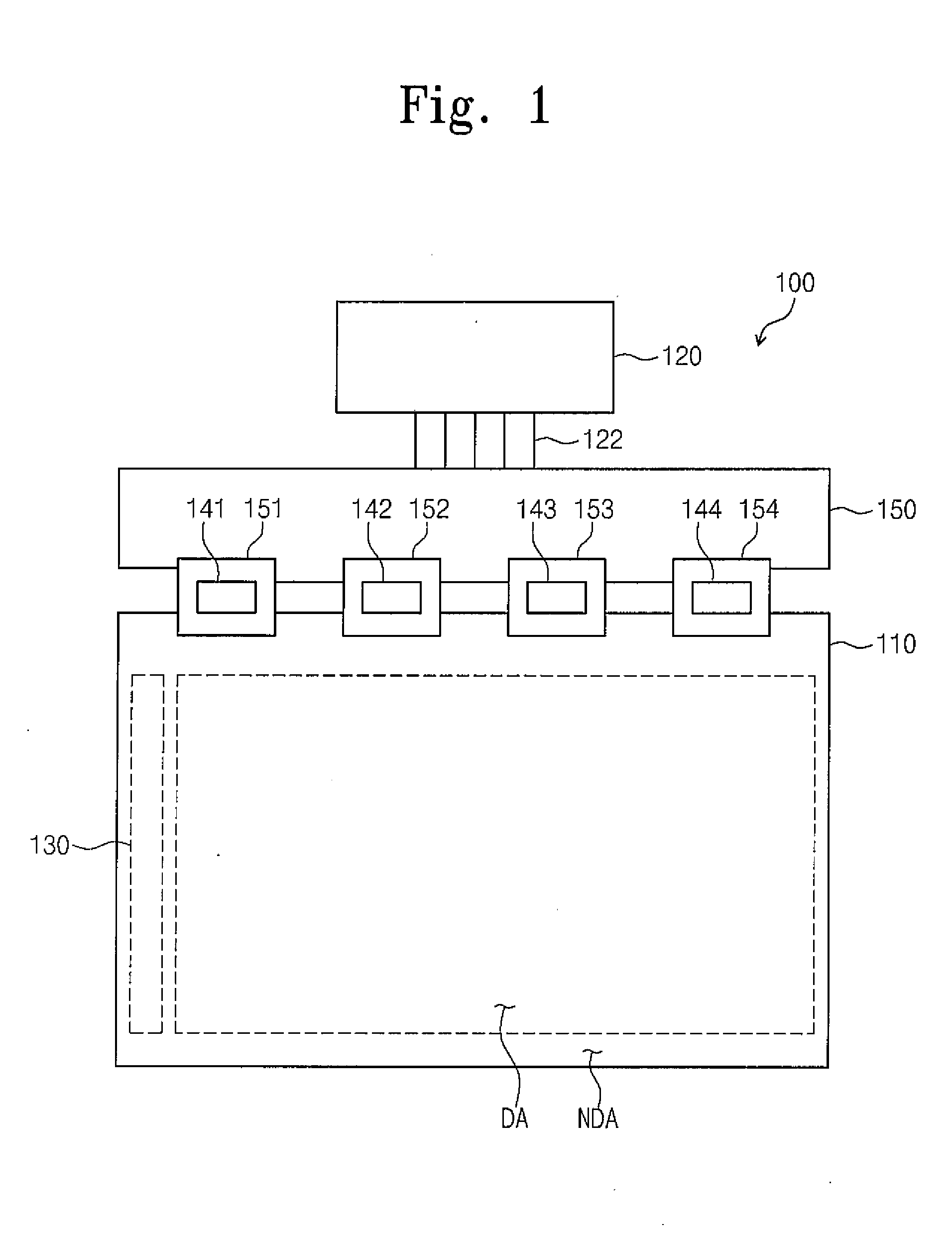

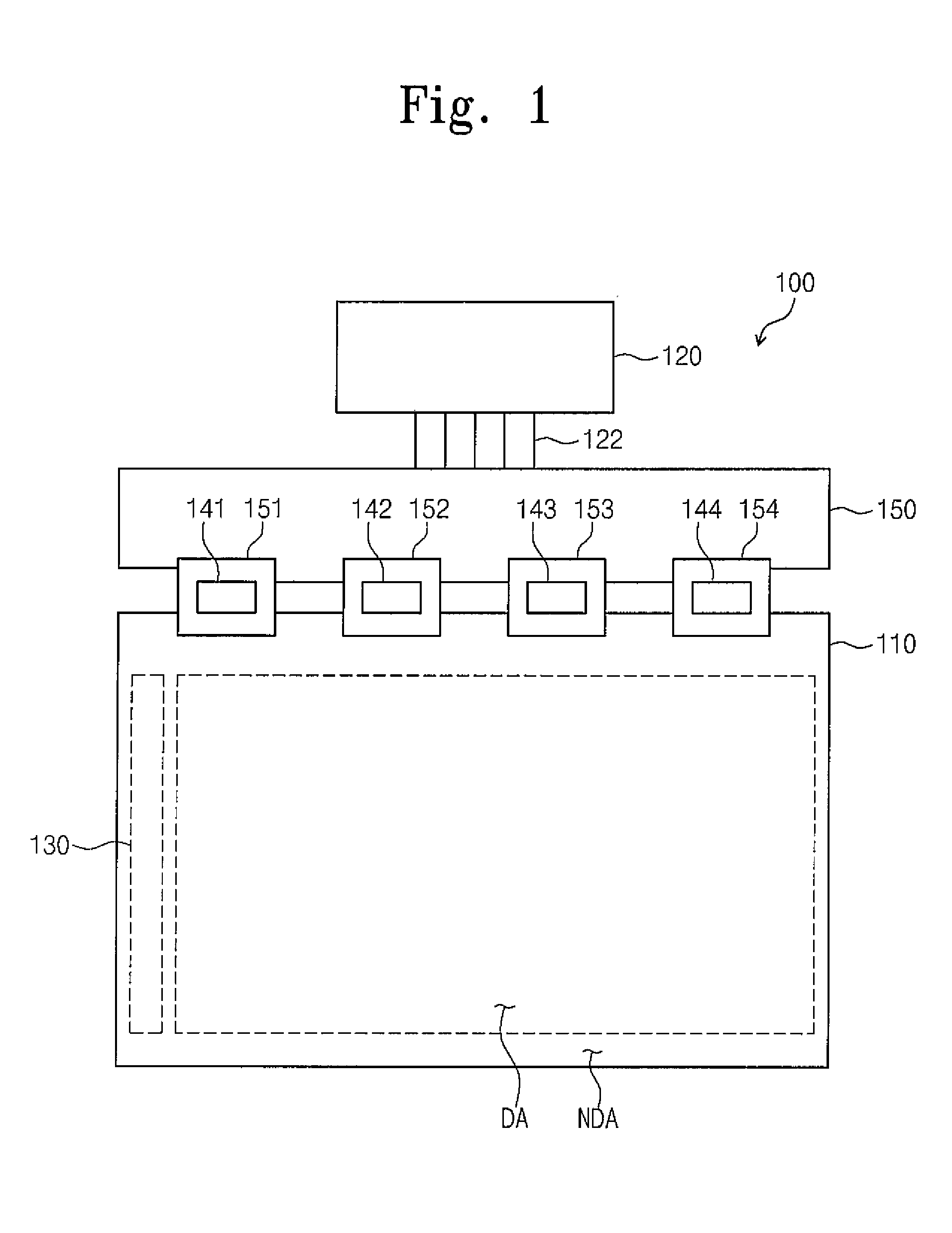

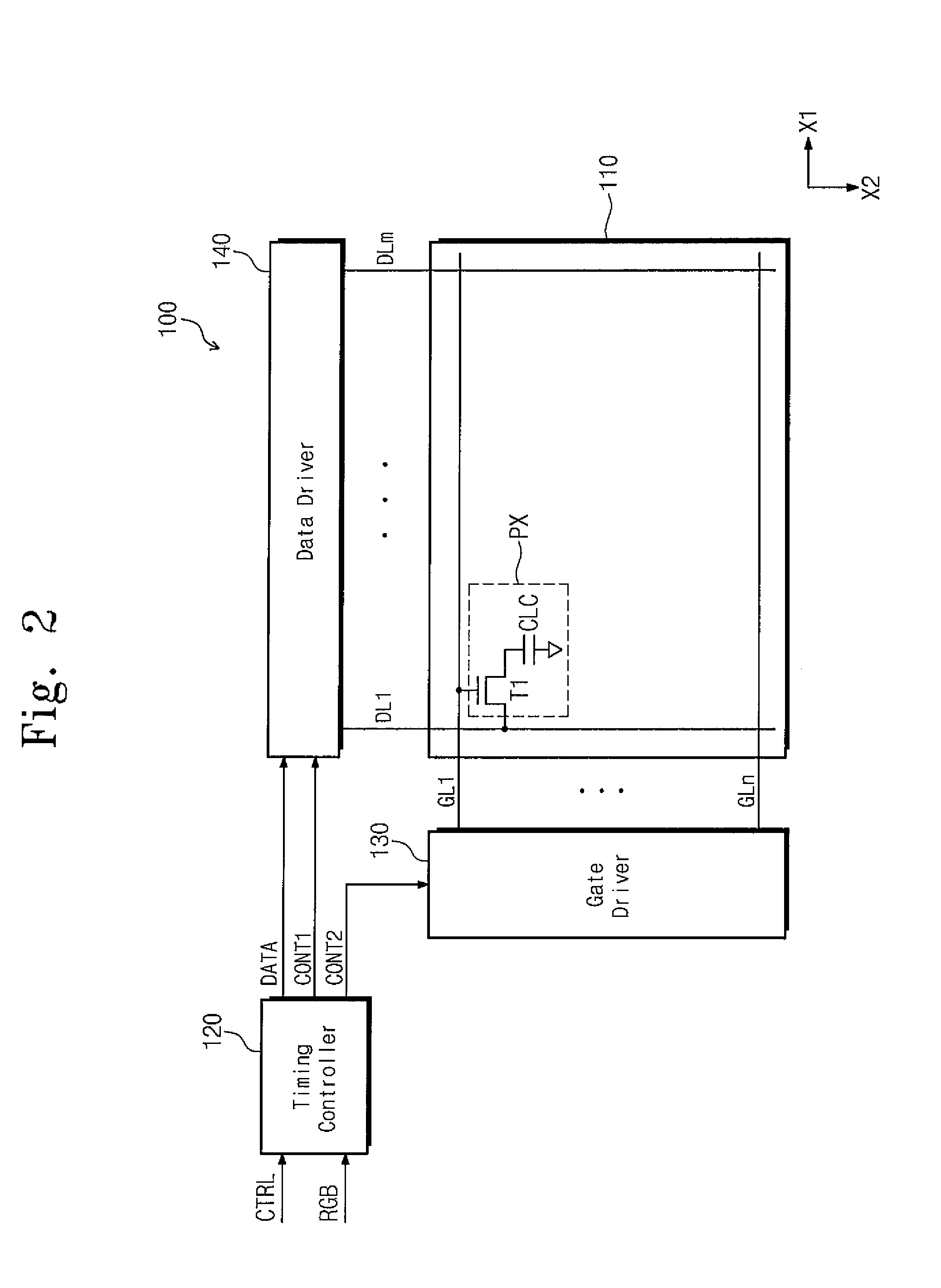

Display device

PendingUS20210048699A1Data lineDecrease widthStatic indicating devicesSolid-state devicesLine segmentEngineering

Provided is a display device including a display panel which allows a curvature portion thereof to be narrowed near a terminal portion even when circuit blocks are arranged in the curvature portion.For a data line in the form of a polyline consisting of a plurality of short straight line segments in a first curvature portion 12a of a display panel 10, as the distance from a terminal portion 16 increases, the slant angle of each straight line segment increases, the number of data lines d decreases, and hence the width of a data line area decreases. Accordingly, the number of unit circuit blocks 70 in a parallel circuit block 80 disposed in a circuit area can be increased by widening the circuit area in proportion to the decrease in the width of the data line area.

Owner:SHARP KK

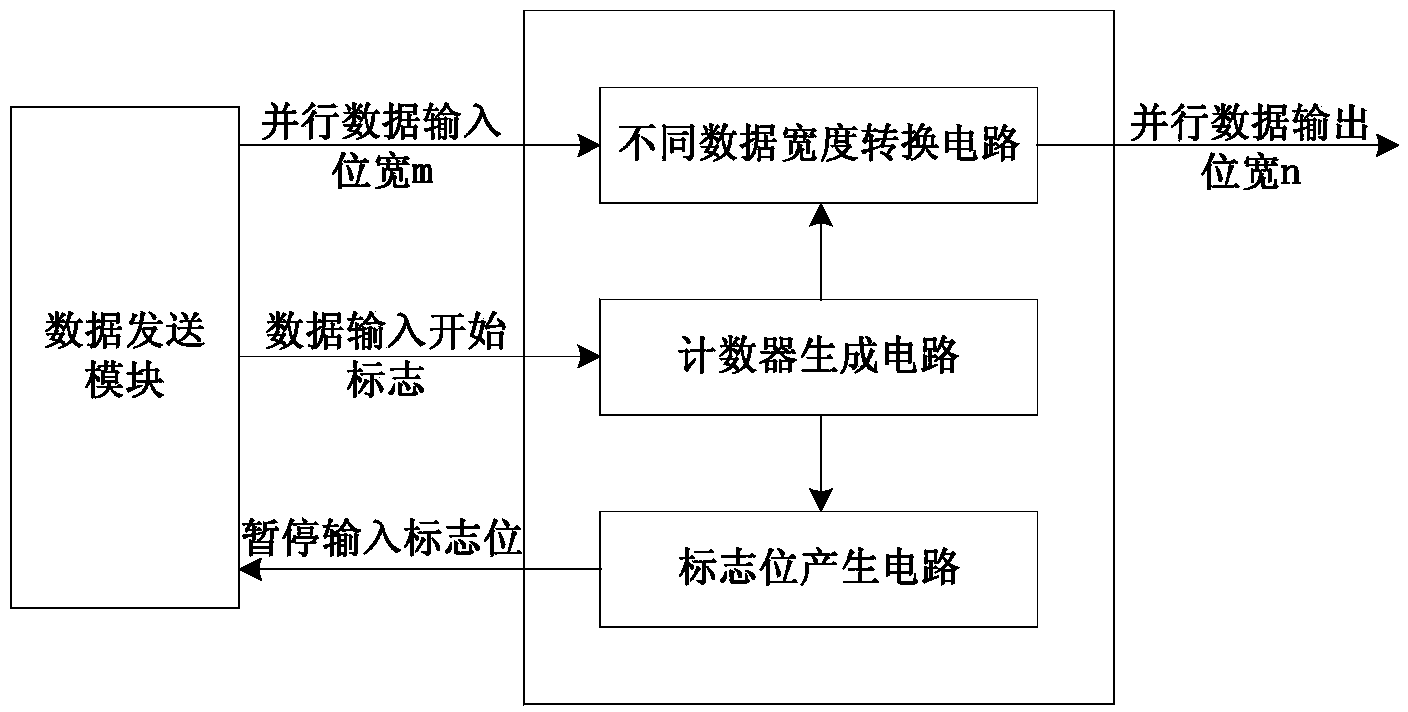

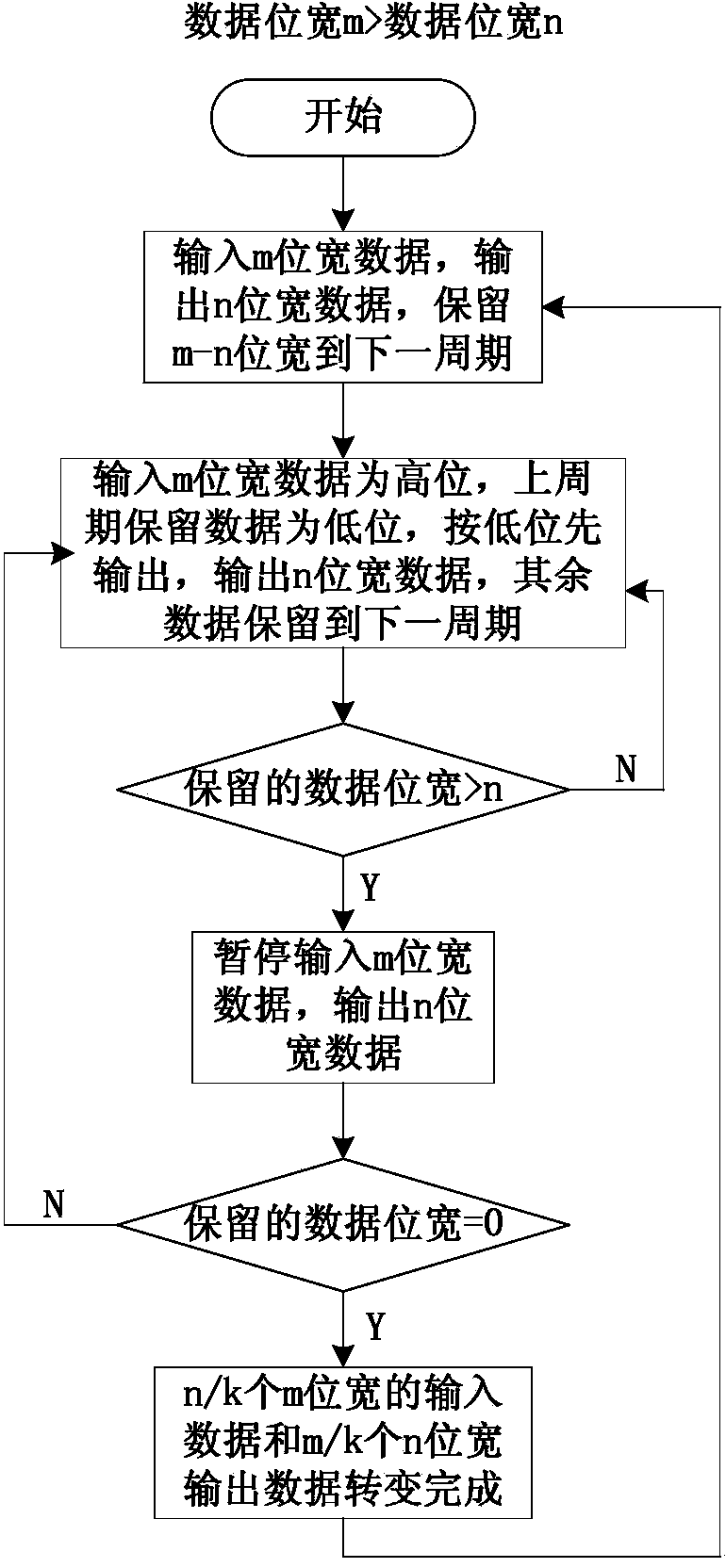

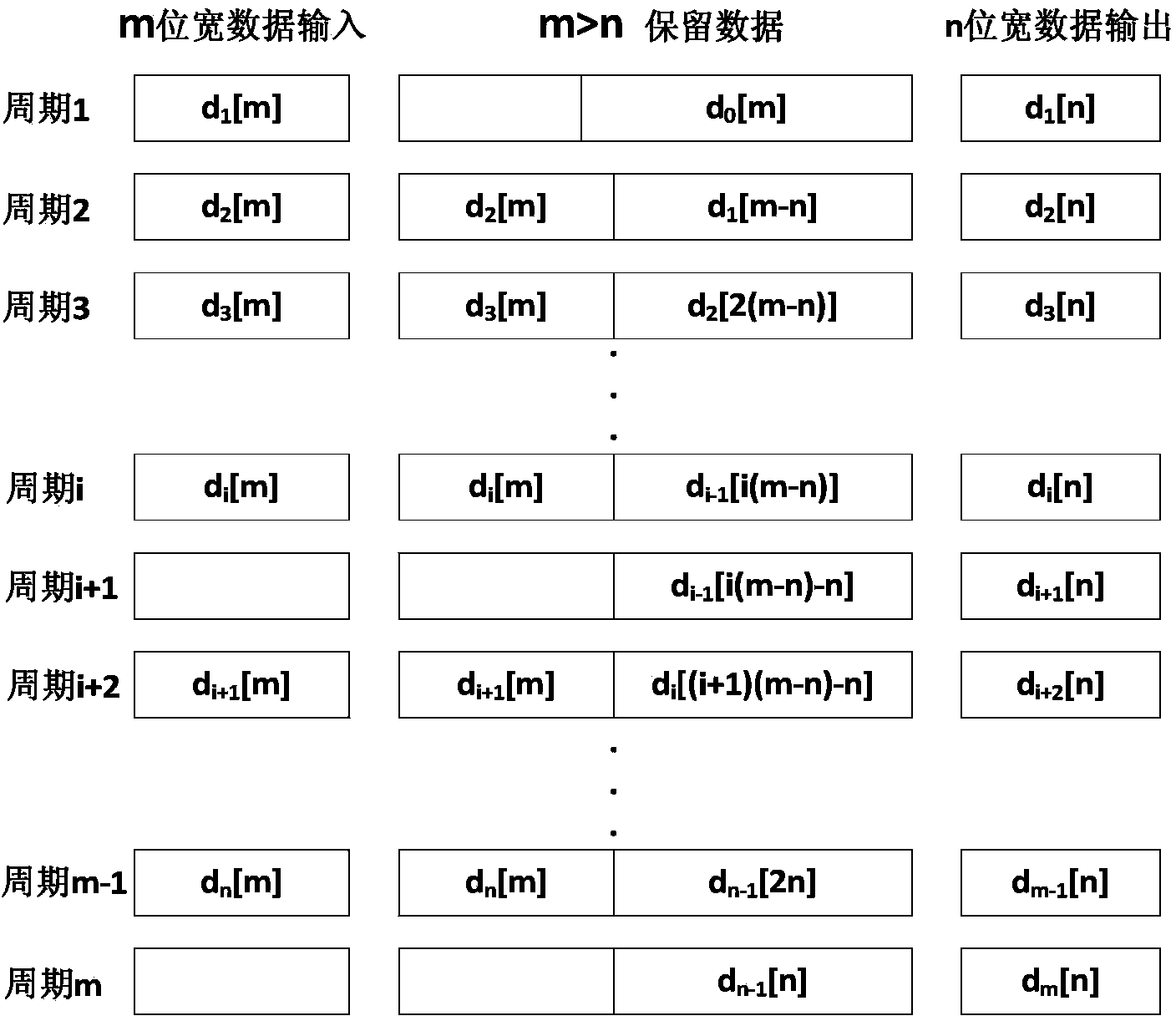

Gearbox circuit for reducing data bit width under condition of not changing Baud rate of data transmission and working method

The invention relates to a gearbox circuit for reducing the data bit width under the condition of not changing the Baud rate of data transmission and a working method. The gearbox circuit comprises a data bit width switching circuit, a counter generation circuit and a flag bit generation circuit. The output end of the counter generation circuit is connected with the data bit width switching circuit and the flag bit generation circuit respectively. According to a gearbox, a synchronous clock of input data of the gearbox can be utilized as the clock used for output data, an additional input clock is not needed, as a result, the design of a clock circuit is simplified, additional expenses for circuit design of an overall system are reduced, and design reliability is improved. The gearbox circuit is particularly suitable for circuit interior design; when data bit widths between modules or all IPs are not matched, the data bit widths between the modules are adjusted under the condition of not changing the Baud rate of data transmission, so that data bit width matching between all the internal modules is realized.

Owner:58TH RES INST OF CETC

Magnetic tape and magentic tape device

ActiveUS20170278540A1Large capacityIncrease the number ofAlignment for track following on tapesRecord information storageMagnetic tapeSurface roughness

The magnetic tape has a timing base servo pattern on the magnetic layer, wherein the centerline average surface roughness Ra on the surface of the magnetic layer is less than or equal to 1.8 nm, the magnetic layer contains a fatty acid ester, the full width at half maximum of spacing distribution measured by optical interferometry on the surface of the magnetic layer before and after vacuum heating the magnetic tape is greater than 0 nm but less than or equal to 7.0 nm, the difference of spacing measured by optical interferometry on the surface of the magnetic layer after and before vacuum heating the magnetic tape is greater than 0 nm but less than or equal to 8.0 nm.

Owner:FUJIFILM CORP

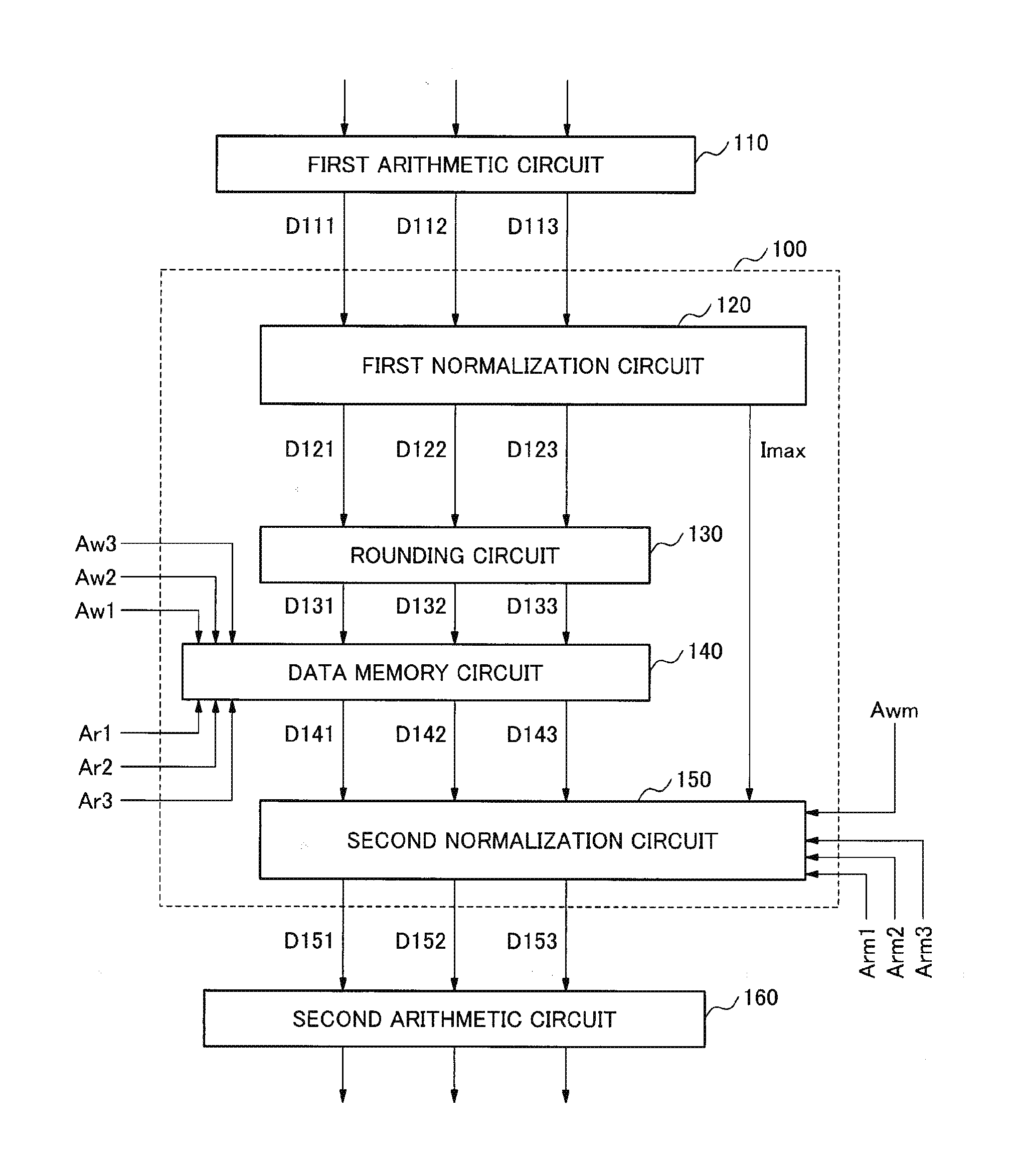

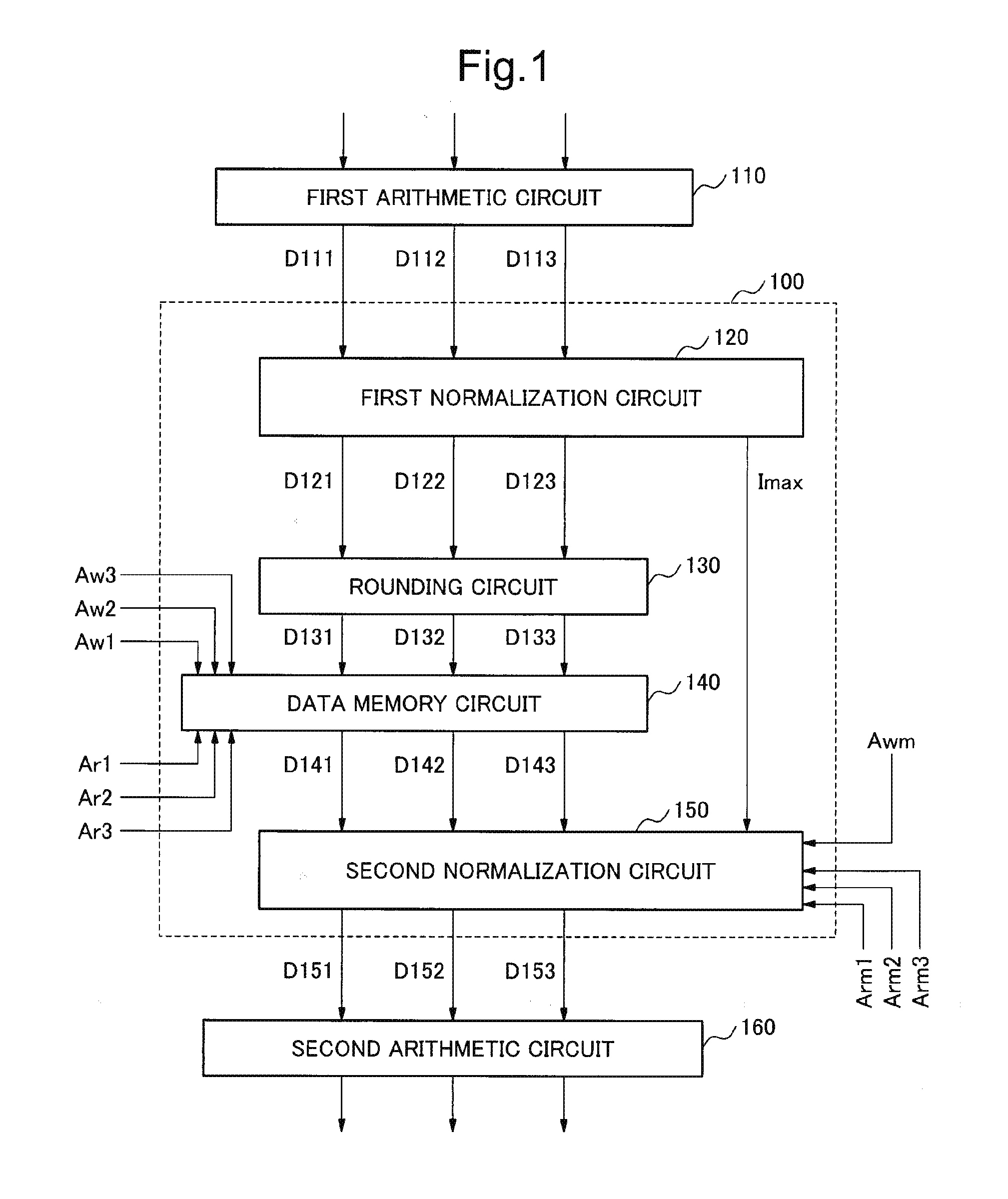

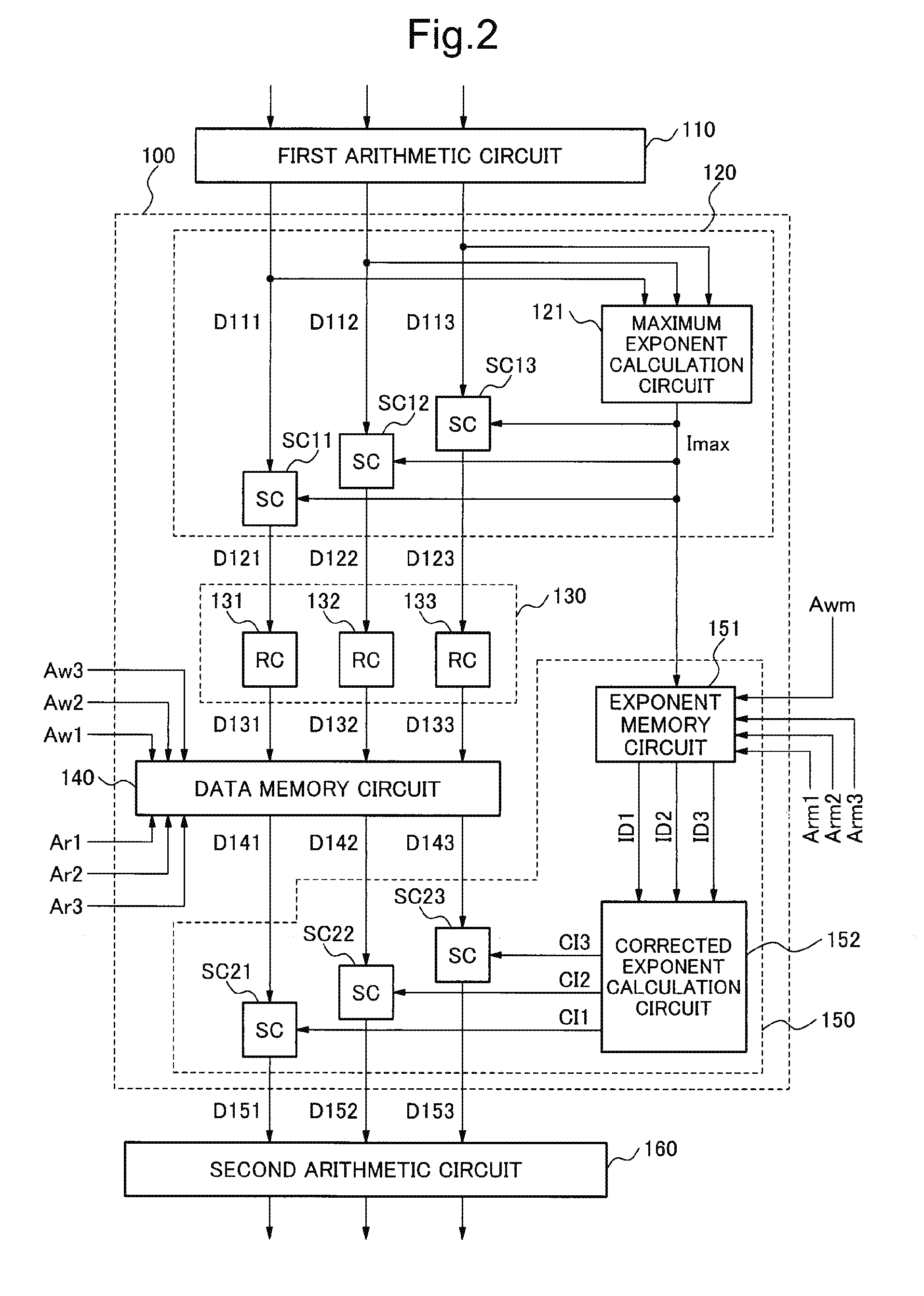

Arithmetic processing apparatus and an arithmetic processing method

ActiveUS20140089361A1Small circuit scaleImprove accuracyComputation using non-contact making devicesDigital computer detailsAlgorithmBlock floating-point

Provided is an arithmetic processing apparatus and an arithmetic processing method which can perform block floating point processing with small circuit scale and high precision.A first normalization circuit (120) performs a first normalization, in which a plurality pieces of data, which have a common exponent and which are either fixed-point number representation data or mantissa portion data of block floating-point number representation, are inputted in each of a plurality of cycles and the plurality of pieces of data inputted in each of the plurality of cycles are respectively normalized with the common exponent on the basis of a maximum exponent for the plurality of pieces of data inputted in a corresponding one of the plurality of cycle. A rounding circuit (130) outputs a plurality of pieces of rounded data which are obtained by reducing a bit width of respective one of the plurality of pieces of data on which the first normalization is performed. A first storage circuit (140) stores a plurality of pieces of rounded data regarding the plurality of cycles in which the first normalization is performed and outputs a plurality of designated pieces of rounded data among the stored plurality of pieces of rounded data. A second normalization circuit (150) performs a second normalization, in which the plurality of designated pieces of rounded data are respectively normalized with an exponent which is common to the plurality of designated pieces of rounded data on the basis of the maximum exponents used in the first normalization for the plurality of designated pieces of rounded data and a maximum value of the maximum exponents, and outputs a result of the second normalization.

Owner:NEC CORP

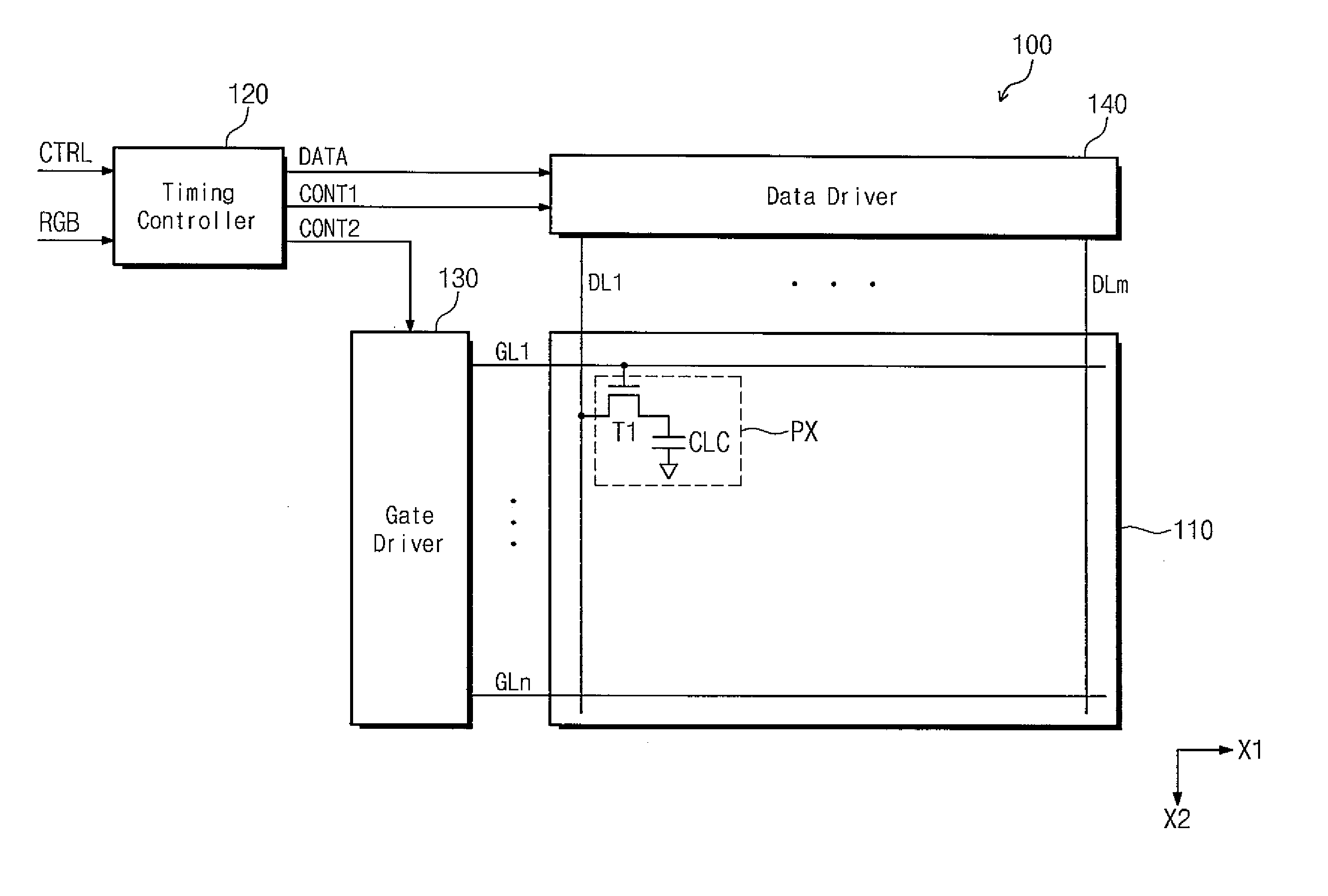

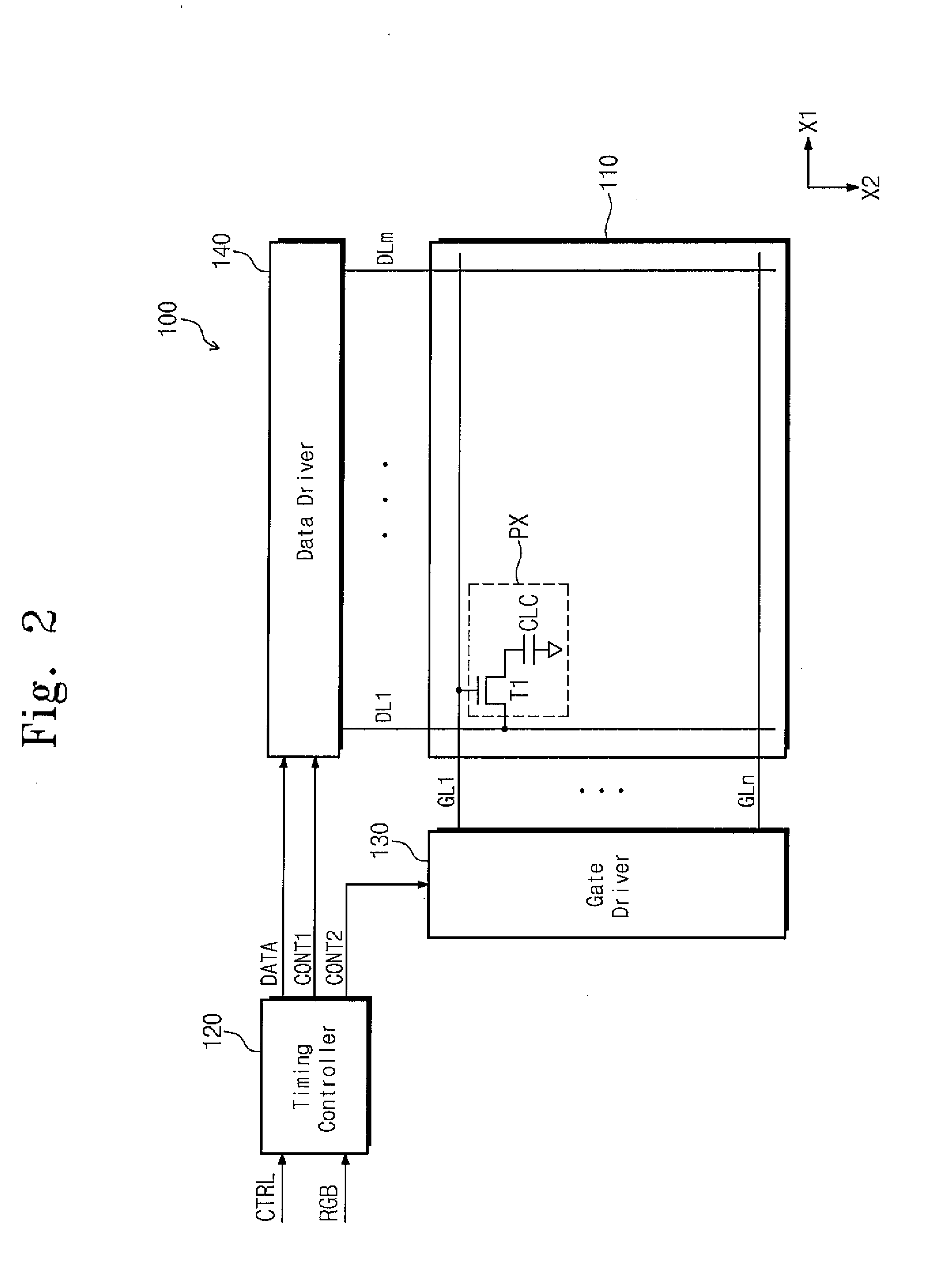

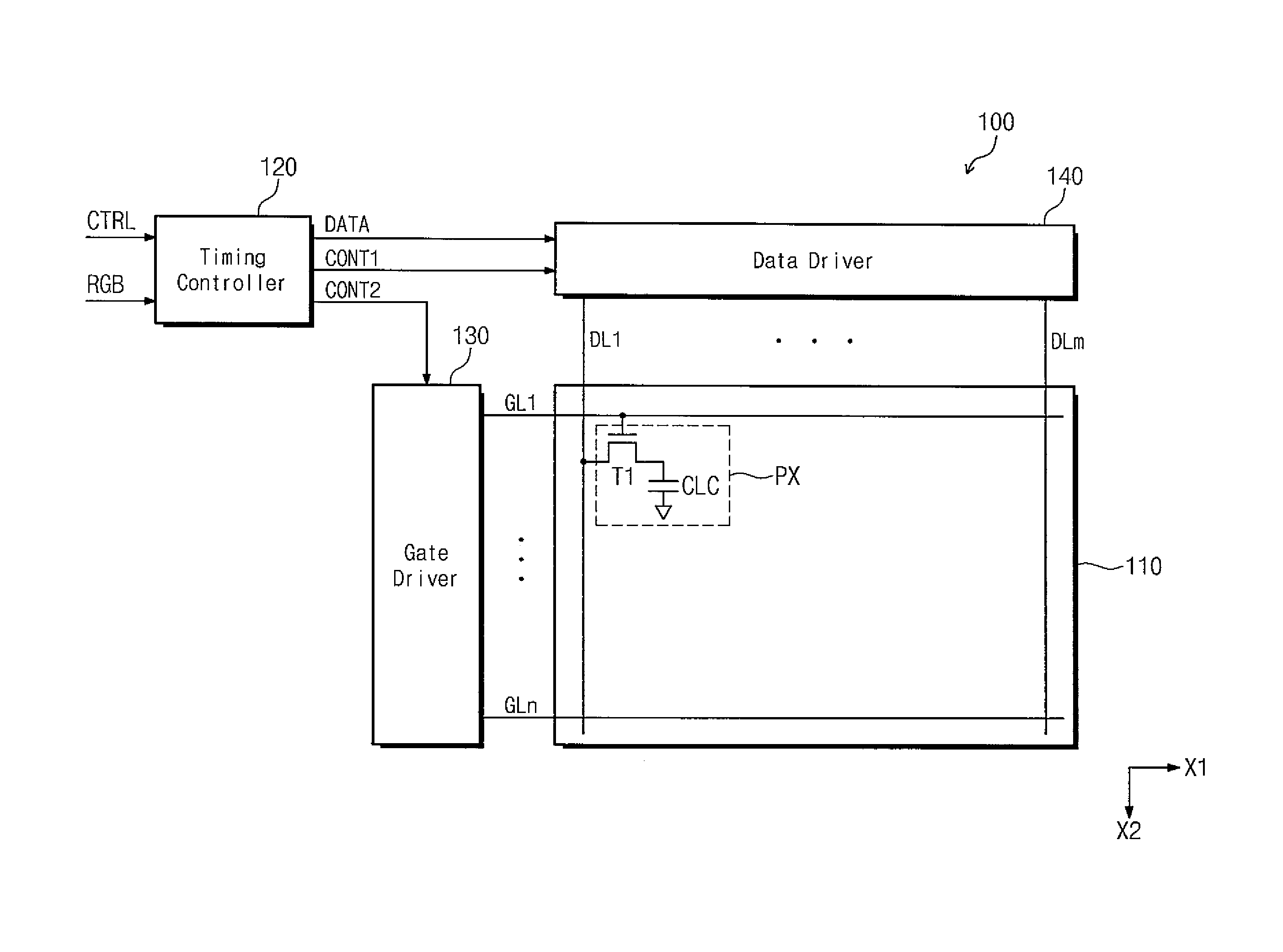

Display apparatus and driving method thereof

ActiveUS20150130782A1Reduce bit widthReducing and minimizing numberCathode-ray tube indicatorsDigital video signal modificationData signalDisplay device

A display device includes: a display panel comprising a plurality of pixels coupled to a plurality of gate lines and a plurality of data lines, respectively; a gate driver configured to drive the plurality of gate lines; a data driver configured to drive the plurality of data lines; and a timing controller configured to control the gate driver and the data driver and to provide the data driver with a data signal generated by compressing an image signal received from an external device, wherein the timing controller is configured to compress the image signal according to a first compression scheme and a second compression scheme to generate a first compression signal and a second compression signal, respectively, and wherein the timing controller is configured to select whichever one, from among the first compression signal and the second compression signal, that has a relatively narrower bit width as the data signal.

Owner:SAMSUNG DISPLAY CO LTD

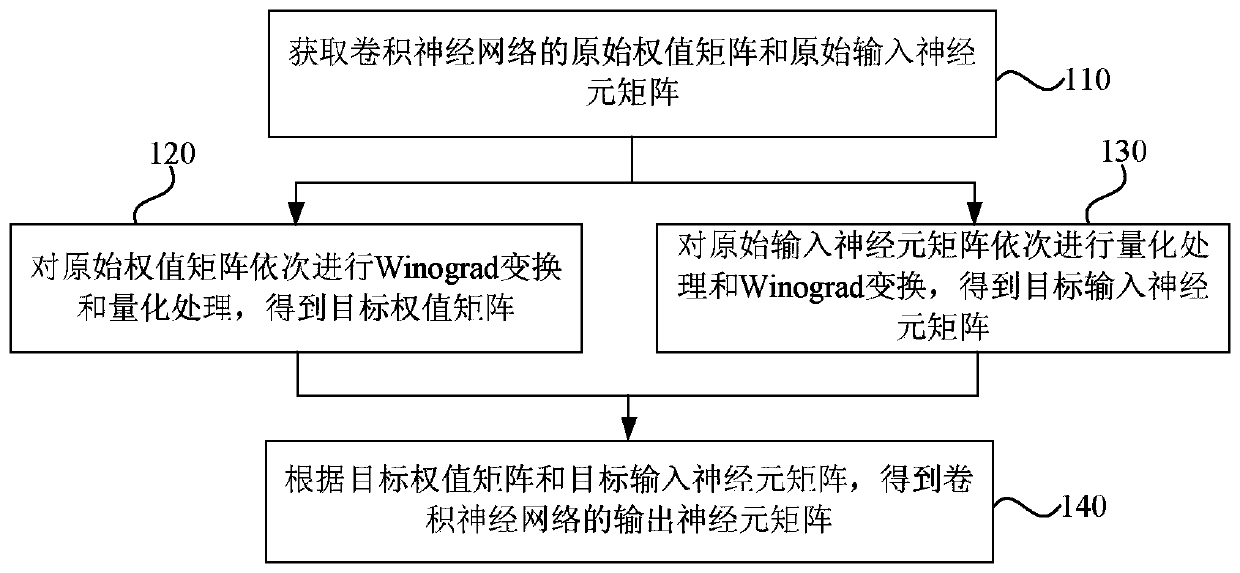

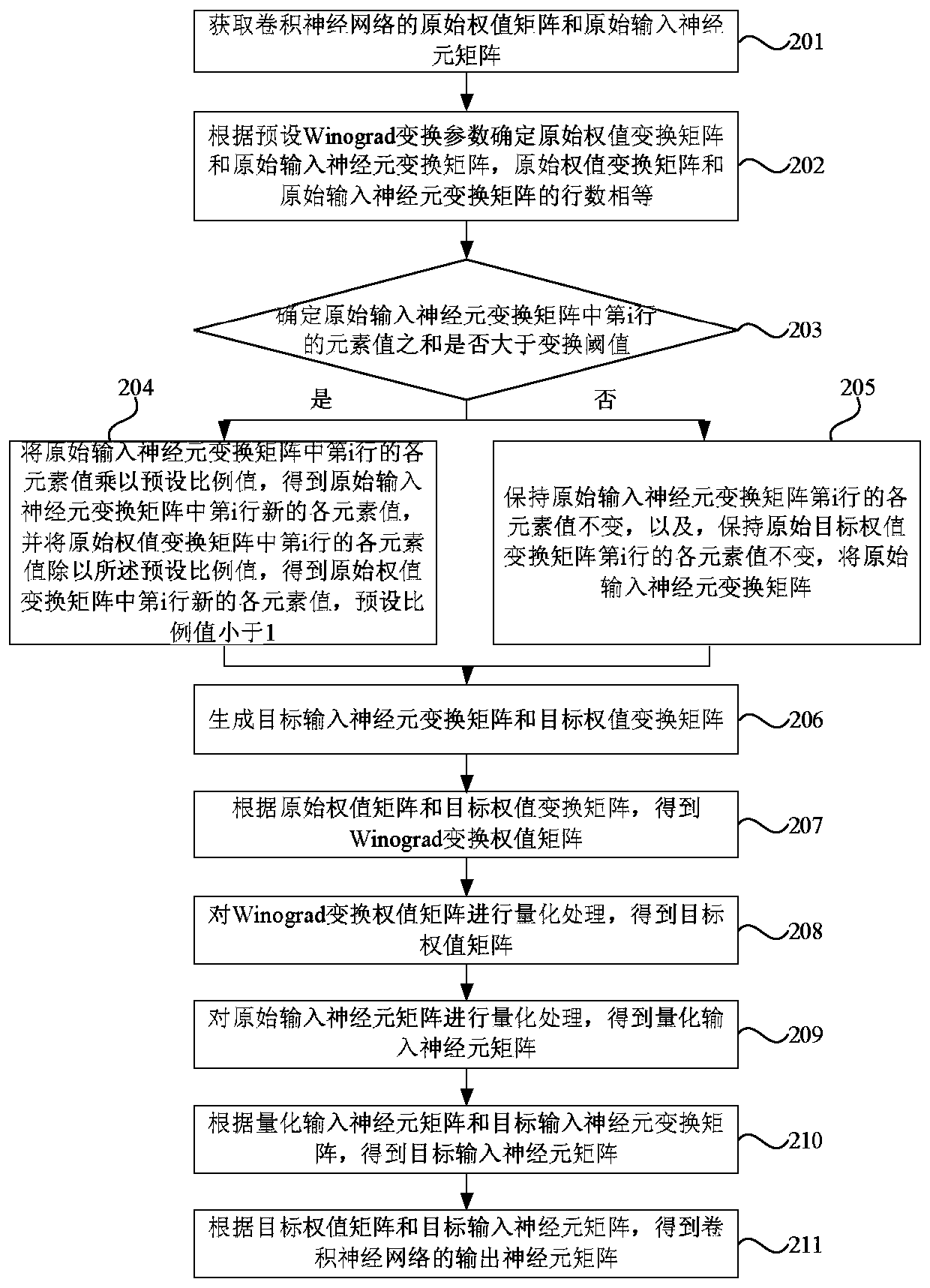

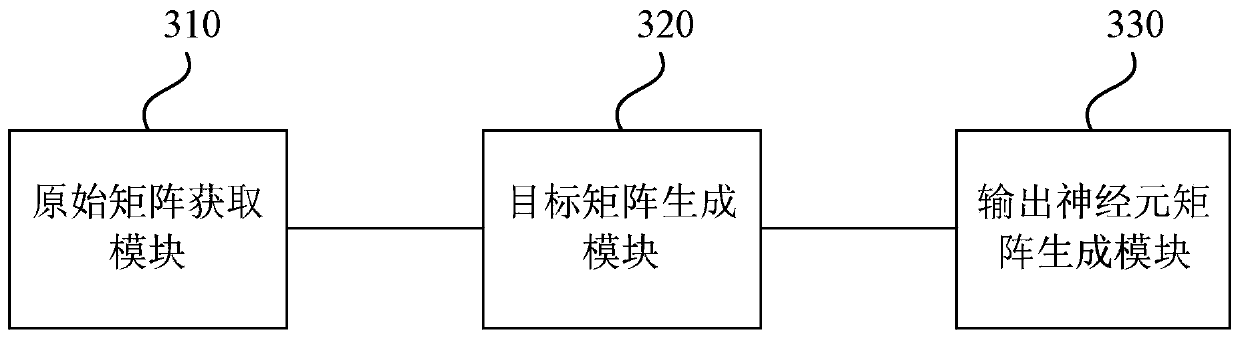

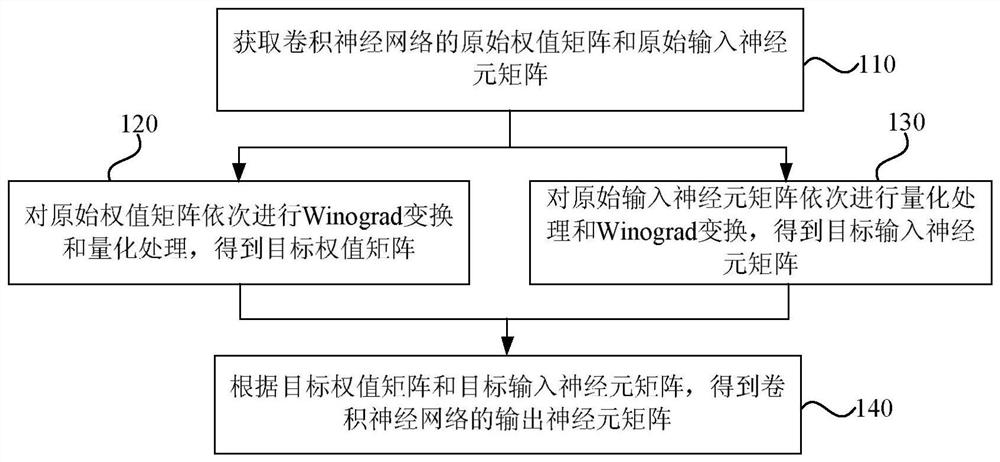

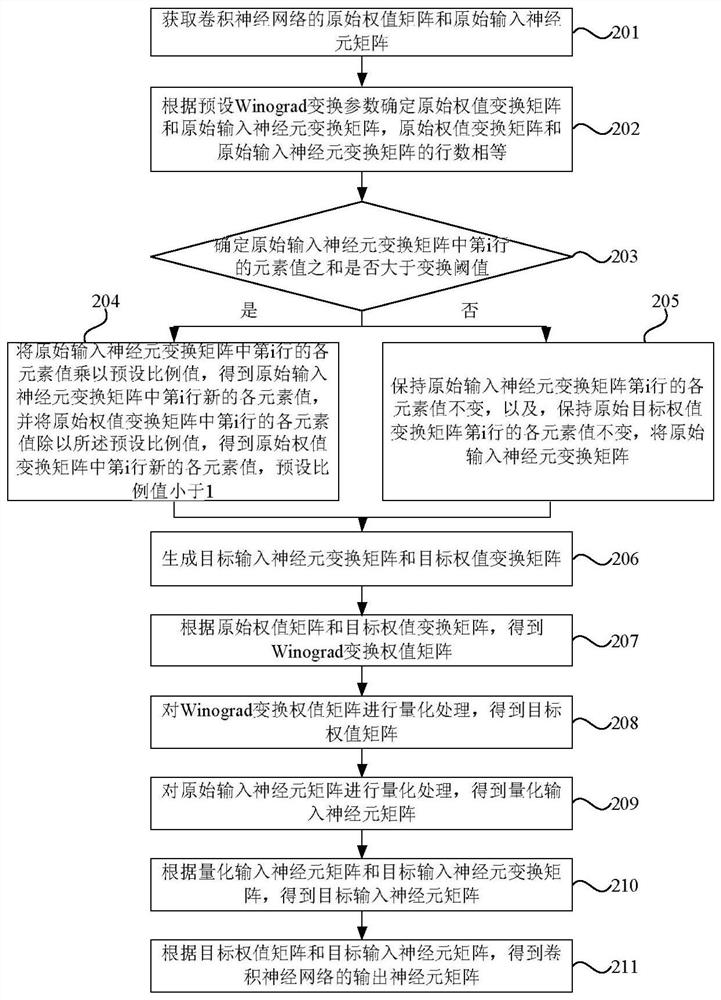

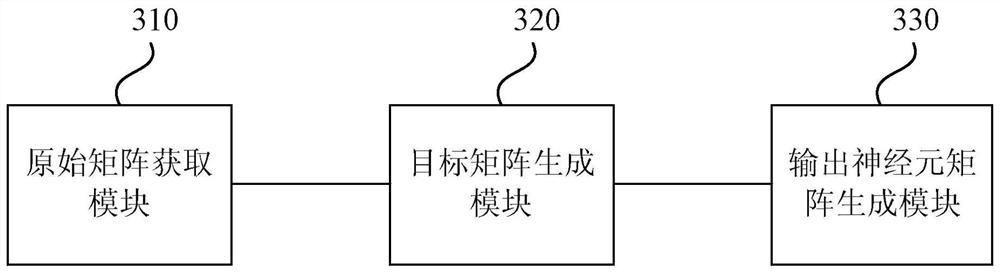

Convolutional neural network processing method and device, equipment and storage medium

The invention discloses a convolutional neural network processing method and device, equipment and a storage medium. The method comprises: obtaining an original weight matrix and an original input neuron matrix of the convolutional neural network, sequentially carrying out Winograd transformation and quantization processing on the original weight matrix to obtain a target weight matrix, sequentially carrying out quantization processing and Winograd transformation on the original input neuron matrix to obtain a target input neuron matrix, and obtaining an output neuron matrix of the convolutional neural network according to the target weight matrix and the target input neuron matrix. According to the embodiment of the invention, the time complexity of the convolutional neural network is reduced through Winograd transformation, and the data bit width of the convolutional neural network is reduced through quantization processing, so that the calculation speed of the convolutional neural network is improved.

Owner:BIGO TECH PTE LTD

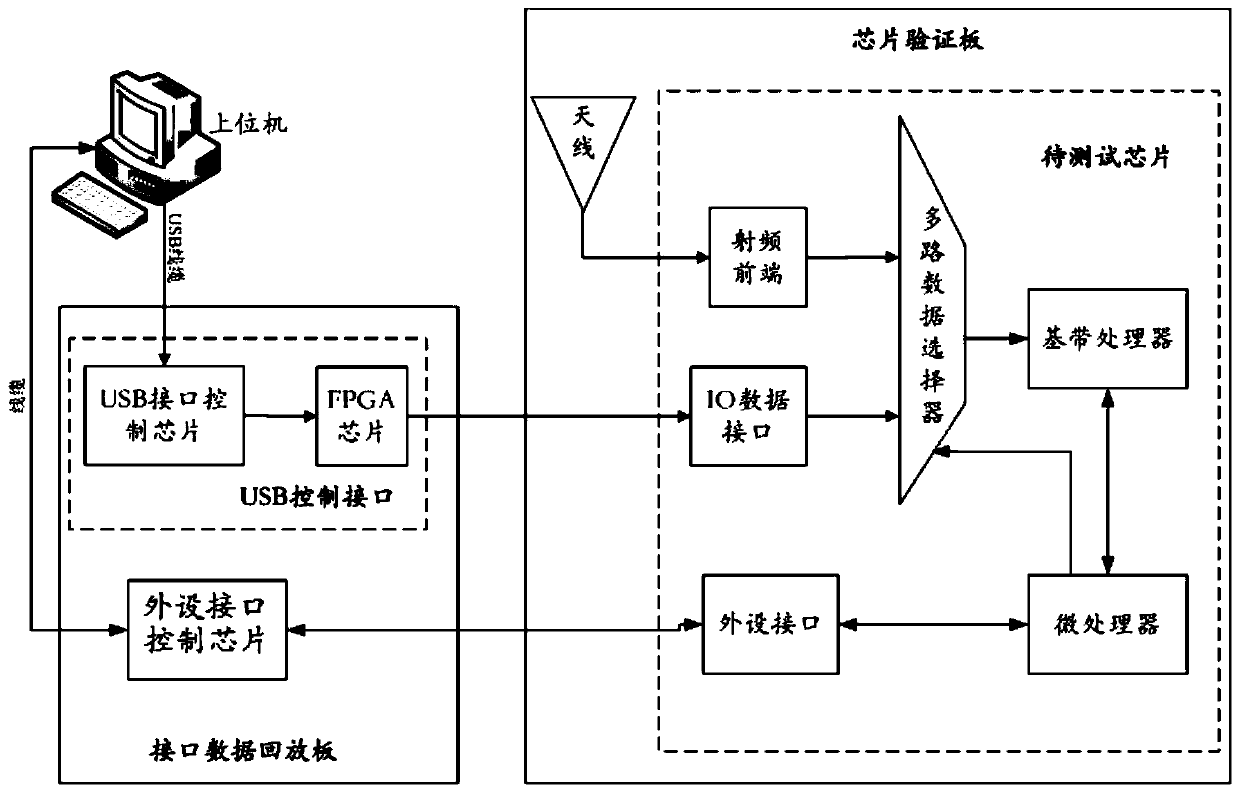

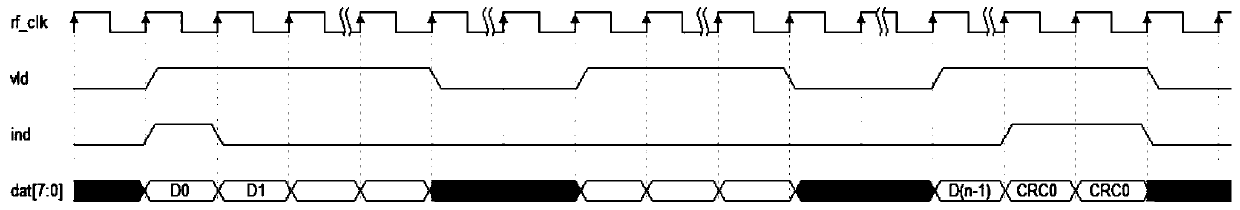

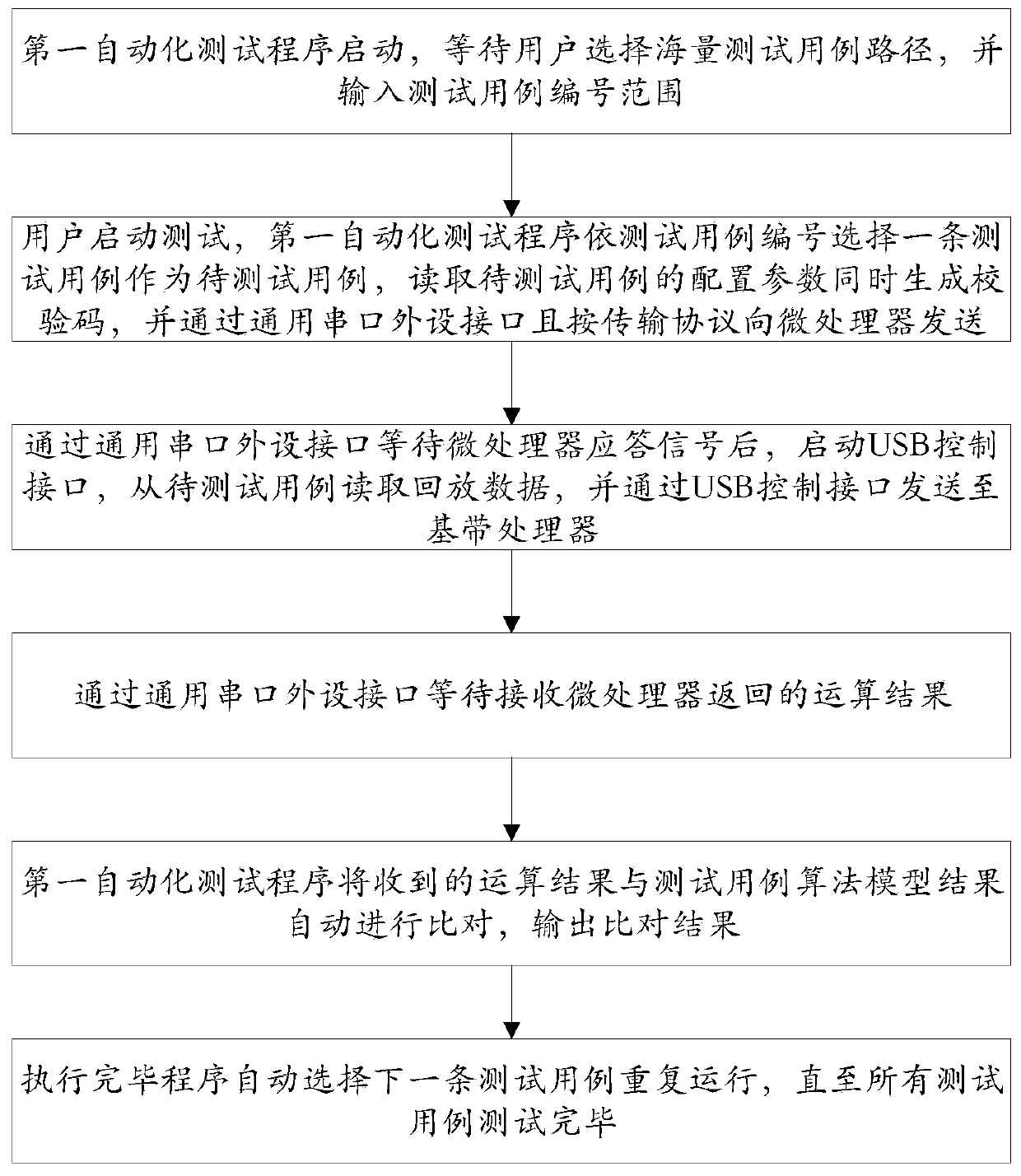

Satellite navigation baseband signal playback device, and automatic verification system and method

InactiveCN110146902ALow costAvoid inefficient manual testingSatellite radio beaconingControl signalMultiplexer

The invention relates to a satellite navigation baseband signal playback device, and an automatic verification system and method. The device is characterized in that one end of a peripheral interfacecontrol chip is connected to an upper computer, and the other end of the peripheral interface control chip is connected to a microprocessor through a peripheral interface; an input end of a USB control interface is connected to the upper computer, and an output end of the USB control interface is connected to the input end of a multi-channel data selector through an IO data interface; the input end of the multi-channel data selector is also connected to an antenna through a radio frequency front end; the output end of the multi-channel data selector is connected to a baseband processor, and the baseband processor is connected to the microprocessor; and a selection control signal of the multi-channel data selector is from the microprocessor. In the invention, through simplifying a function,a satellite navigation baseband signal playback function is only realized, a low-cost satellite navigation baseband signal playback device is realized through a mature, stable and low-cost interfacedata playback board and a chip verification board, and a hardware condition is provided for an automatic test of playback data.

Owner:WUHAN MENGXIN TECH CO LTD

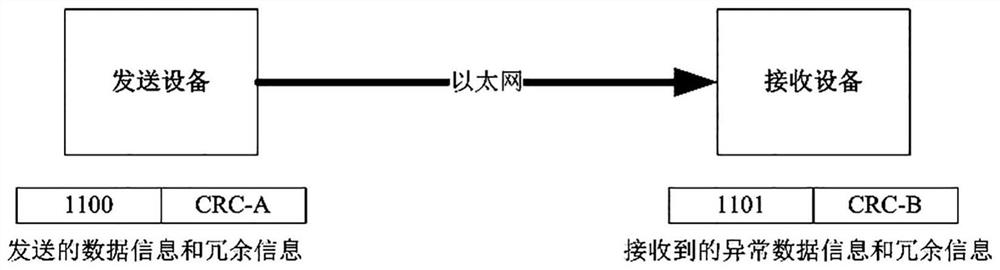

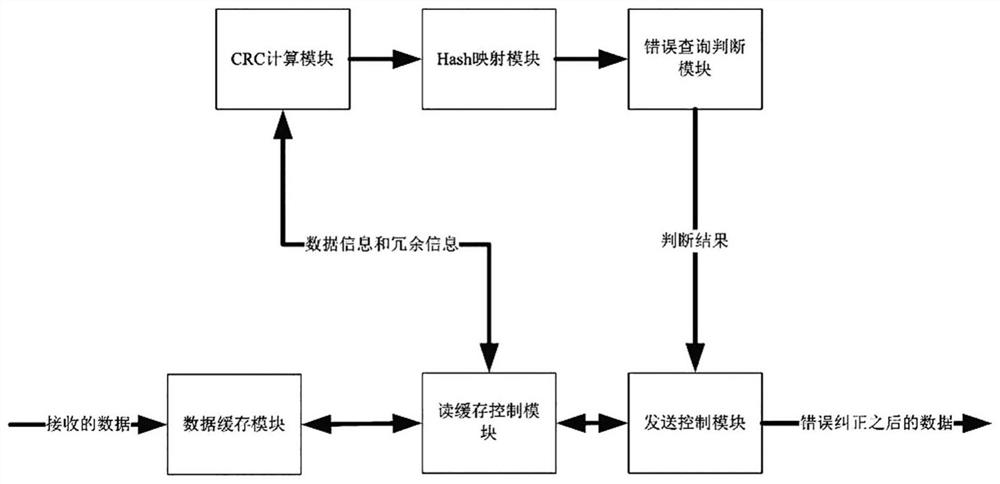

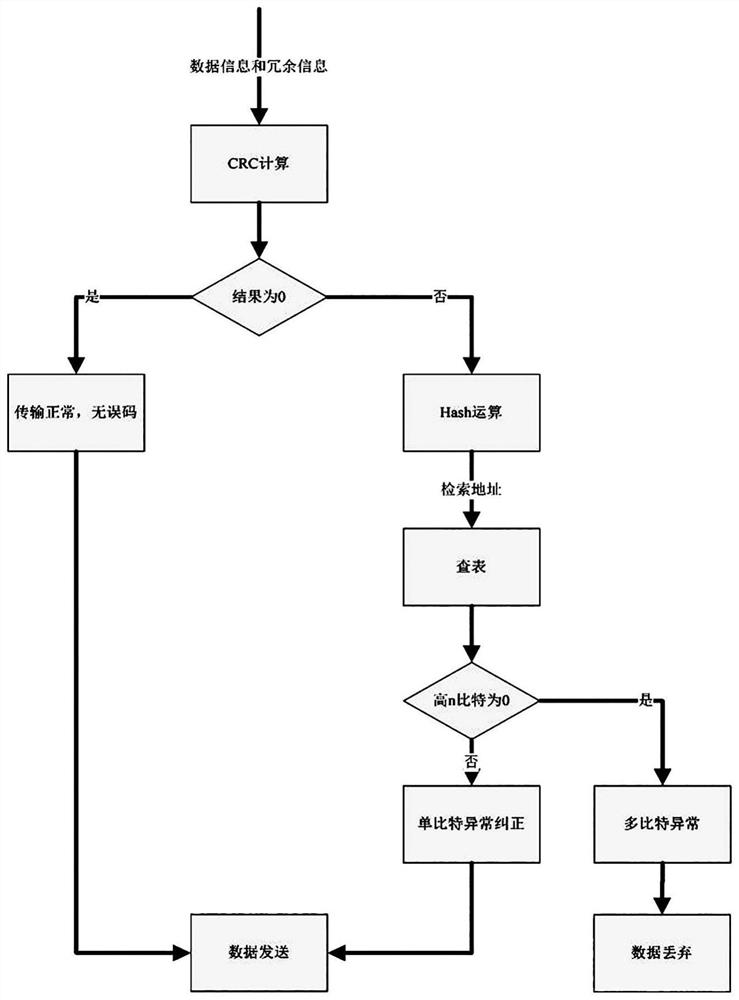

Single-bit error correction FPGA implementation method based on CRC16

ActiveCN113050519AReduce address spaceSave resourcesProgramme controlComputer controlData retrievalParallel computing

The invention relates to a single-bit error correction FPGA (Field Programmable Gate Array) implementation method based on CRC16 (Cyclic Redundancy Check 16). The method comprises a data cache module, a read cache control module, an error judgment arbitration module and a sending control module, and the error judgment arbitration module comprises a CRC (Cyclic Redundancy Check) calculation module, a Hash mapping module and an error query judgment module. According to the method, the data information and the redundant information are sent into the CRC calculation module together for Hash operation, delay in the data processing and judging process is reduced, the data bit width is reduced, in other words, the address space of data retrieval is reduced, and the method has the beneficial effects of being high in data processing efficiency and saving hardware resources.

Owner:SHANDONG INST OF COMMERCE & TECH

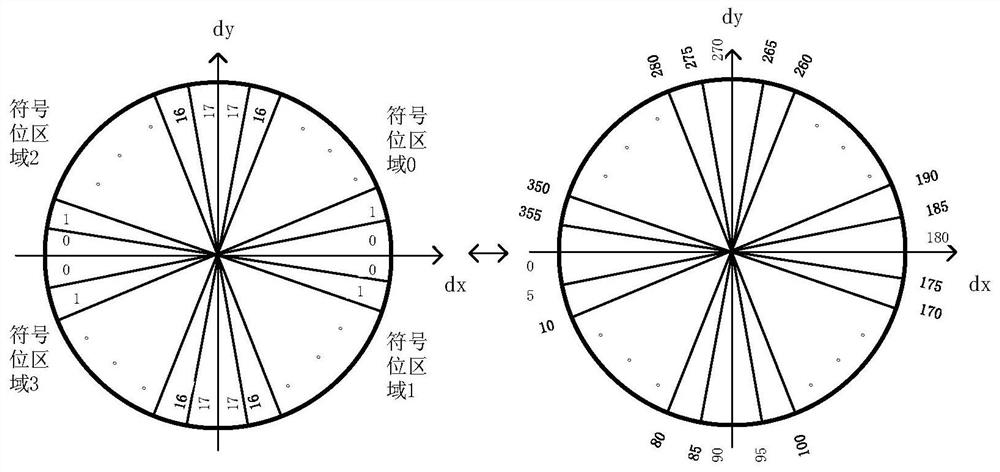

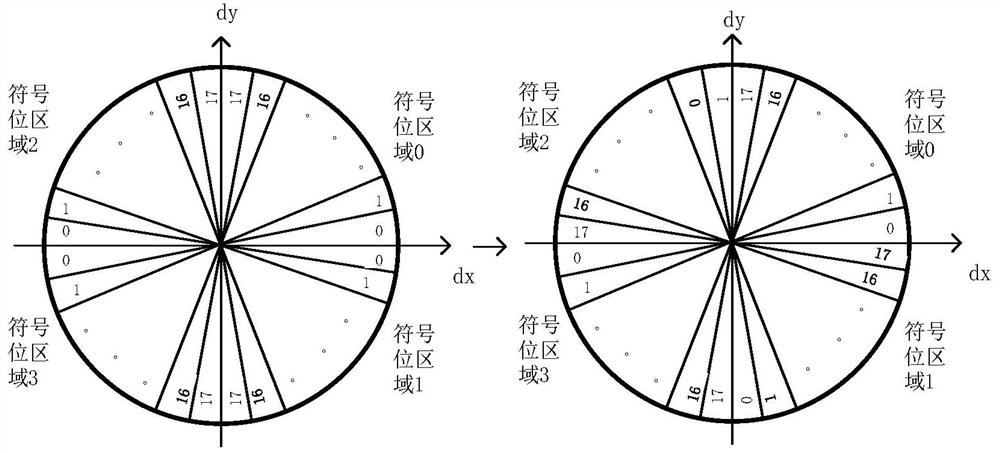

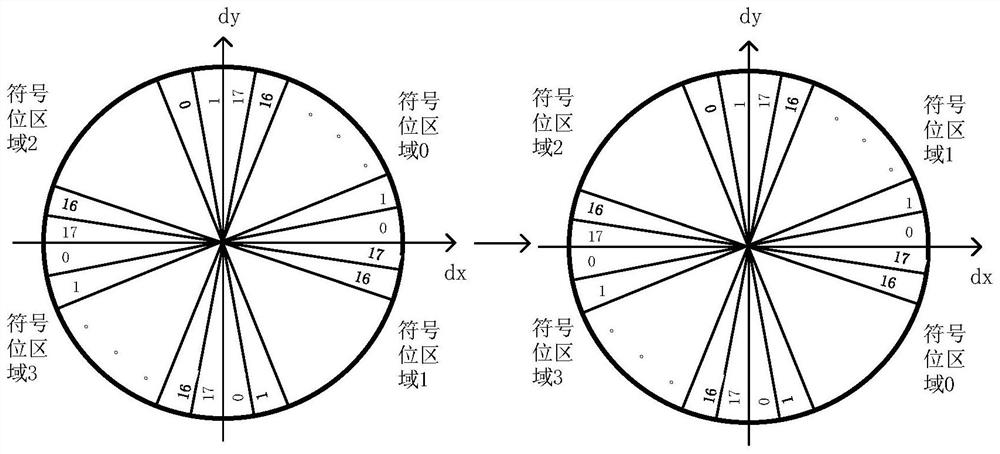

A method and system for quickly generating SIFT descriptors

ActiveCN108664982BReduce data widthReduce usageCharacter and pattern recognitionComputer graphics (images)Algorithm

The invention relates to a method for quickly generating a SIFT descriptor, comprising the following steps: S1. receiving Gaussian graph data information transmitted from the outside; S2. obtaining the main direction of the key point after passing through the amplitude and angle calculation module; S3 The obtained main direction will be sent to the rotation interval calculation module to calculate the rotated argument angle information; S4. The rotation interval calculation module will receive the initial argument angle information and the main direction, and then perform interval rotation according to the main direction, and finally determine its location Row and column information; at the same time receive the amplitude and weight 2 to weight the amplitude; S5.128bin calculation module receives the angle information after rotation, the coordinate information after rotation and the weighted amplitude, so as to calculate the 128-dimensional description sub for output.

Owner:SUN YAT SEN UNIV

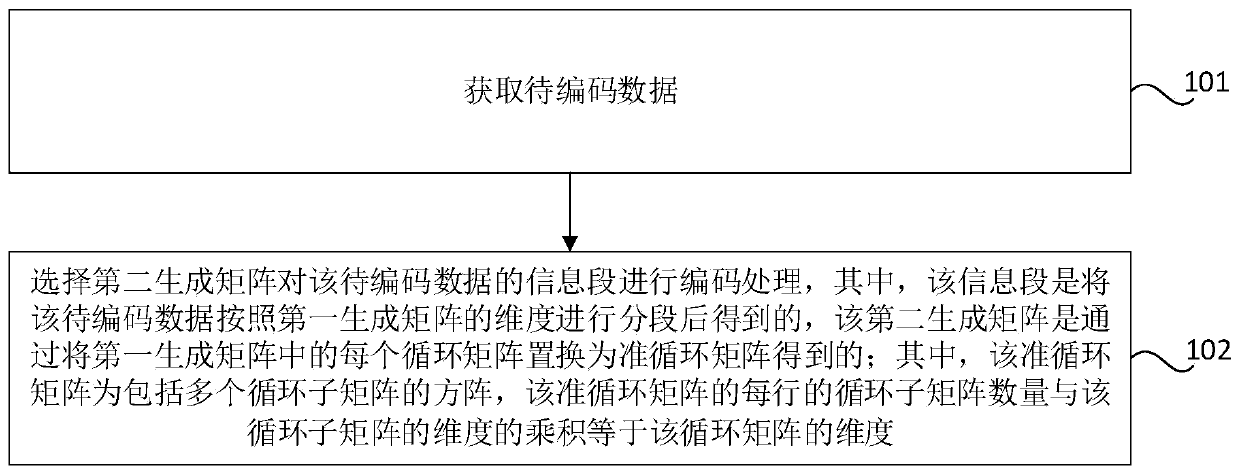

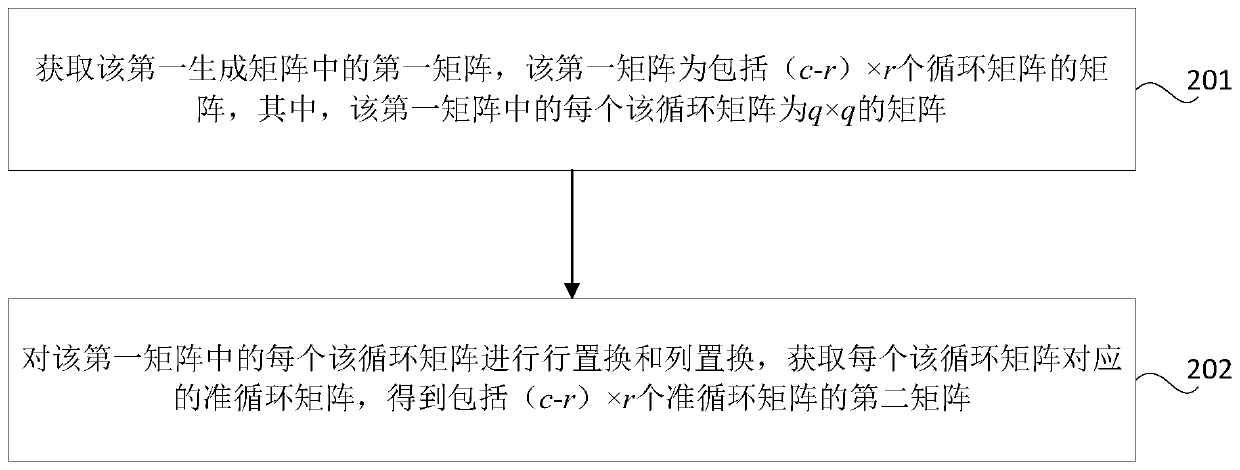

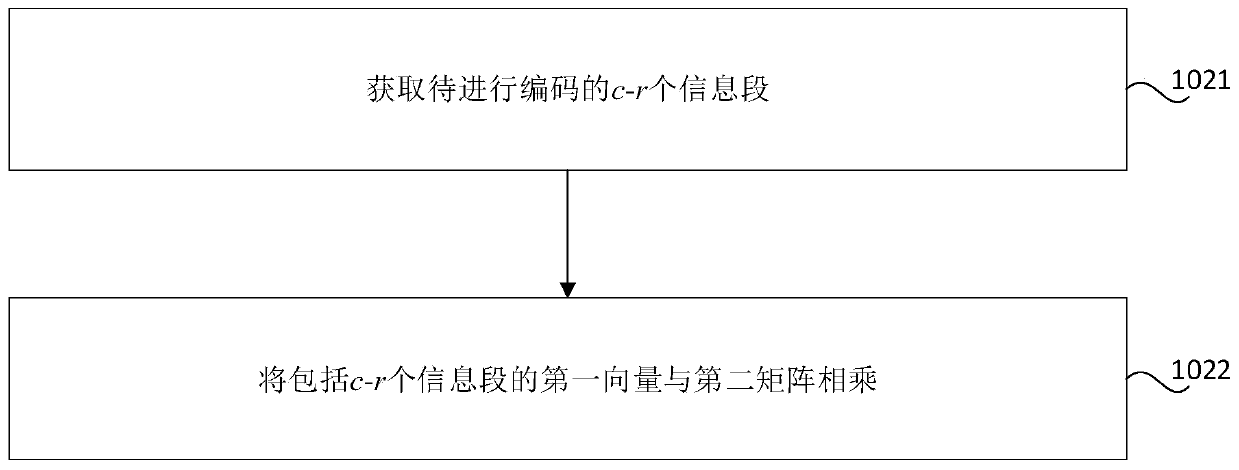

Data processing method and device

ActiveCN106877882BReduce occupancyIncrease working frequencyError correction/detection using multiple parity bitsCode conversionCode generationAlgorithm

The invention relates to a data processing method and device. The method comprises the steps that data to be encoded are acquired; a second generation matrix is selected to encode the message segment of the data to be encoded, wherein the message segment is formed by segmenting the data to be encoded according to the dimensionality of a first generation matrix, and the second generation matrix is formed by replacing each cyclic matrix in the first generation matrix with a quasi-cyclic matrix; the quasi-cyclic matrix is a matrix comprising a number of cyclic sub-matrices; and the product of the number of the cyclic sub-matrices of each row of the quasi-cyclic matrix and the dimension of the cyclic sub-matrices is equal to the dimension of the cyclic matrix. According to the invention, a code generation matrix is transformed; without changing the quasi-cyclic characteristic of the generation matrix, the data bit width of encoding operation is reduced; the logical resource occupancy of the operation is reduced; and the operating frequency of encoding calculation is improved.

Owner:SHENZHEN YILIAN INFORMATION SYST CO LTD

Display apparatus and driving method thereof

ActiveUS9530383B2Reduce data widthReducing and minimizing numberCathode-ray tube indicatorsDigital video signal modificationDisplay deviceData signal

A display device includes: a display panel comprising a plurality of pixels coupled to a plurality of gate lines and a plurality of data lines, respectively; a gate driver configured to drive the plurality of gate lines; a data driver configured to drive the plurality of data lines; and a timing controller configured to control the gate driver and the data driver and to provide the data driver with a data signal generated by compressing an image signal received from an external device, wherein the timing controller is configured to compress the image signal according to a first compression scheme and a second compression scheme to generate a first compression signal and a second compression signal, respectively, and wherein the timing controller is configured to select whichever one, from among the first compression signal and the second compression signal, that has a relatively narrower bit width as the data signal.

Owner:SAMSUNG DISPLAY CO LTD

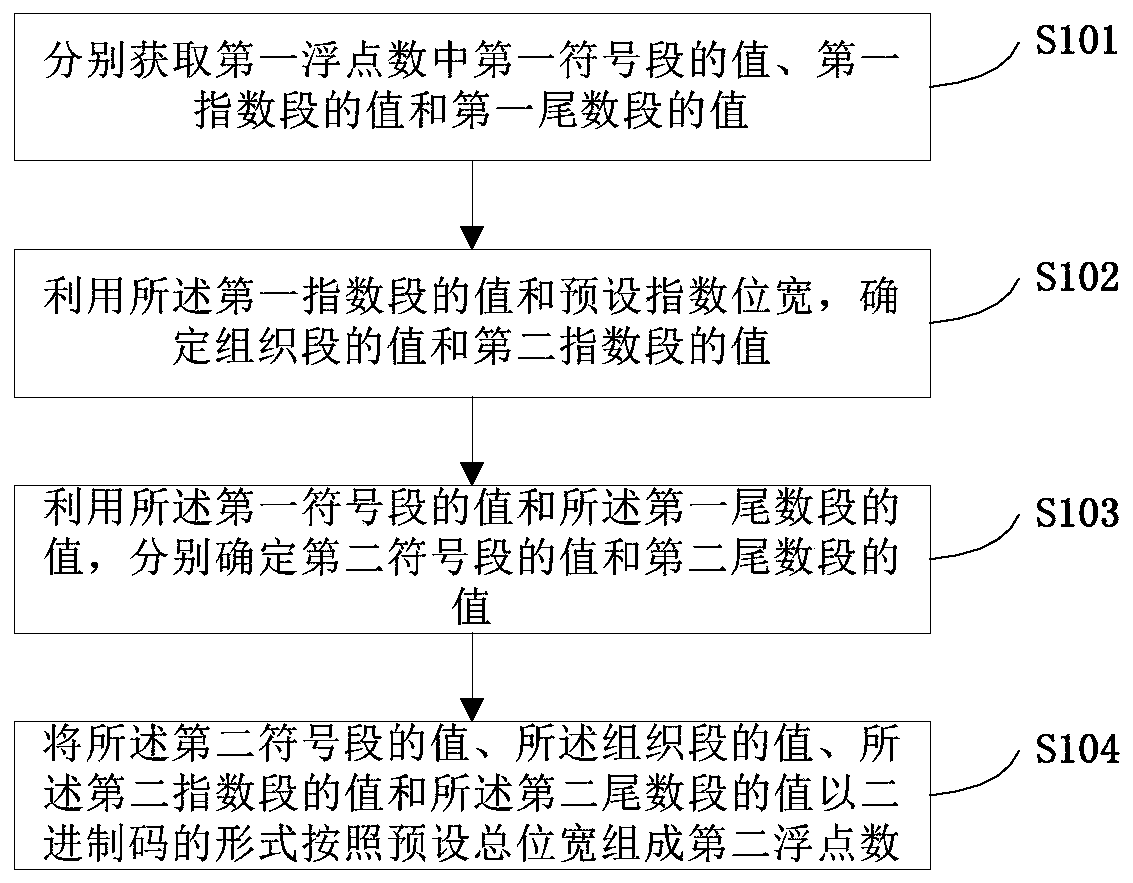

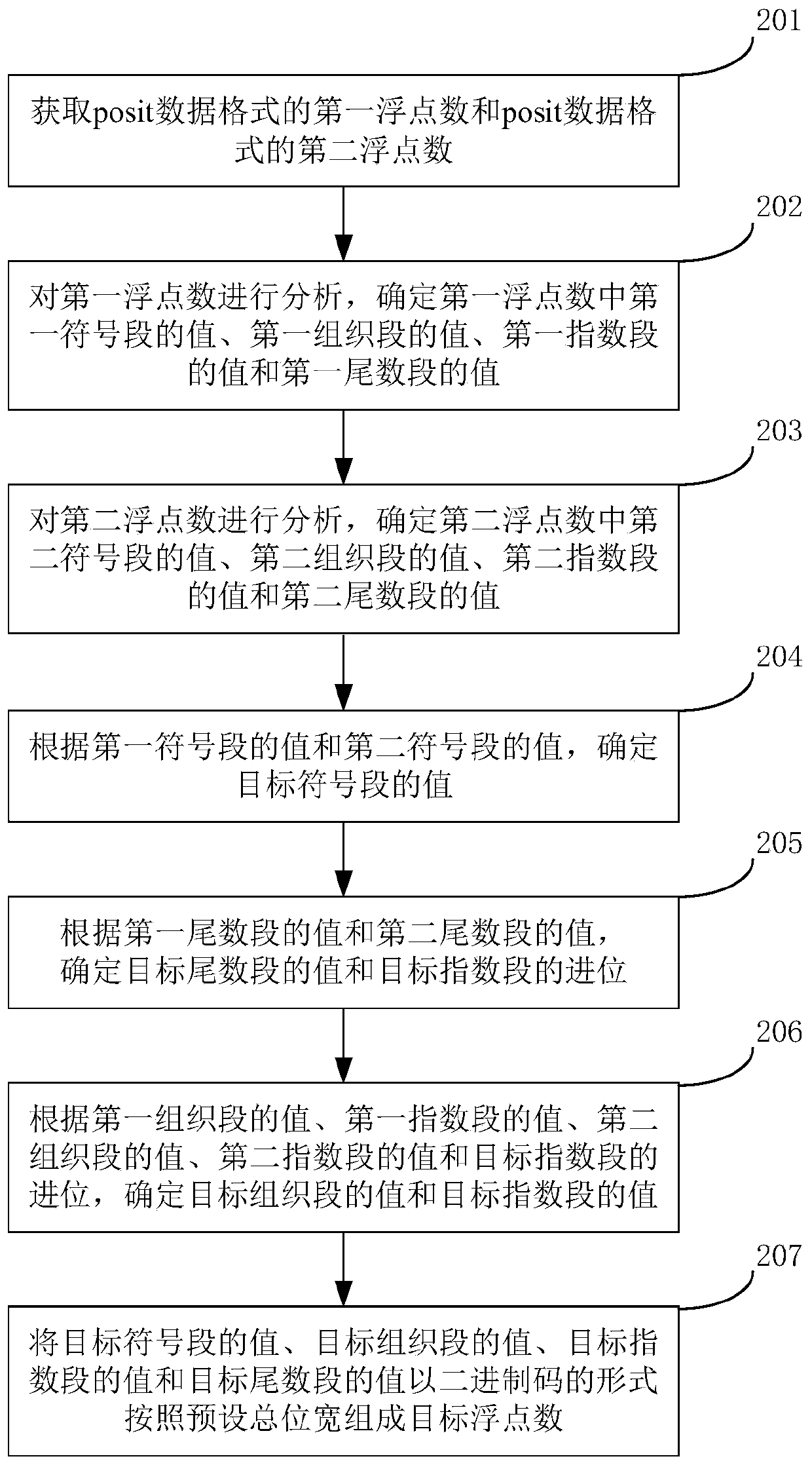

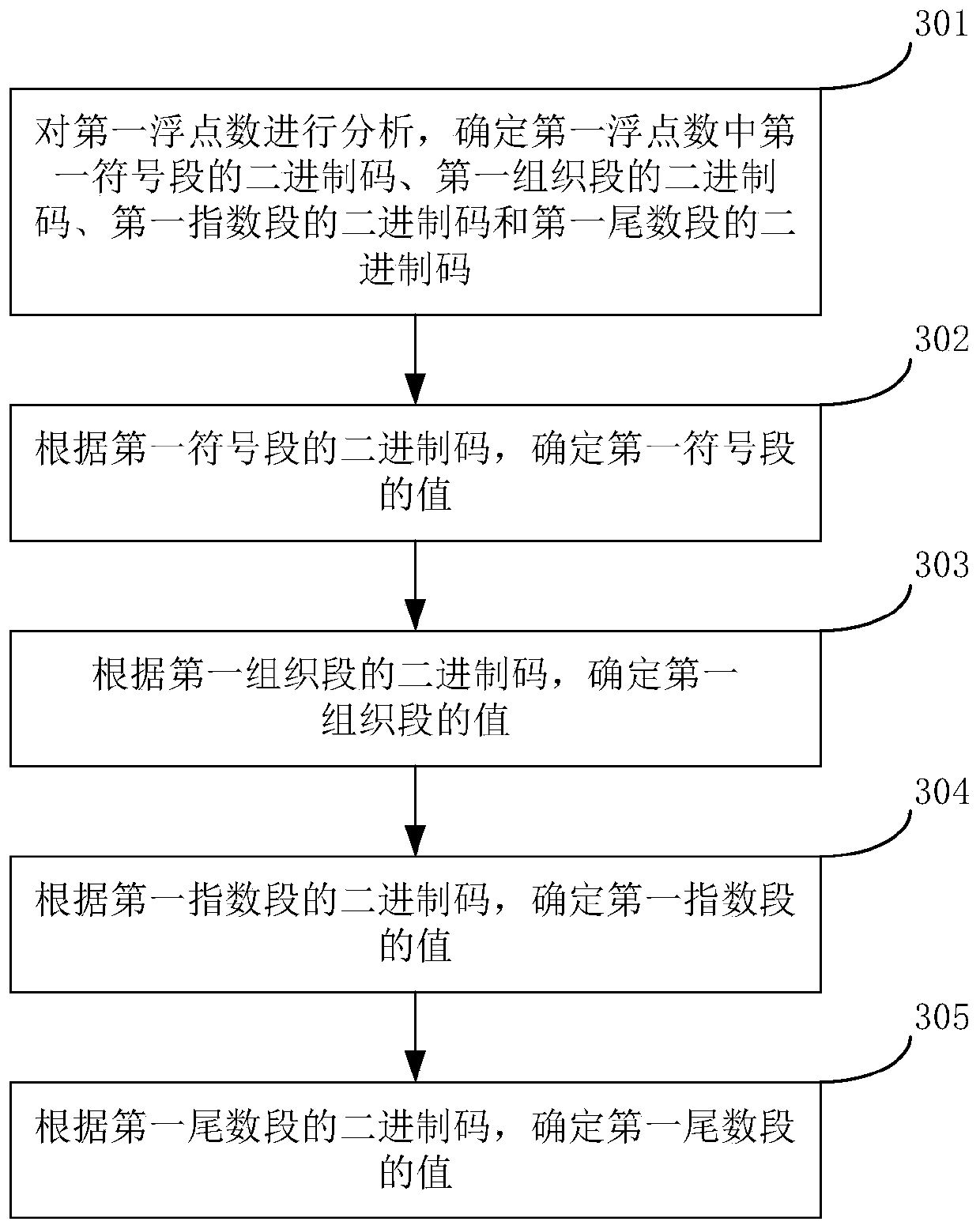

Floating-point number conversion method and device

PendingCN111313905AImprove training efficiencyGuaranteed accuracyCode conversionEnergy efficient computingData setAlgorithm

The invention discloses a floating-point number conversion method and a floating-point number conversion device, which can convert a single-precision floating-point number based on an IEEE 754 specification into a floating-point number in a posit data format, namely a second floating-point number. In the training process of a plurality of neural networks, the operation data approximately obeys normal distribution; data can be concentrated near 0 through transformation; however, the floating-point number of the posit data format in the invention can ensure the precision near 0 in the neural network training process; moreover, the preset total bit width of the floating-point number in the posit data format can be regulated and controlled, so that the data bit width can be reduced to a greatextent, resources required for storage and resources consumed in the read-write process are reduced, and the efficiency of neural network training is improved.

Owner:NANJING UNIV

A signal processing method and device

ActiveCN104821861BAvoid quantization errorDoes not increase sensitivity to effectsError preventionBit slicingComputer science

Owner:DATANG MOBILE COMM EQUIP CO LTD

Semiconductor Device

ActiveUS20070080717A1Suppress generationImprove data transfer rateSolid-state devicesDigital storageControl signalDelay periods

A semiconductor device is disclosed which increases the data transfer rate in transferring data output from an input / output sense amplifier via a global data bus line by reducing the swing width of the data placed on the global data bus line. The semiconductor device may include a data transfer unit which receives first data, and outputs second data obtained by driving the first data to a predetermined level to a data transfer line; a data receiver which receives the second data transferred via the data transfer line; a delay which outputs a plurality of delay signals respectively obtained by delaying the second data outputted from the data transfer unit by different delay periods; a delay controller which selects one of the delay signals in accordance with an operation mode of the semiconductor device, and outputs at least one adjustment signal for adjusting a driving period of the data transfer unit for the first data based on the delay period of the selected delay signal; and a transfer controller which receives the first data and the at least one adjustment signal, and outputs at least one transfer control signal for controlling the operation of the data transfer unit, based on the received first data and adjustment signal.

Owner:SK HYNIX INC

Floating-point multiplication method and device based on posit data format

ActiveCN111367497AReduce training timeGuaranteed accuracyDigital data processing detailsEnergy efficient computingAlgorithmData format

The invention provides a floating-point multiplication method and device based on a posit data format. The method comprises the steps that after a first floating-point number and a second floating-point number are obtained, the first floating-point number and the second floating-point number are analyzed, and a target floating-point number is determined according to values obtained after analysis.According to the method, multiplication is carried out by adopting a posit data format, so that the data bit width can be reduced to a great extent while the precision is ensured near 0, the trainingtime of the neural network is shortened, and the requirements on resources such as storage and bit width are also reduced.

Owner:NANJING UNIV

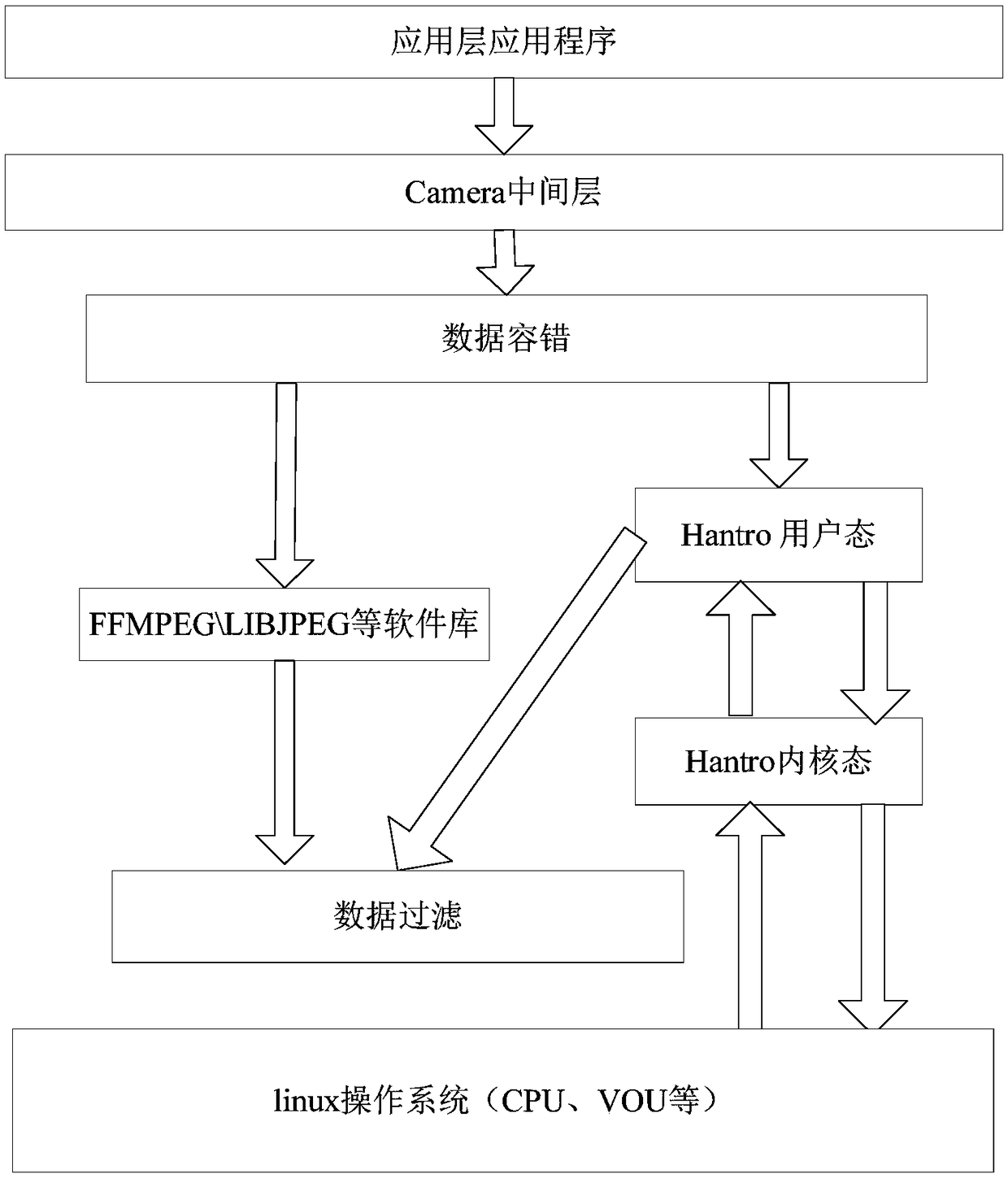

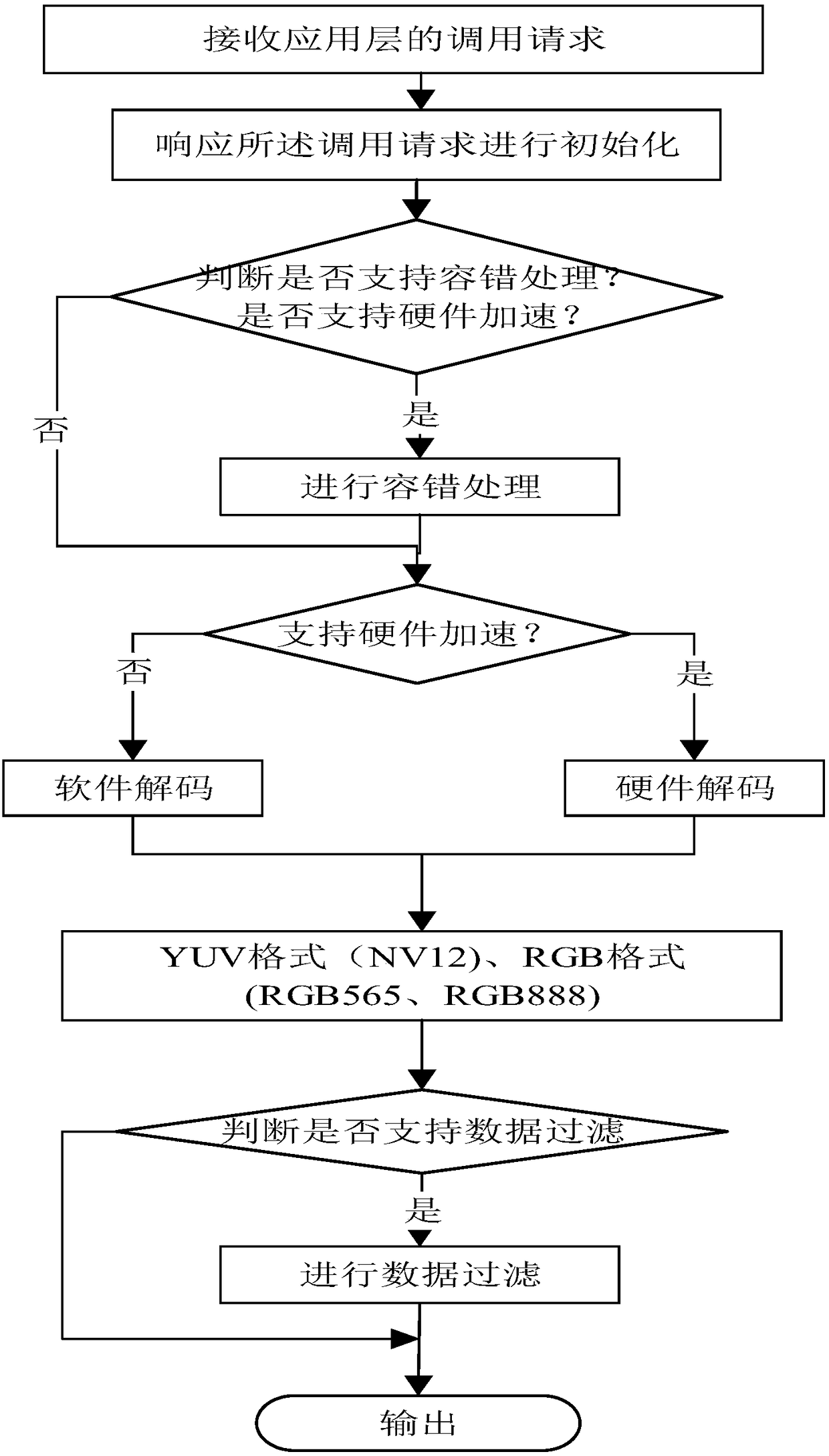

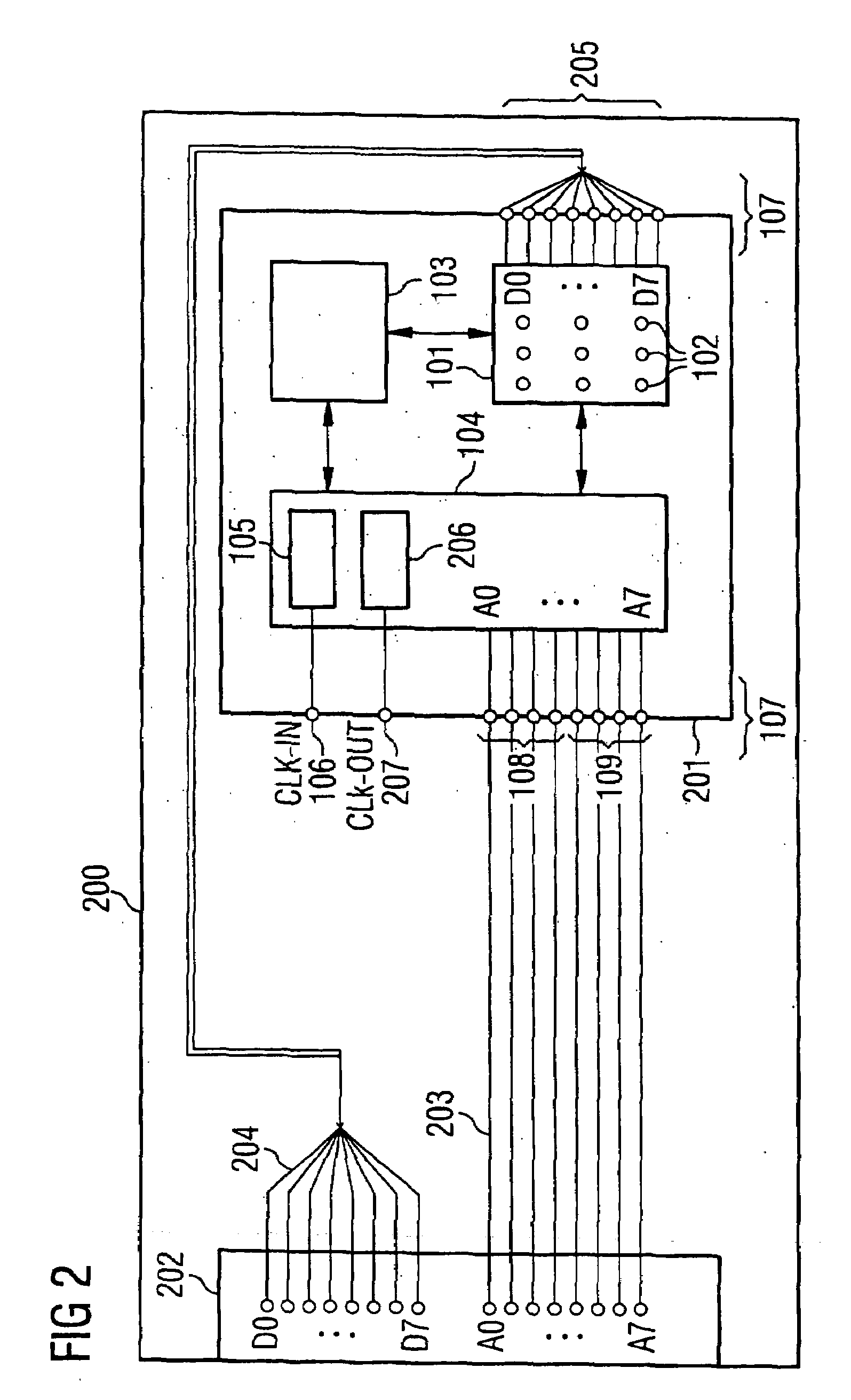

Camera middle layer image processing method and system on chip

ActiveCN109120938AImprove decoding rateReduce loadInterprogram communicationDigital video signal modificationImaging processingComputer module

A Camera middle layer image processing method and a system on chip are provided. By adding fault-tolerant processing, abnormal or missing video data is pre-repaired in order to reduce the probabilityof error during video data decoding, and hardware decoding is carried out by a decoder as much as possible in order to reduce the probability of software calling for decoding and improve the decodingperformance of the system on chip. Meanwhile, a step of filtering processing is added in order to meet the requirements of subsequent modules and improve the display performance of the system. The multi-core central processing unit of the system on chip is bound to different threads to realize parallel operation of software and hardware and to further improve the display performance of the systemon chip. In addition, as a better decoded data format is selected for the system on chip, higher display quality can be provided while the display performance is guaranteed.

Owner:SANECHIPS TECH CO LTD

Integrated memory device and method for its testing and manufacture

InactiveUS20070300106A1Reduce data widthReduce in quantityElectronic circuit testingError detection/correctionData storingData interface

An integrated memory device includes an array of memory cells for storing data, a memory cell selector operationally connected to the array for selecting at least one memory cell of the array, a data interface adapted to store data provided to the data interface in a selected memory cell and to provide data stored in a selected memory cell to the data interface for retrieval, and a control circuit operationally connected to the memory cell selector and the data interface.

Owner:POLARIS INNOVATIONS

A convolutional neural network processing method, device, equipment and storage medium

ActiveCN111382854BReduce time complexityReduce data widthPhysical realisationNeuronNeural network nn

Disclosed are a convolutional neural network processing method and apparatus, a device, and a storage medium. The method comprises: acquiring an original weighting value matrix and an original input neuron matrix of a convolutional neural network; sequentially performing Winograd transformation and quantisation processing on the original weighting value matrix to obtain a target weighting value matrix, and sequentially performing quantisation processing and Winograd transformation on the original input neuron matrix to obtain a target input neuron matrix; and, on the basis of the target weighting value matrix and the target input neuron matrix, obtaining an output neuron matrix of the convolutional neural network.

Owner:BIGO TECH PTE LTD

Field programmable gate array (FPGA) based method for achieving synchronous detection of oversampling Golay sequence

ActiveCN103023529BExcellent autocorrelation performanceReduce occupancyTransmissionMultiplexingShift register

Owner:TOEC TECH