Patents

Literature

36 results about "Return address stack" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

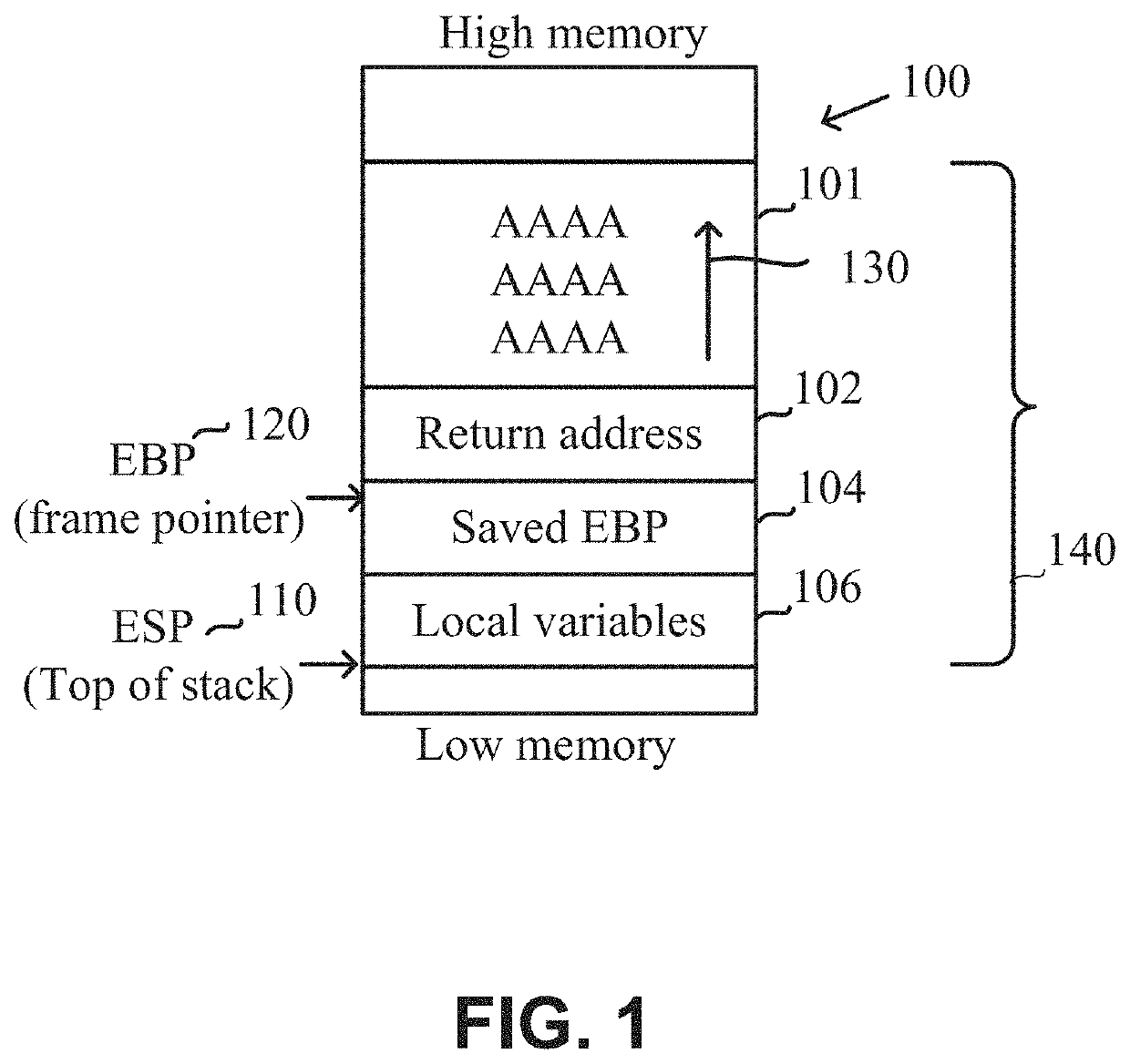

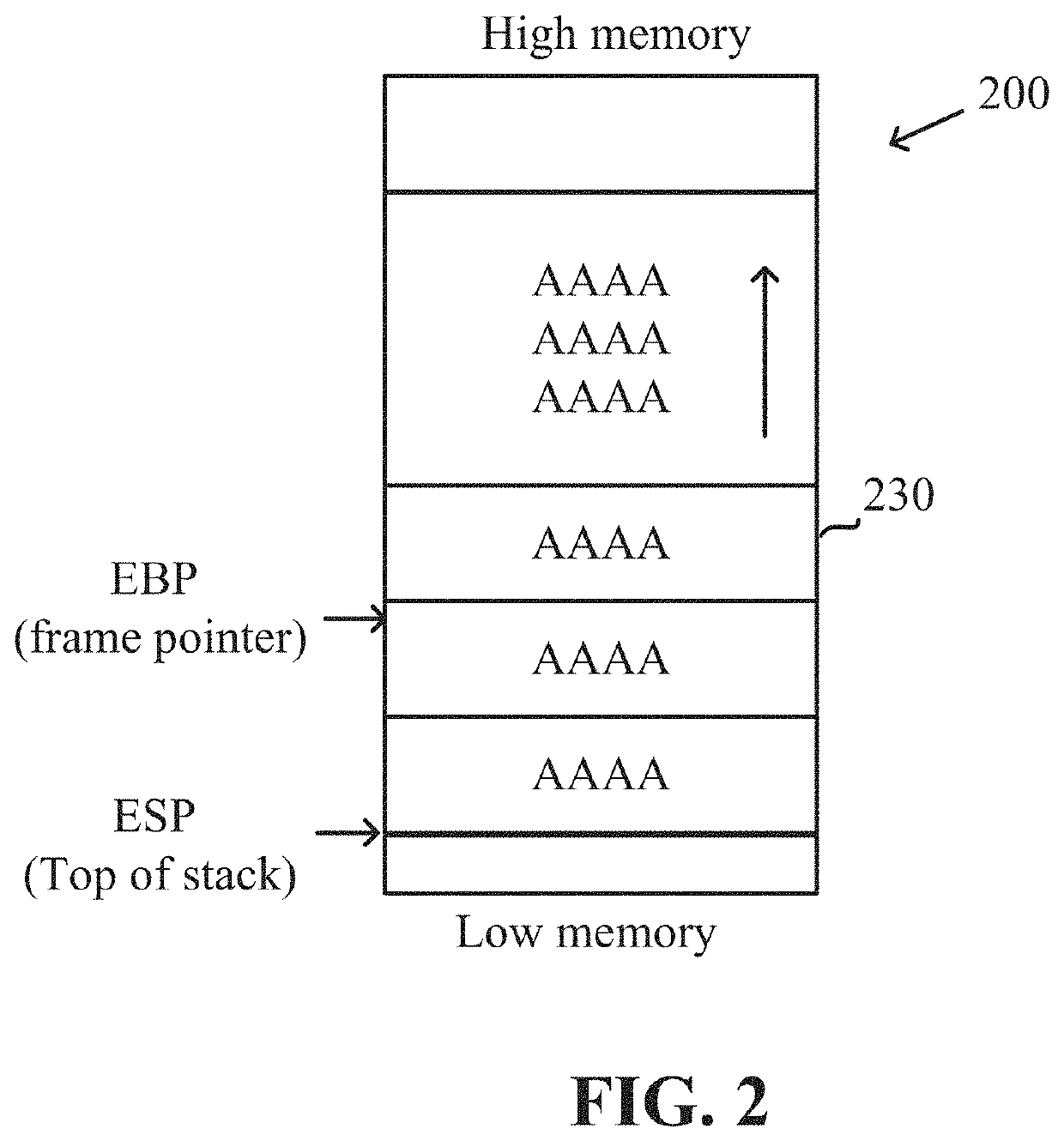

The function return address is placed on the stack by the x86 CALL instruction, which stores the current value of the EIP register. Then, the frame pointer that is the previous value of the EBP register is placed on the stack.

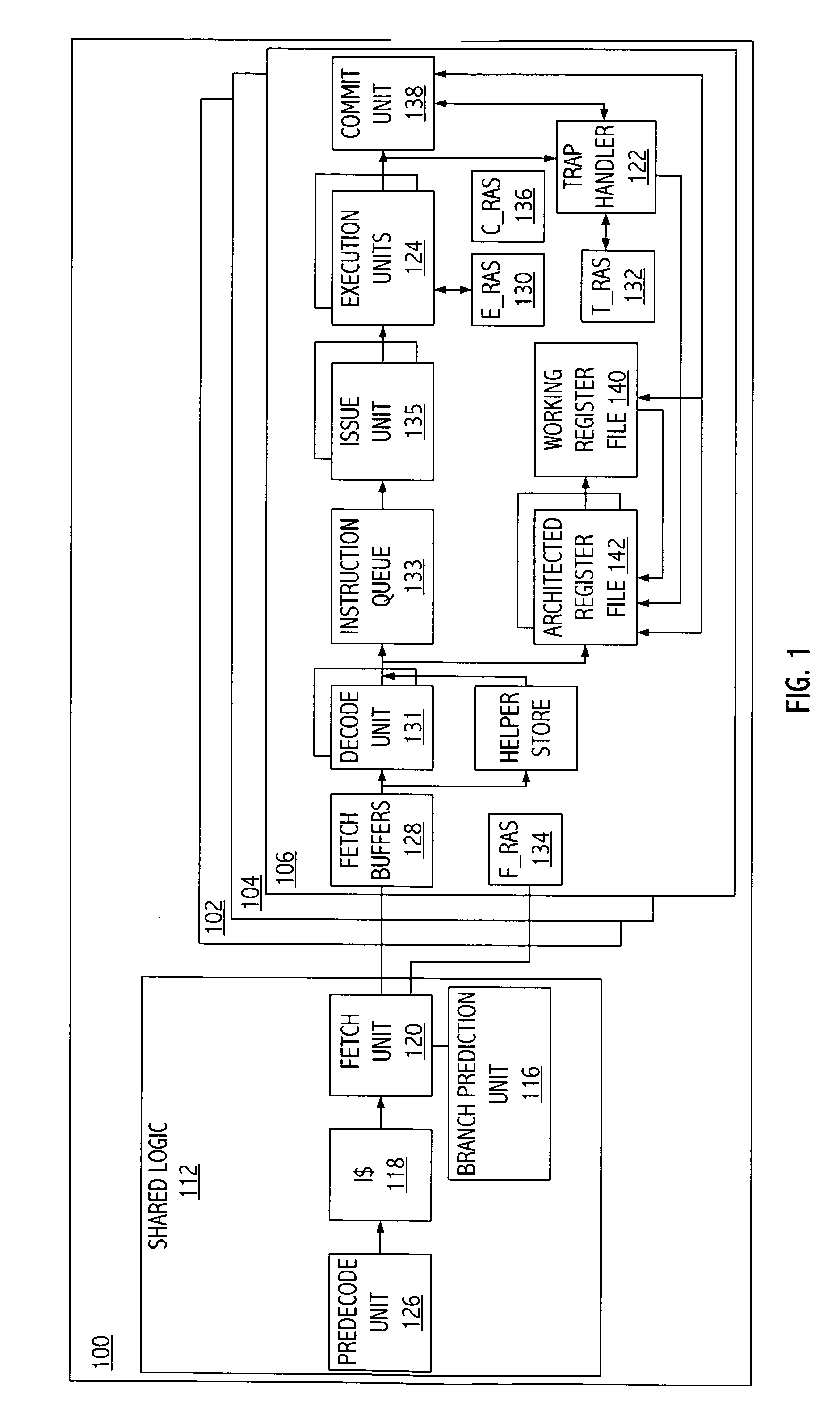

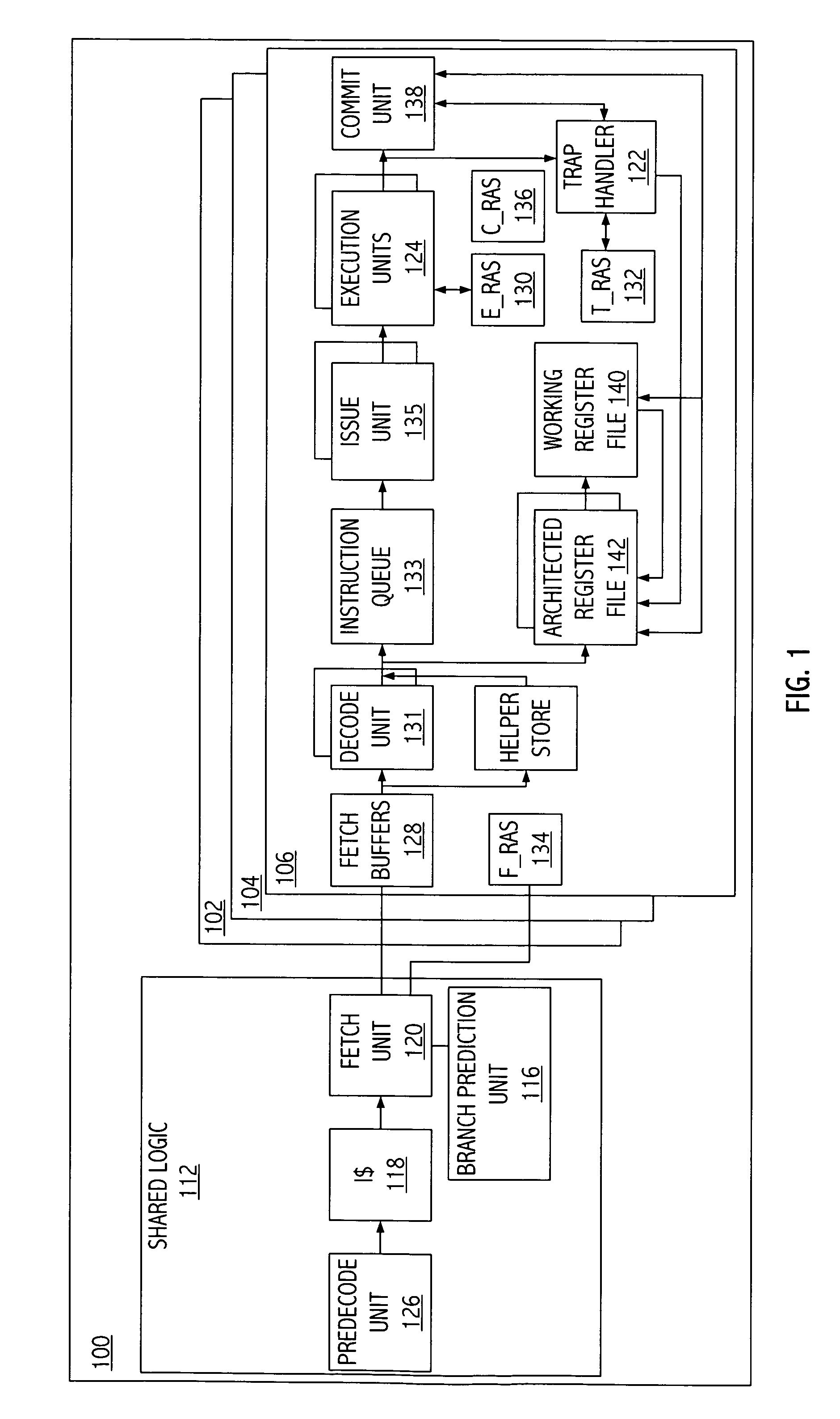

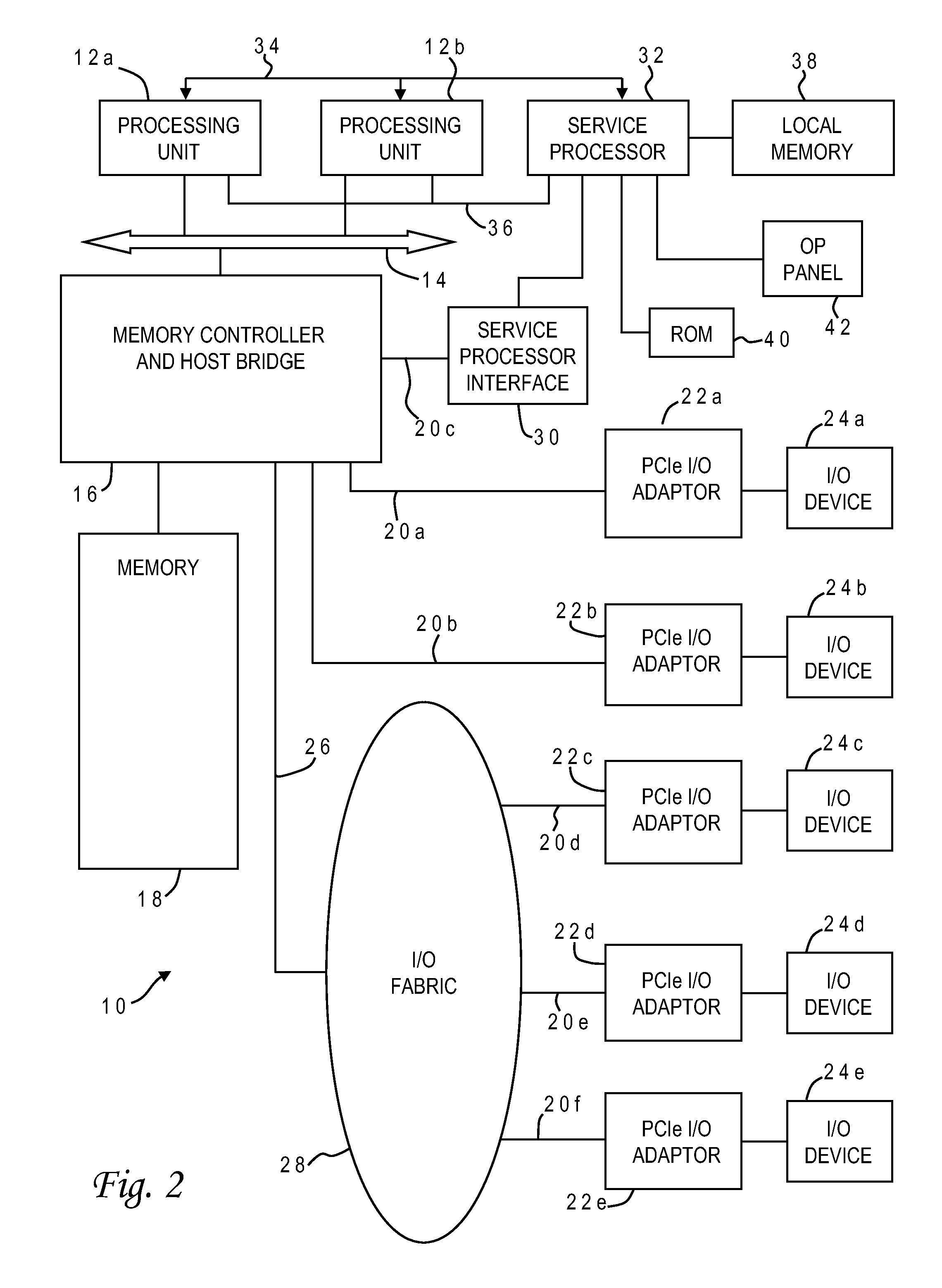

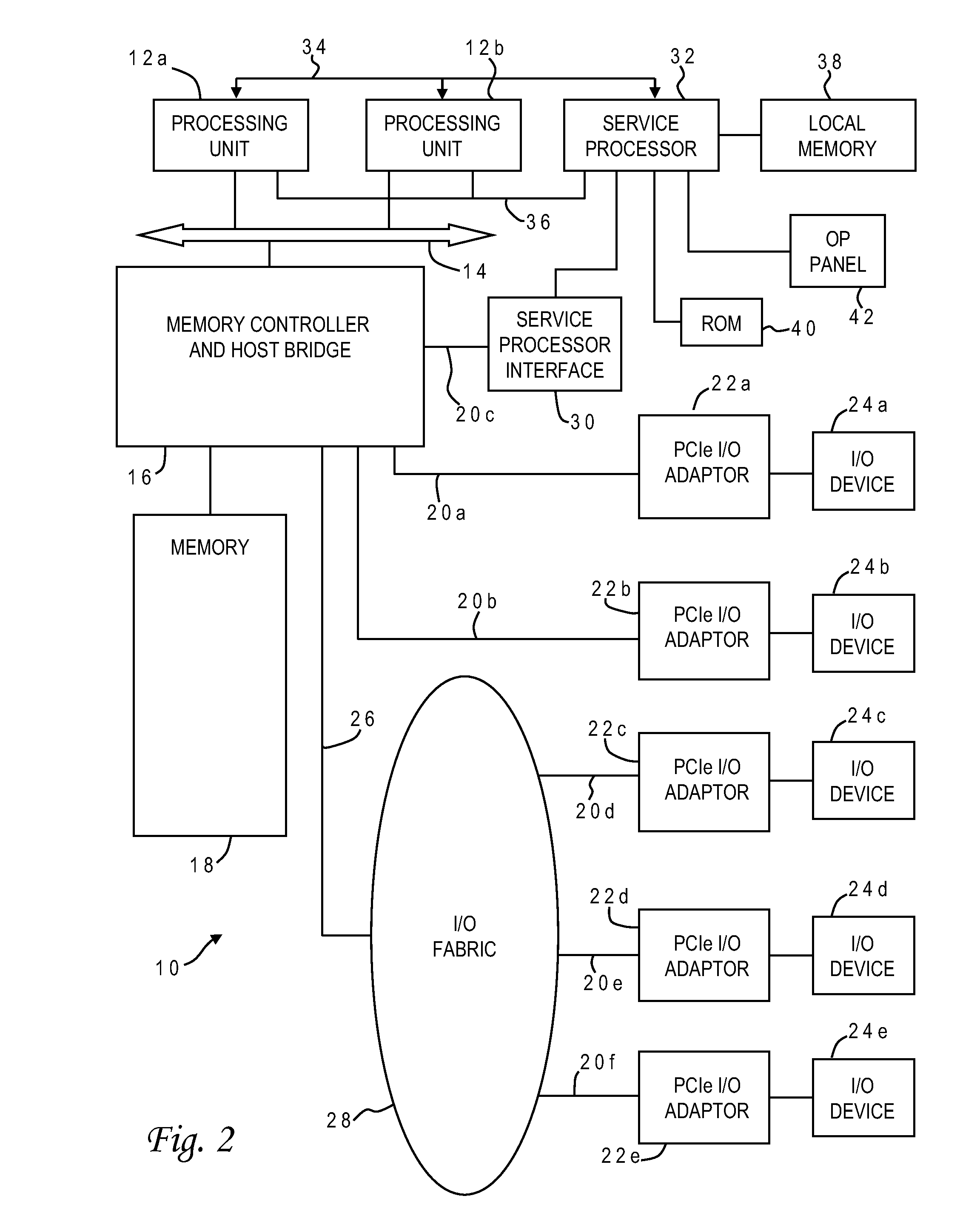

System and method of maintaining and utilizing multiple return stack buffers

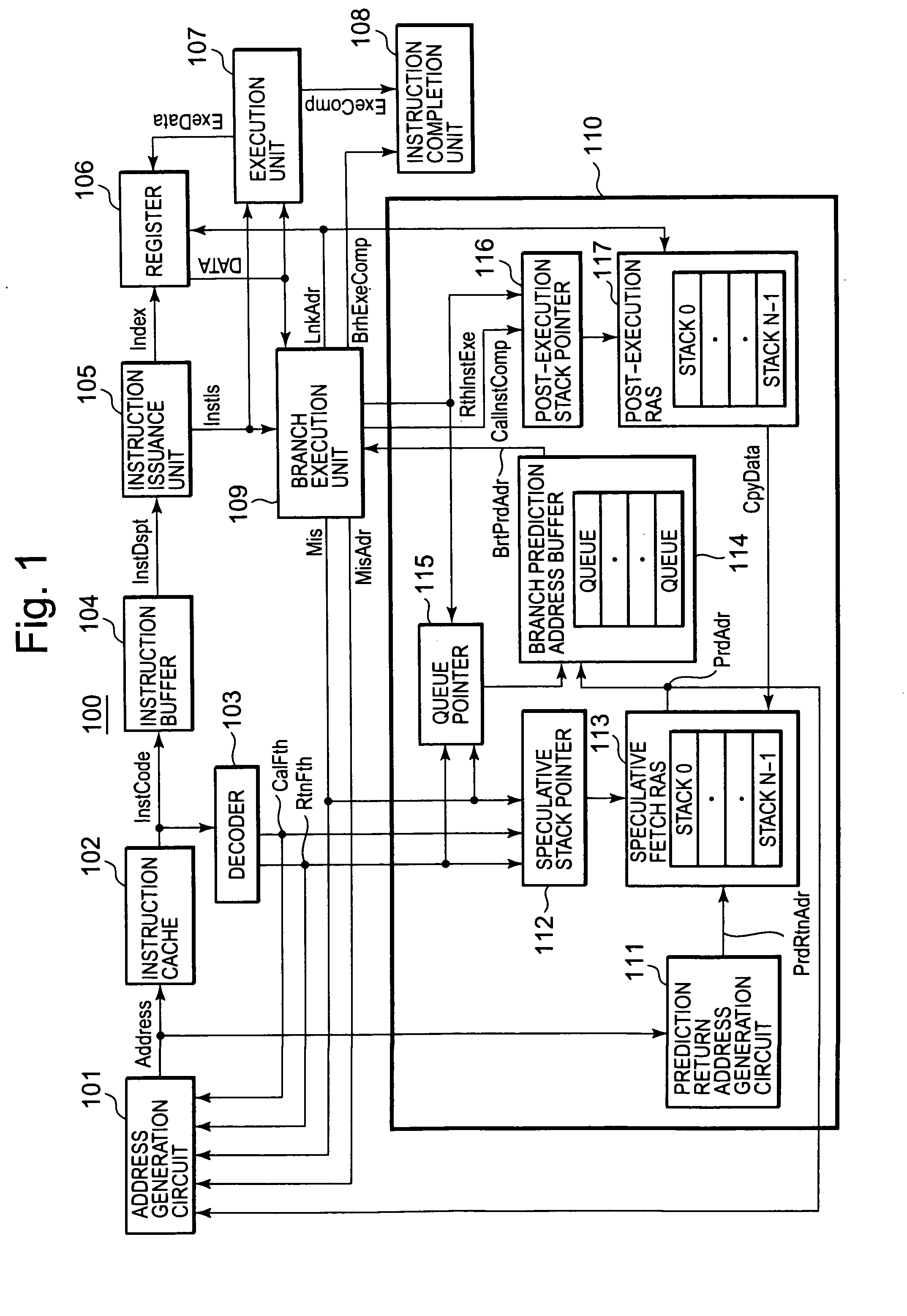

InactiveUS6374350B1Digital computer detailsConcurrent instruction executionReturn address stackInstruction pipeline

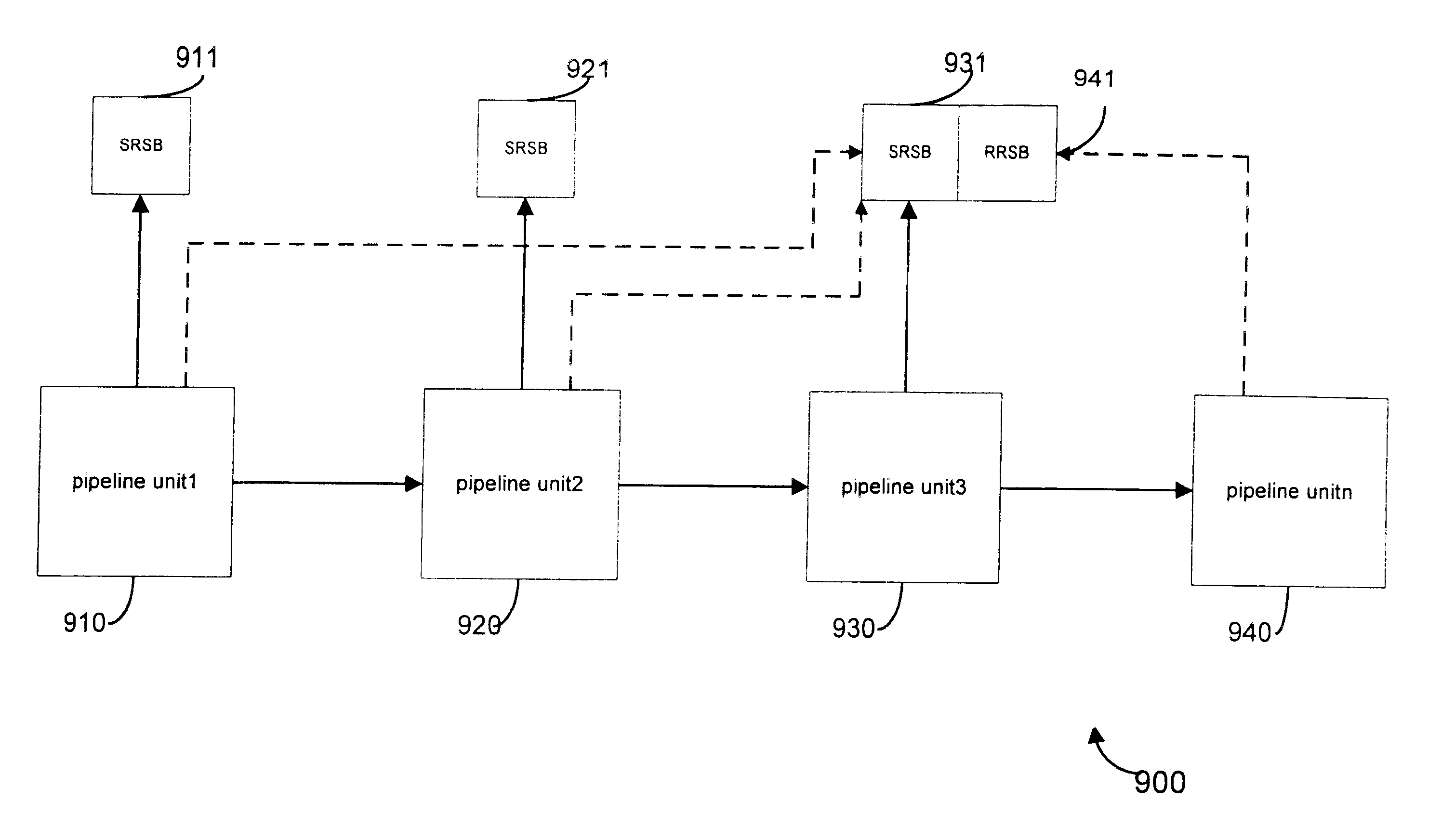

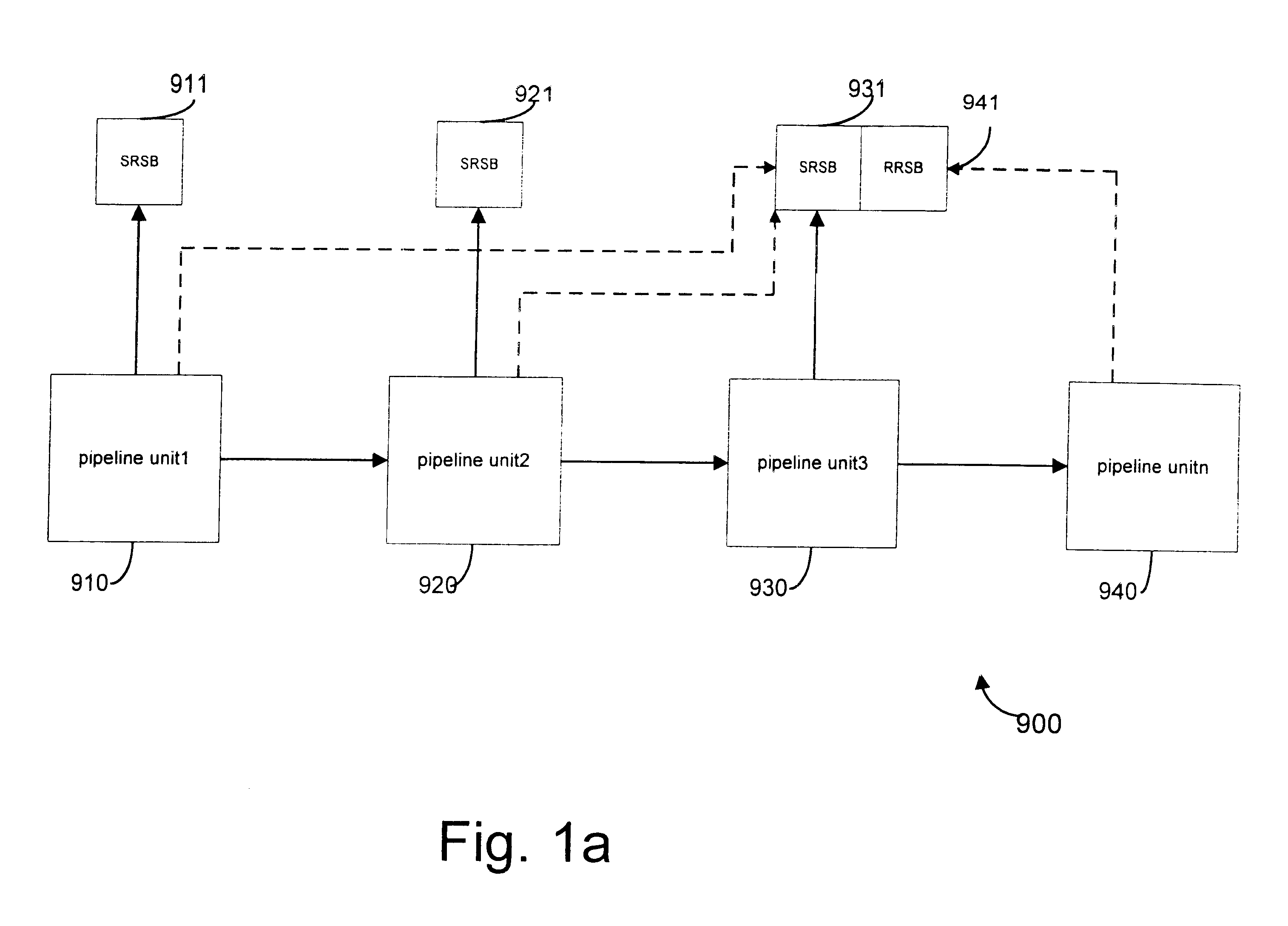

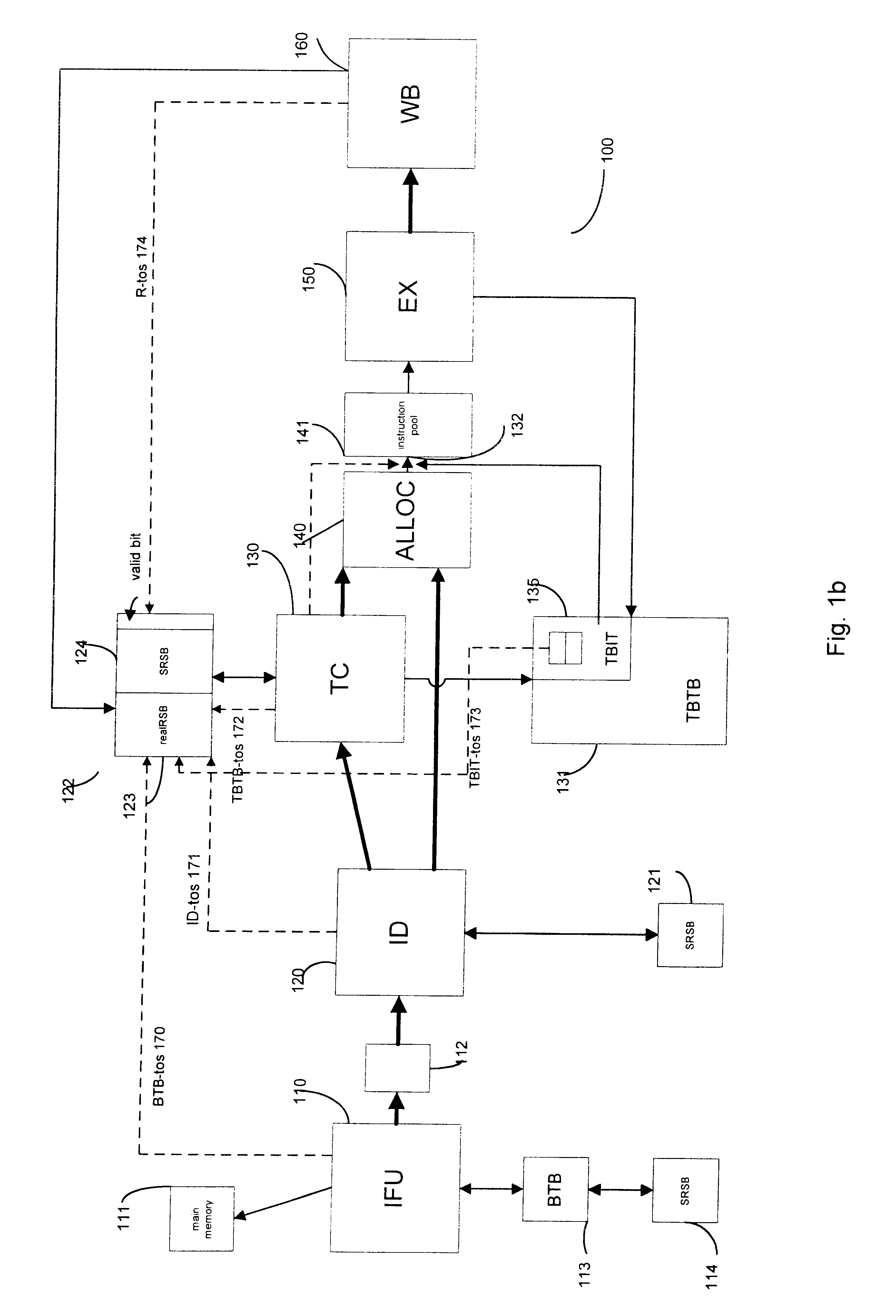

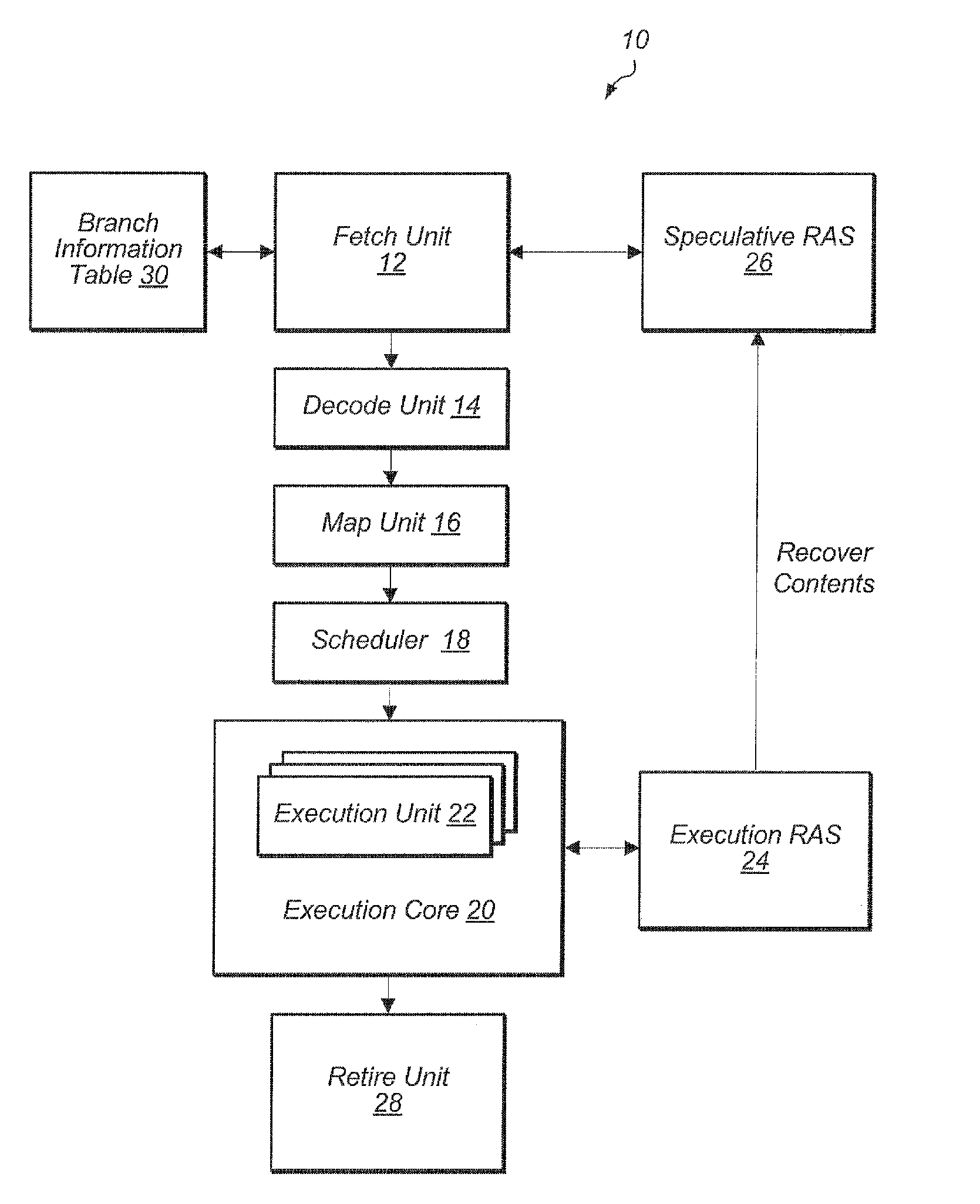

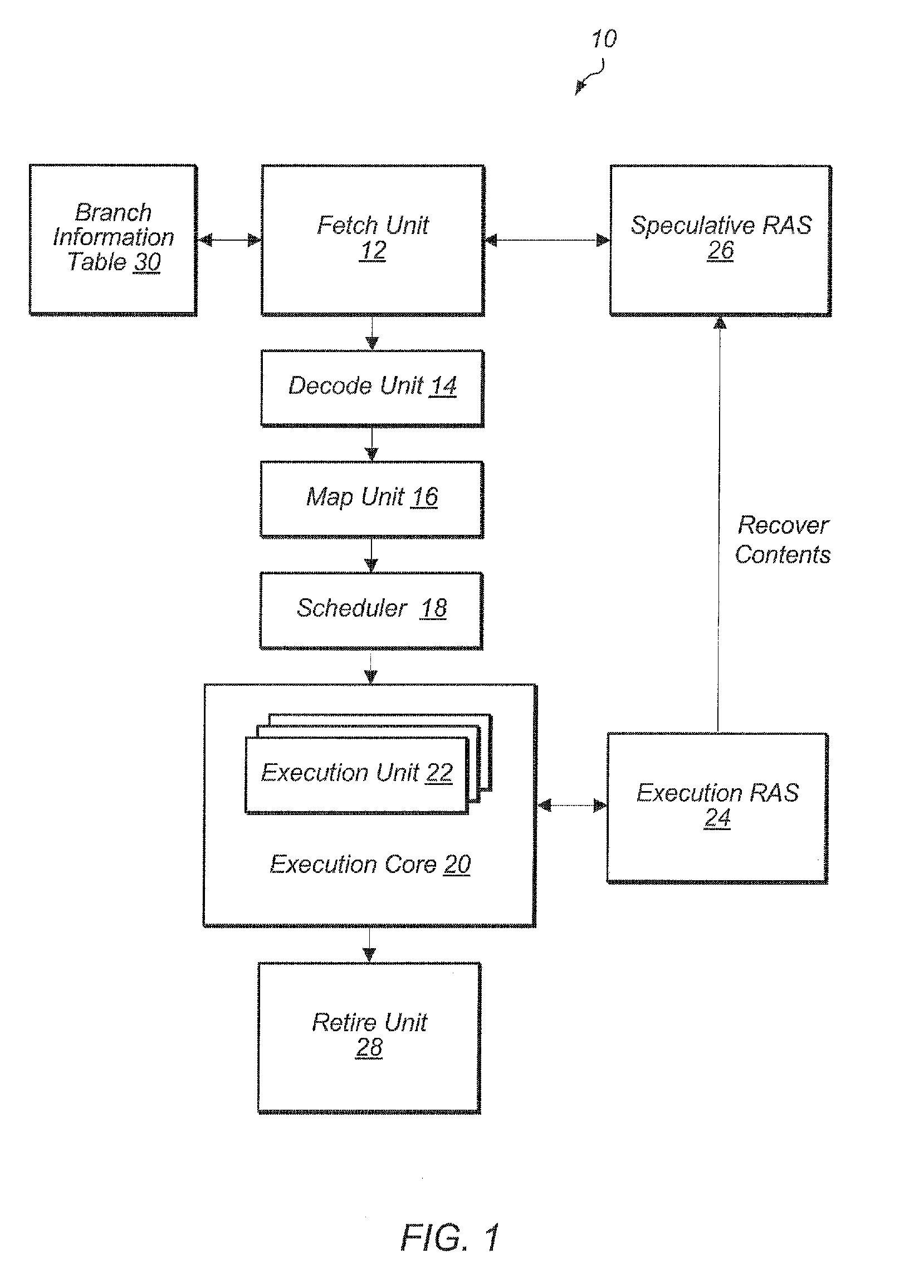

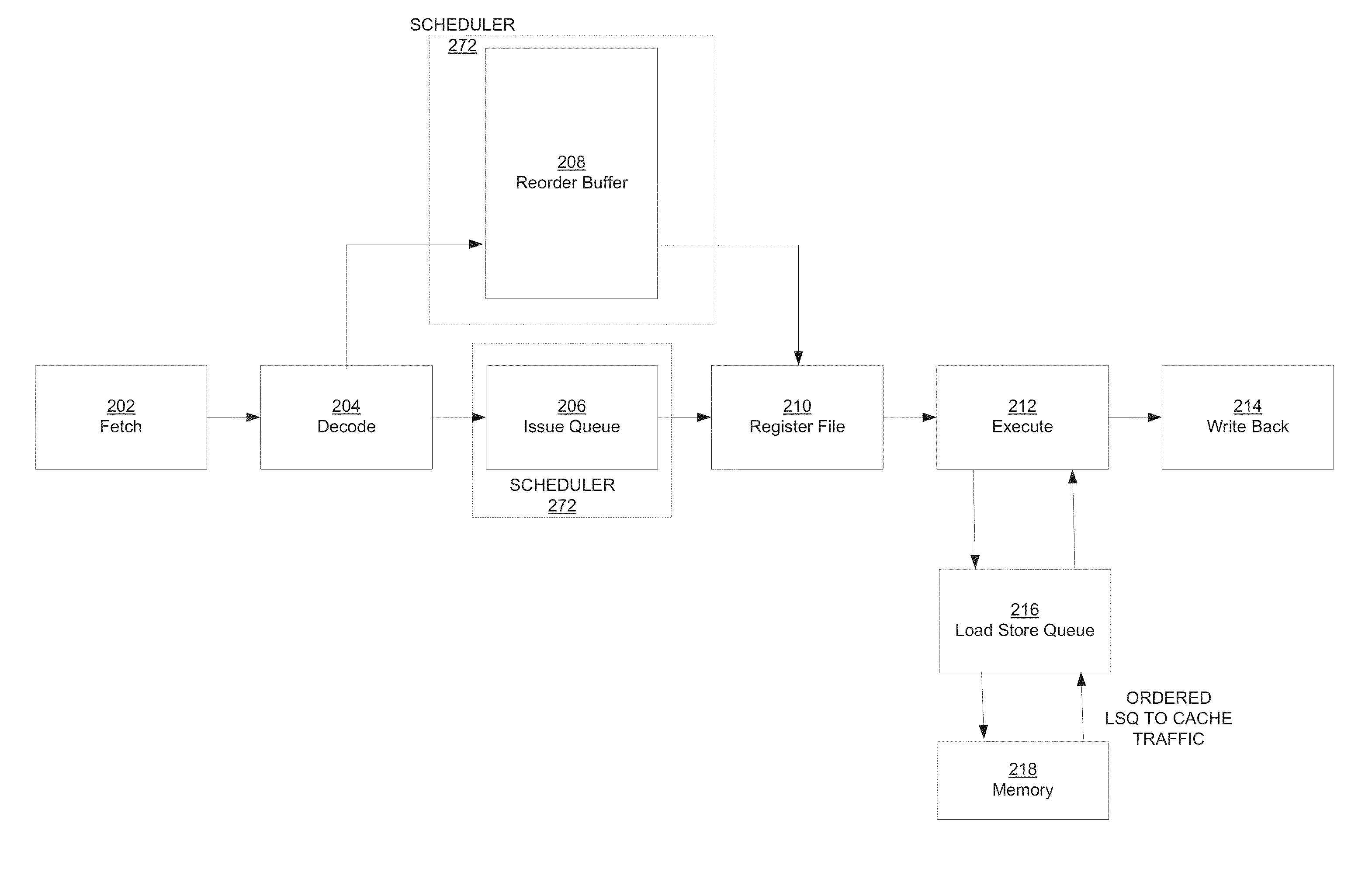

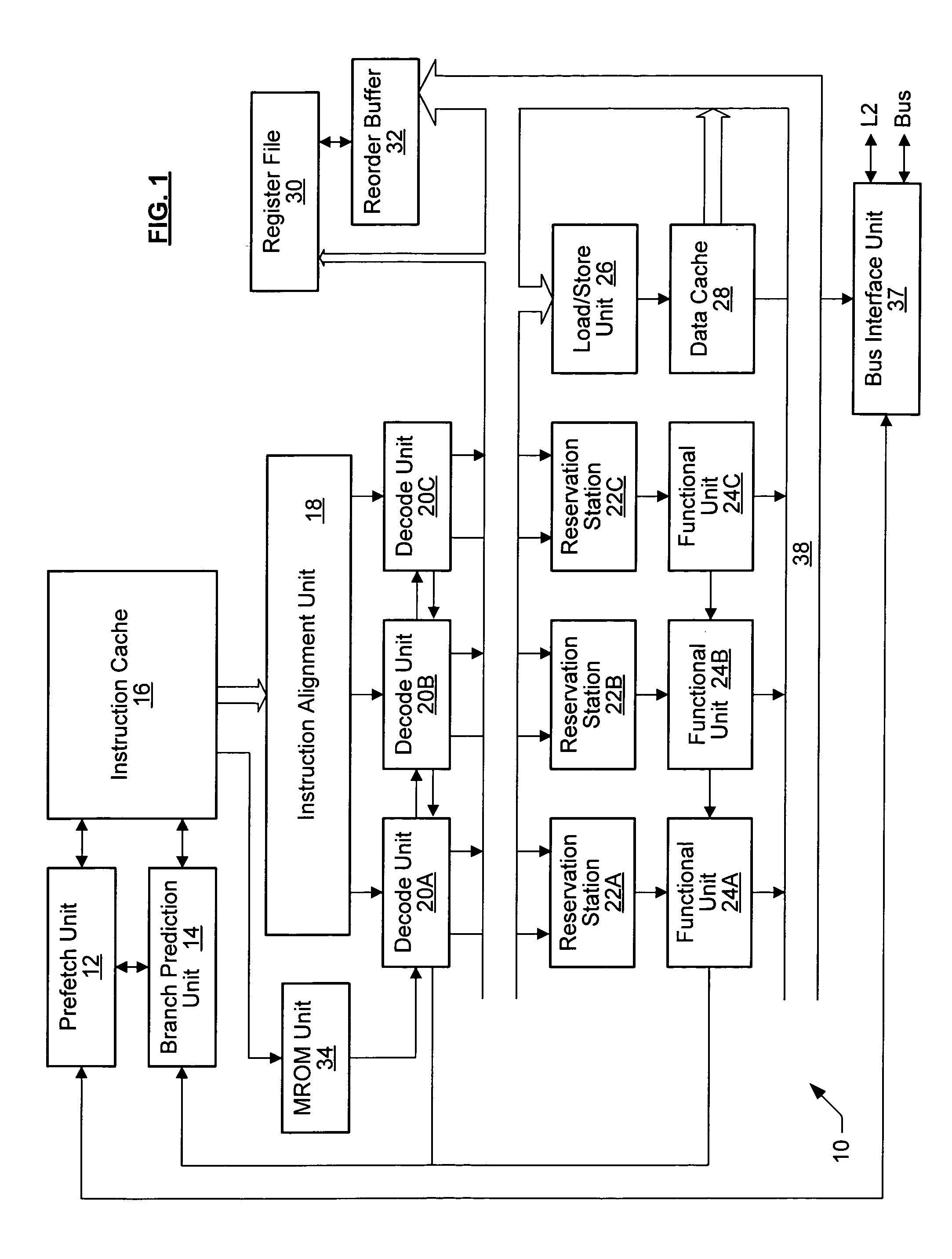

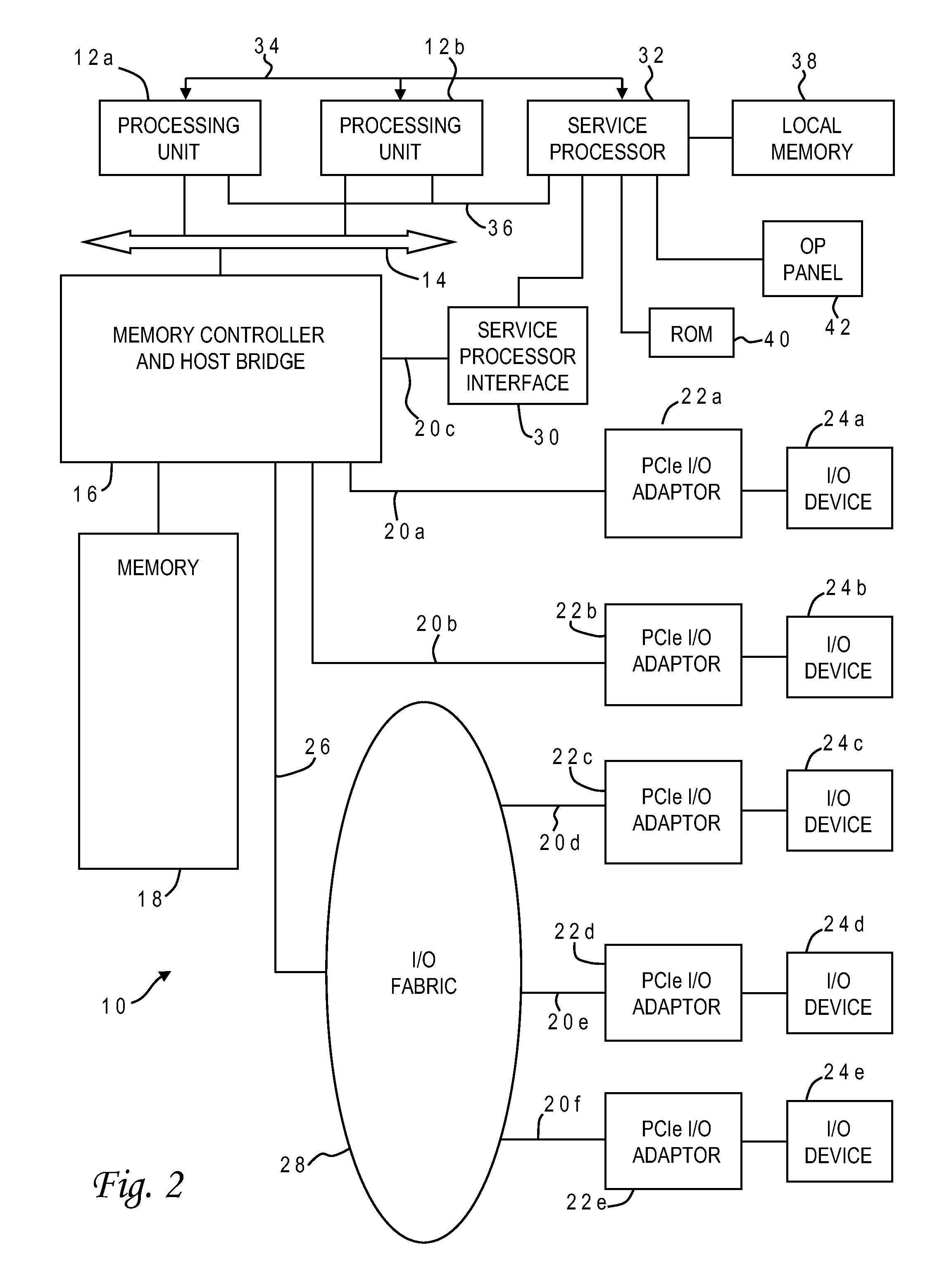

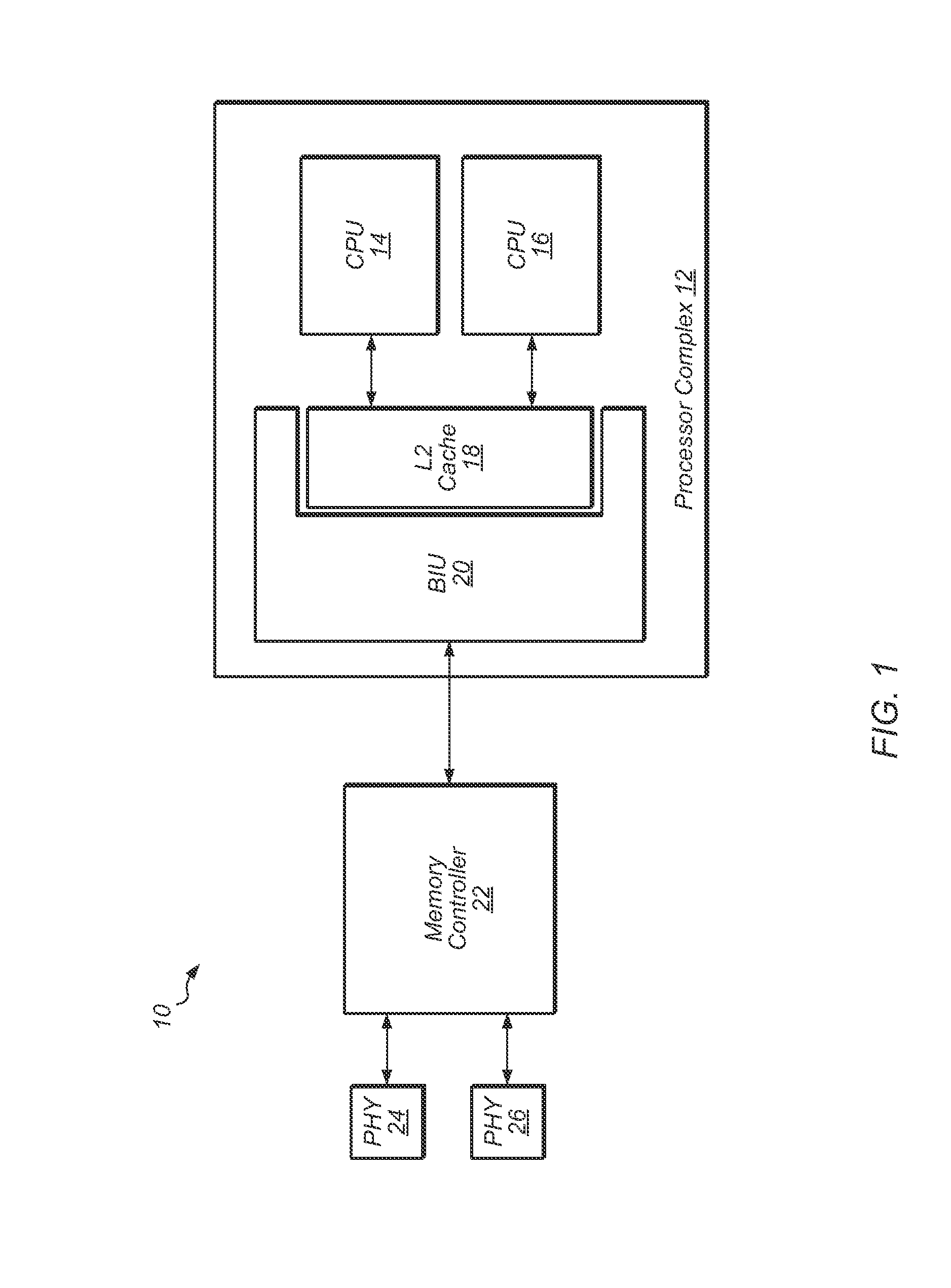

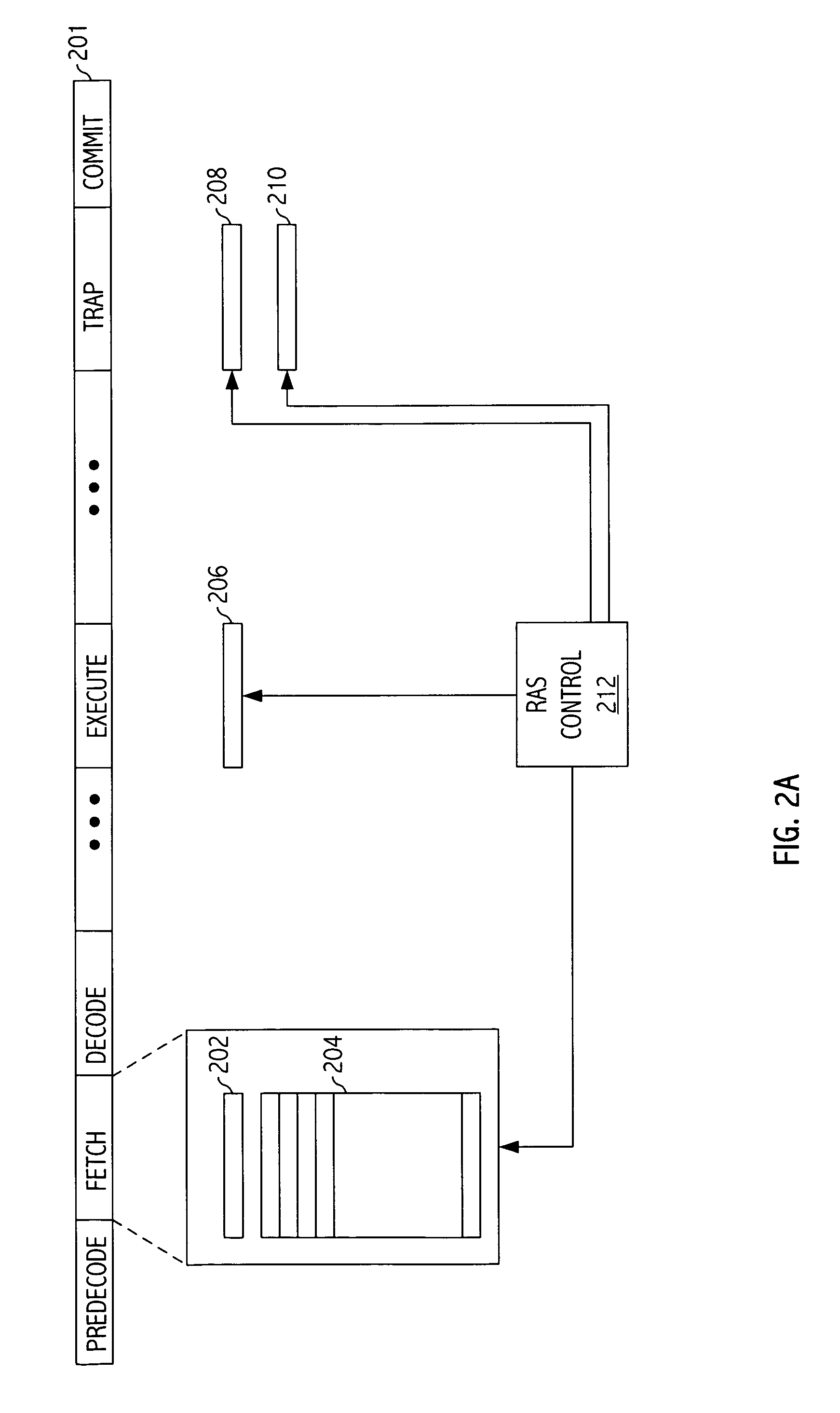

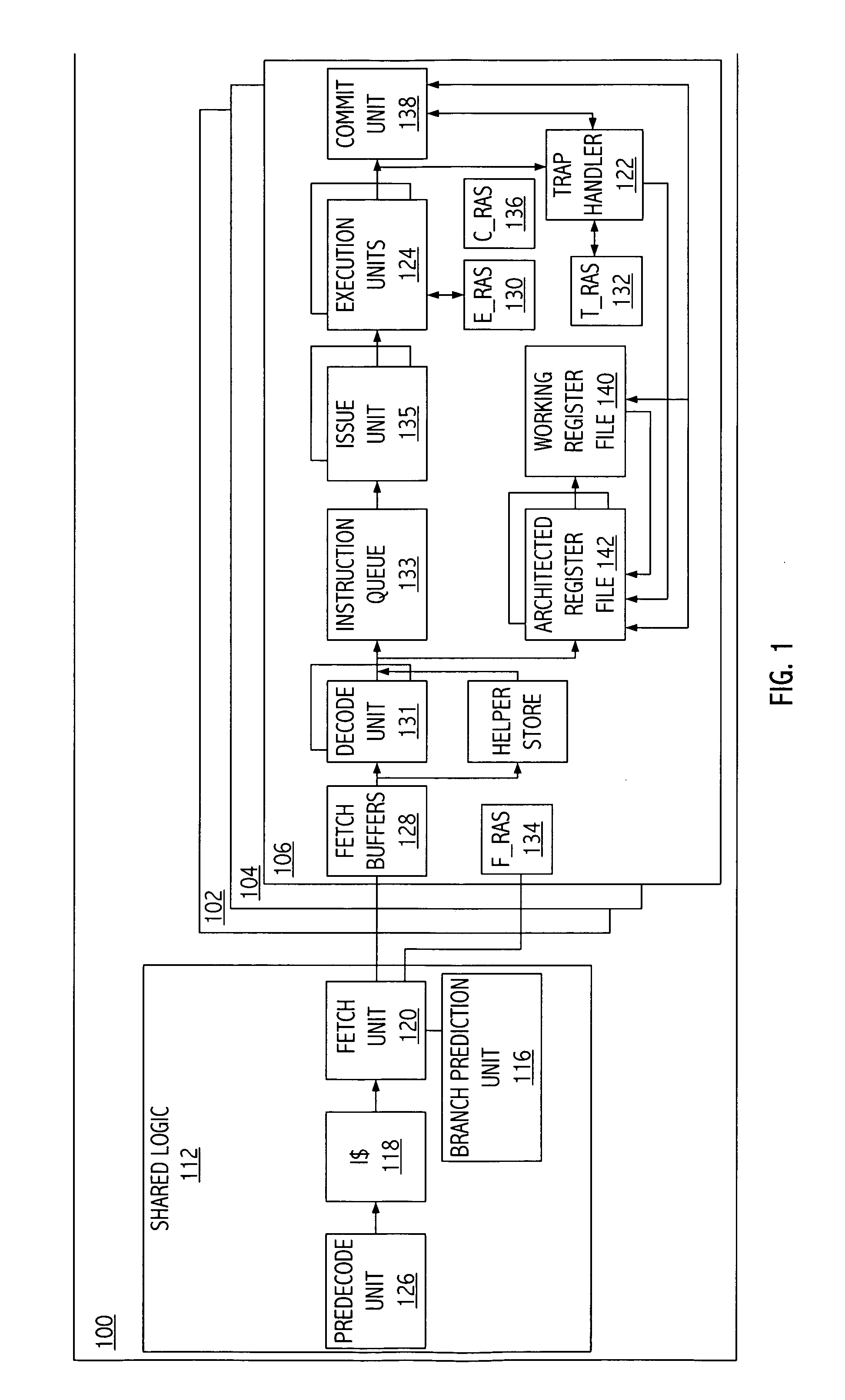

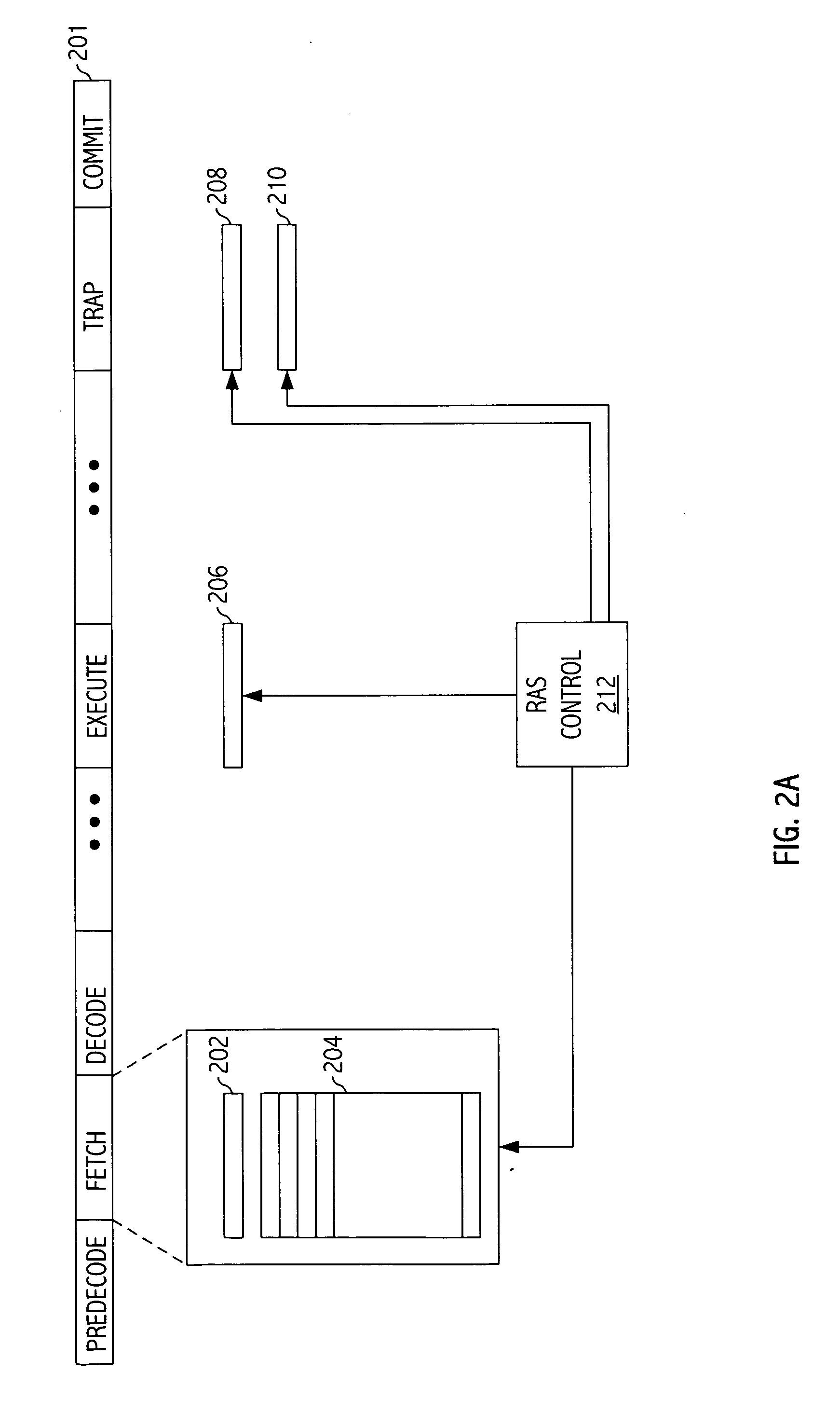

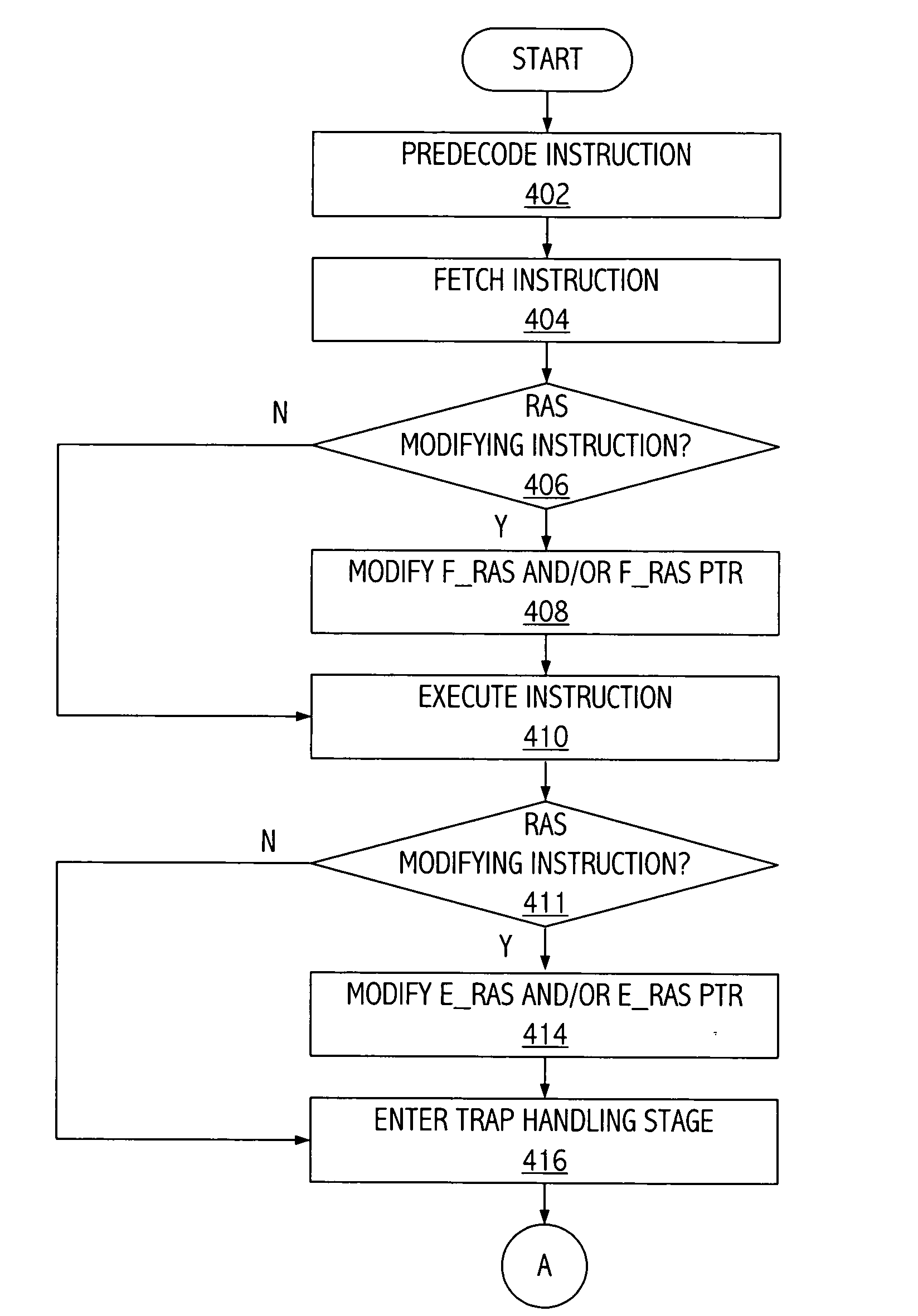

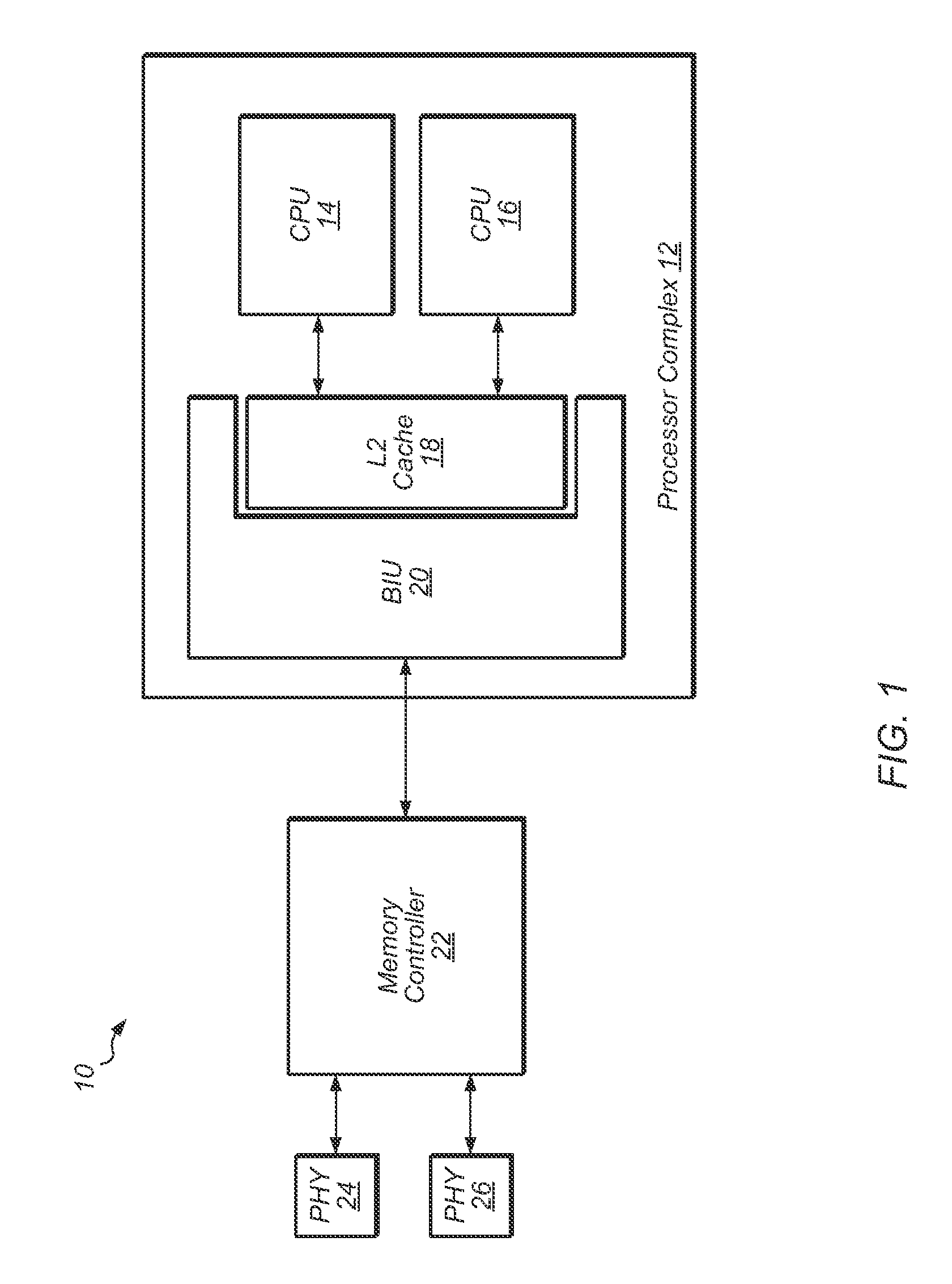

An instruction pipeline in a microprocessor is provided. The instruction pipeline includes a plurality of pipeline units, each of the plurality of pipeline units processing a plurality of instructions. At least two of the plurality of pipeline units are a source of at least some of the instructions for the pipeline. The pipeline further includes at least two speculative return address stacks, each of the speculative return address stacks coupled is coupled to at least one of the instruction source units. Each of the speculative return return address stacks are capable of storing at least two speculative return addresses.

Owner:INTEL CORP

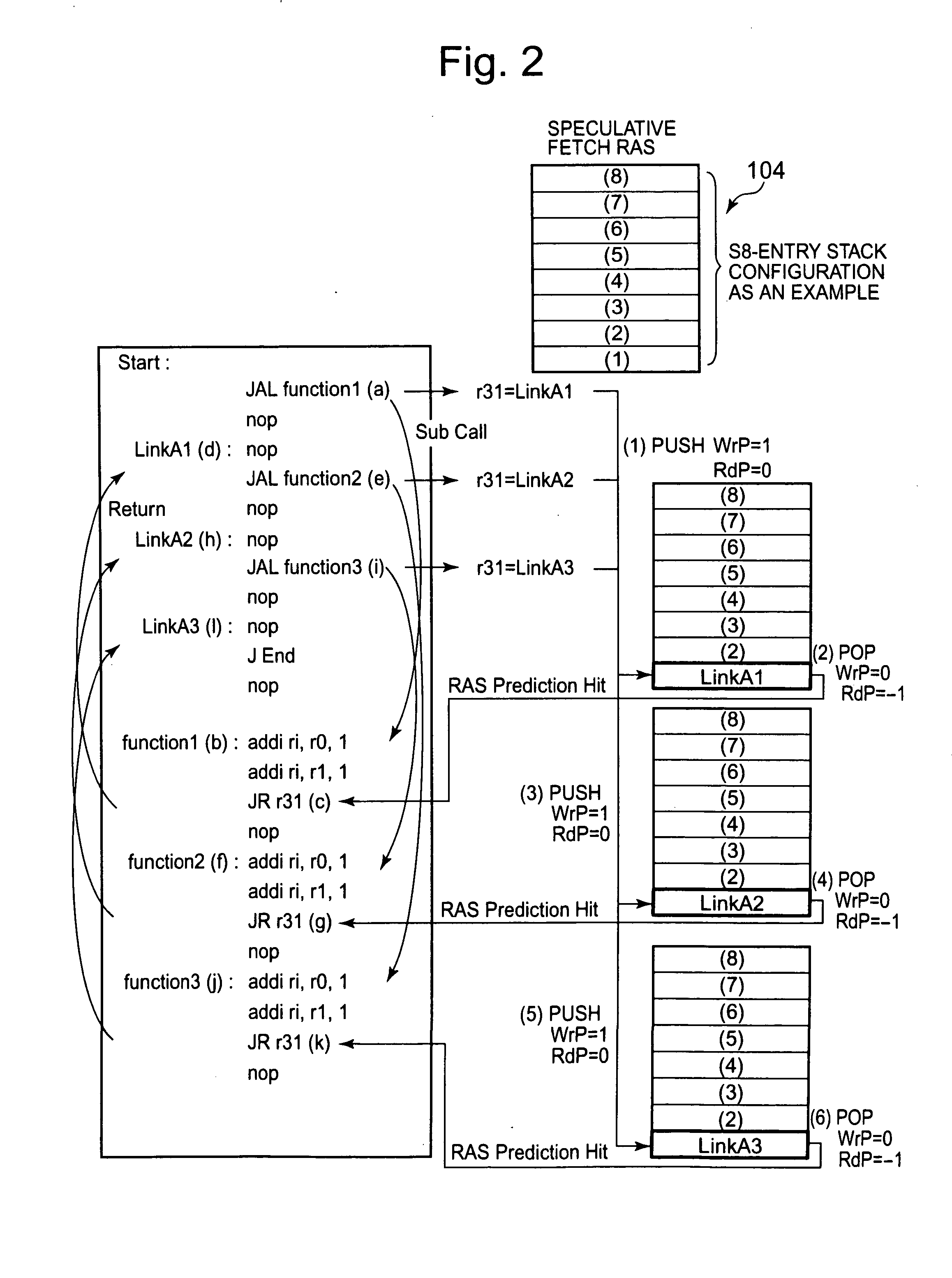

Branch prediction control device having return address stack and method of branch prediction

InactiveUS20080301420A1Improve accuracyDigital computer detailsConcurrent instruction executionInformation processingReturn address stack

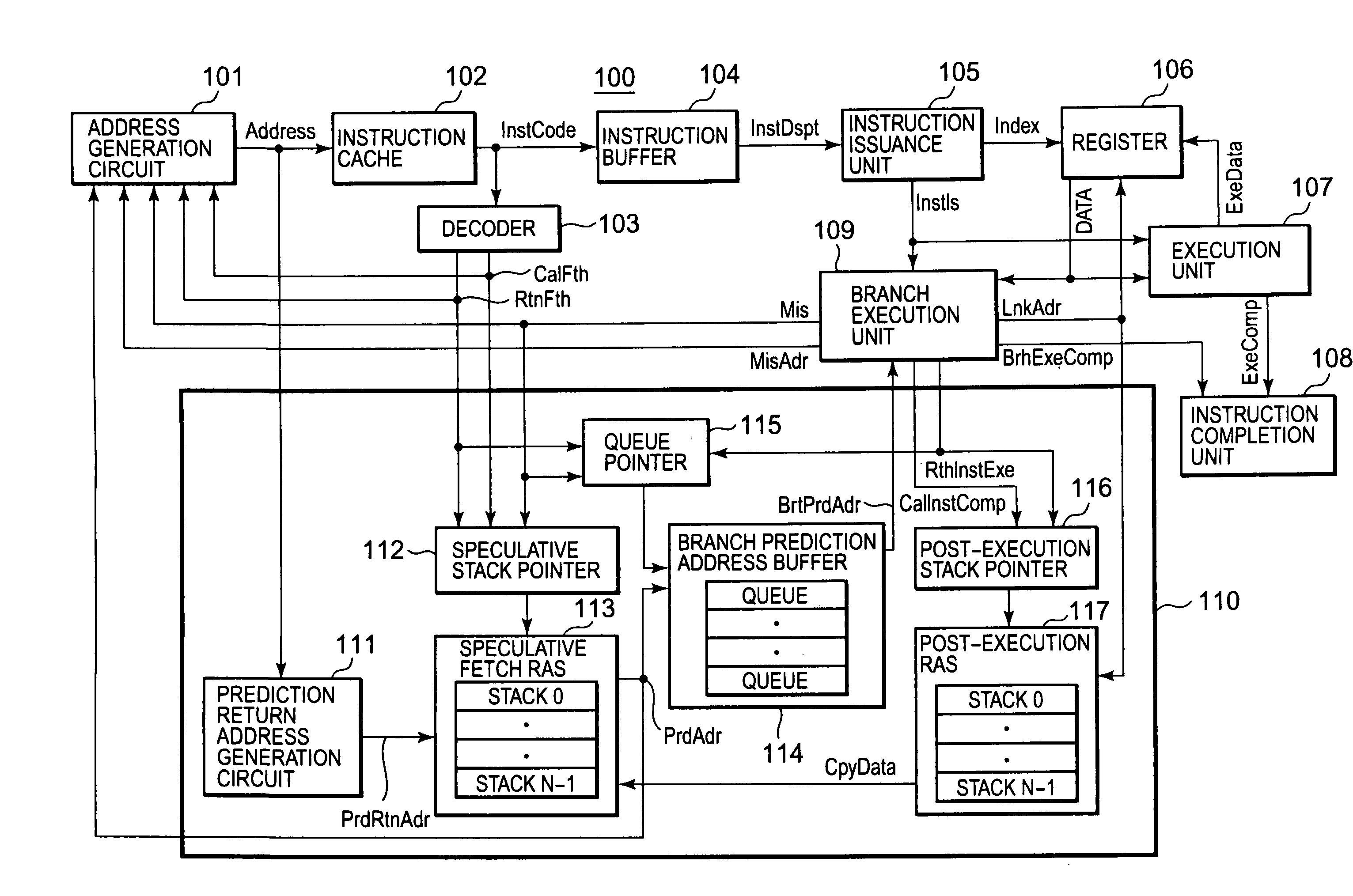

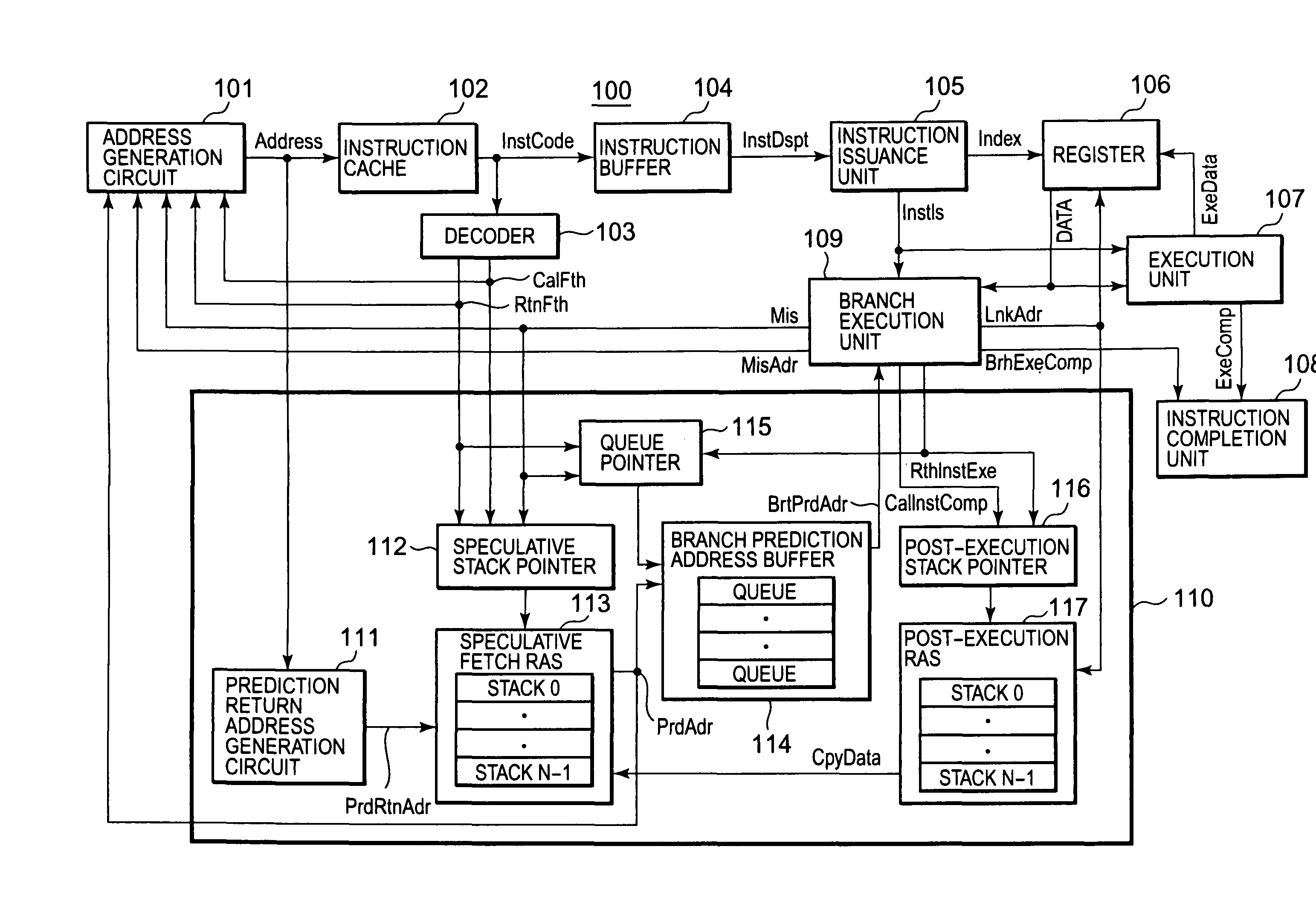

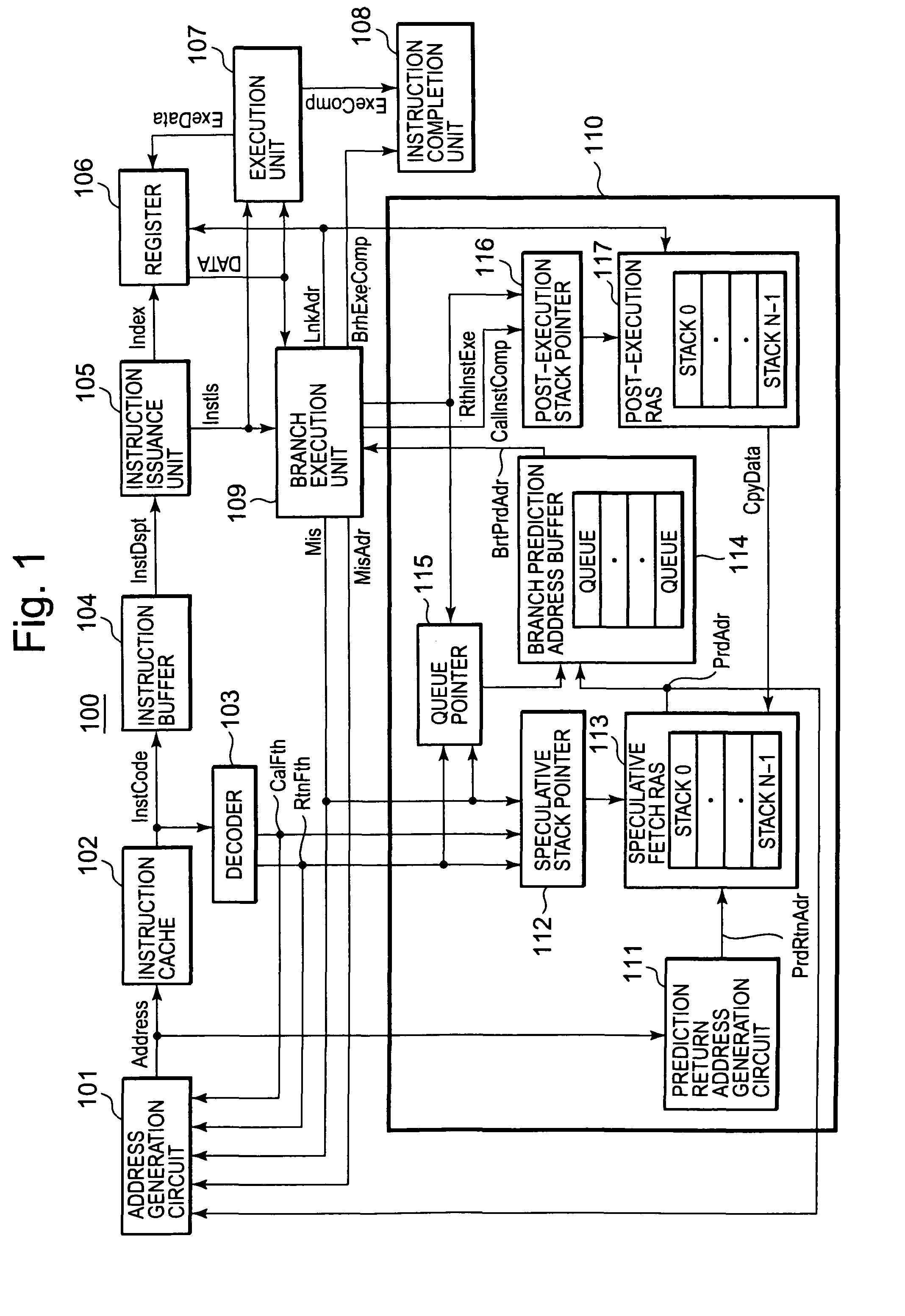

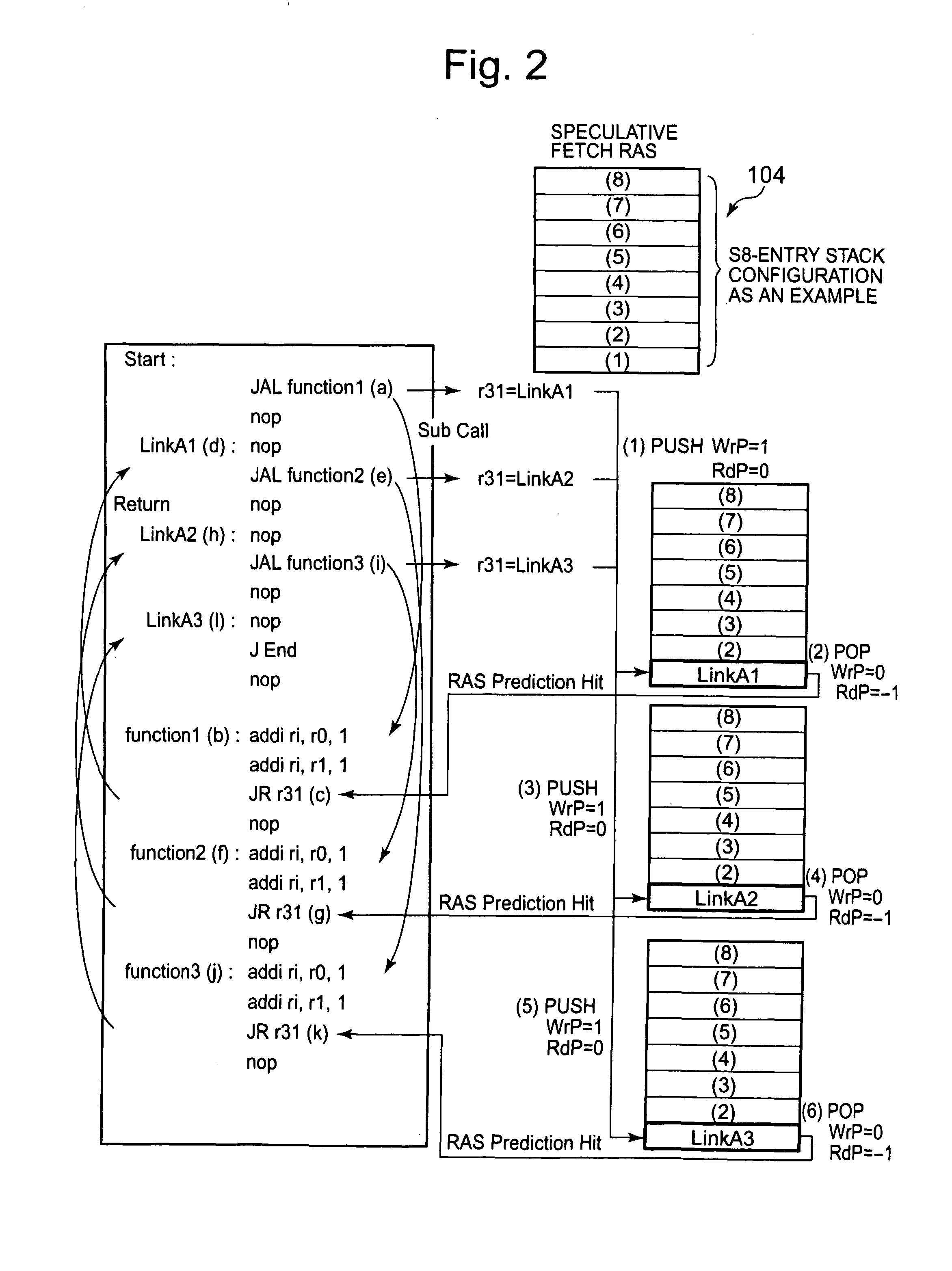

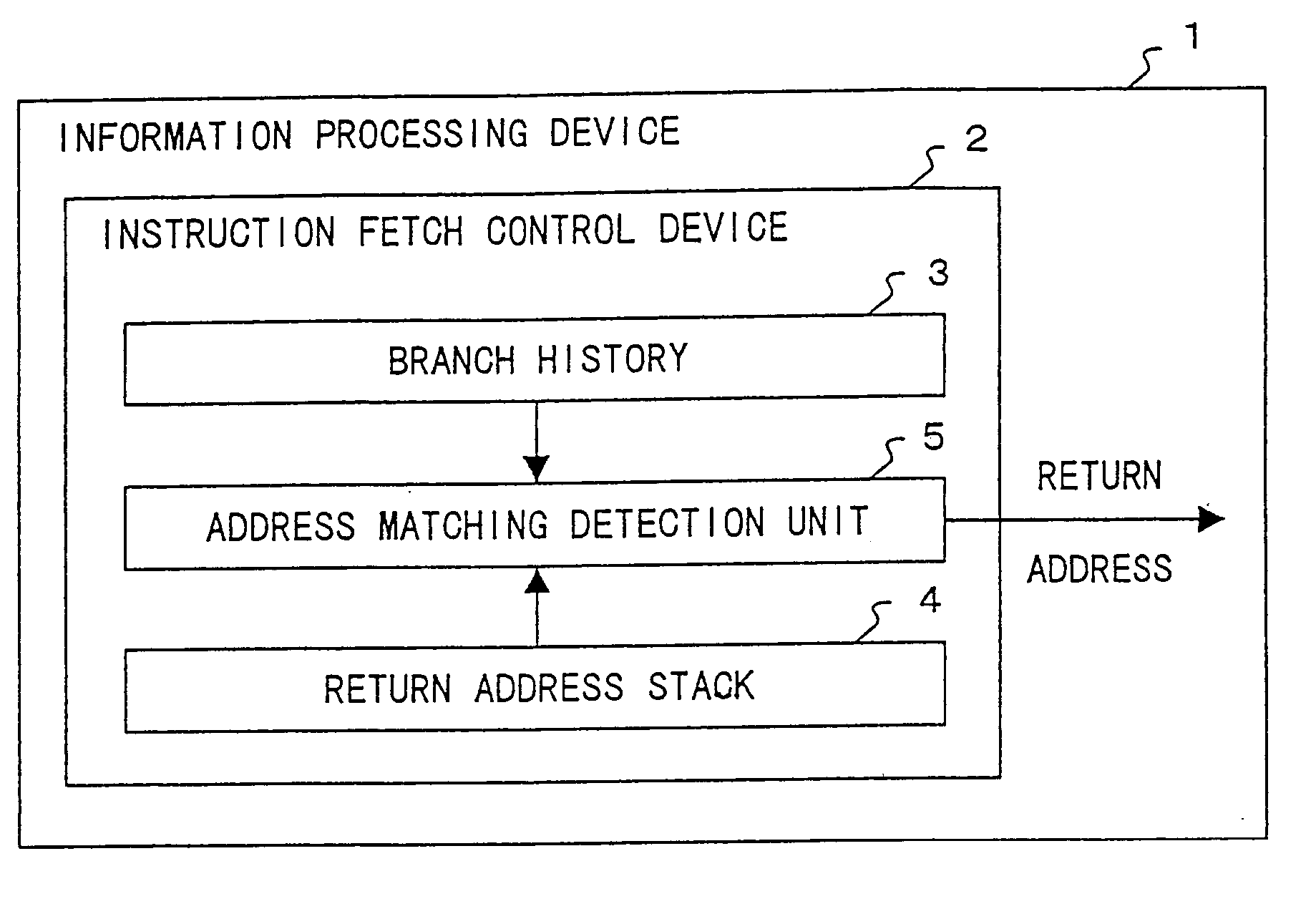

A branch prediction control device, in an information processing unit which performs a pipeline process, generates a branch prediction address used for verification of an instruction being speculatively executed. The branch prediction control device includes a first return address storage unit storing the prediction return address, a second return address storage unit storing a return address to be generated depending on an execution result of the call instruction, and a branch prediction address storage unit sending a stored prediction return address as a branch prediction address and storing the sent branch prediction address. When the branch prediction address differs from a return address, which is generated after executing a branch instruction or a return instruction, contents stored in the second return address storage unit are copied to the first return address storage unit.

Owner:RENESAS ELECTRONICS CORP

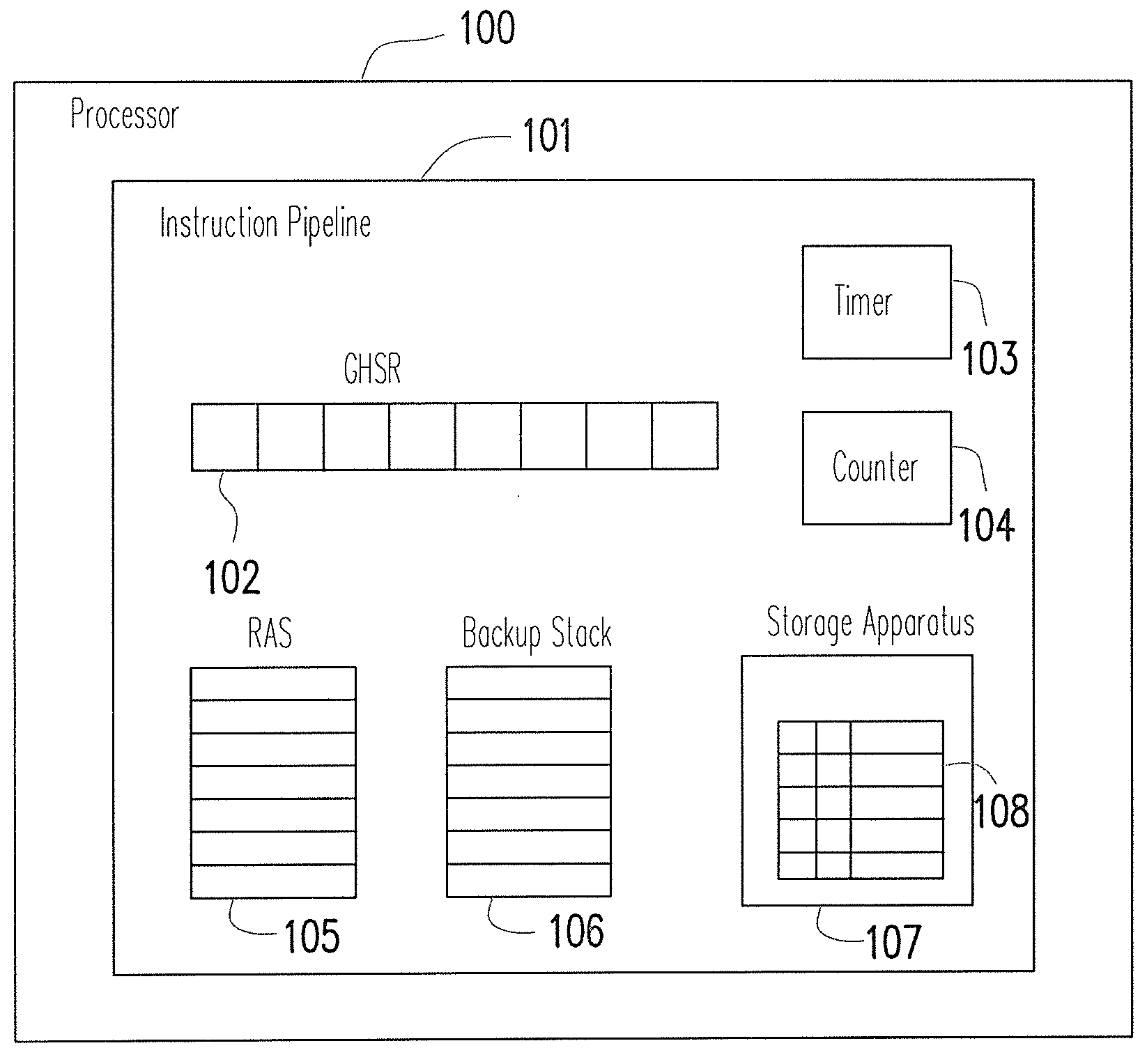

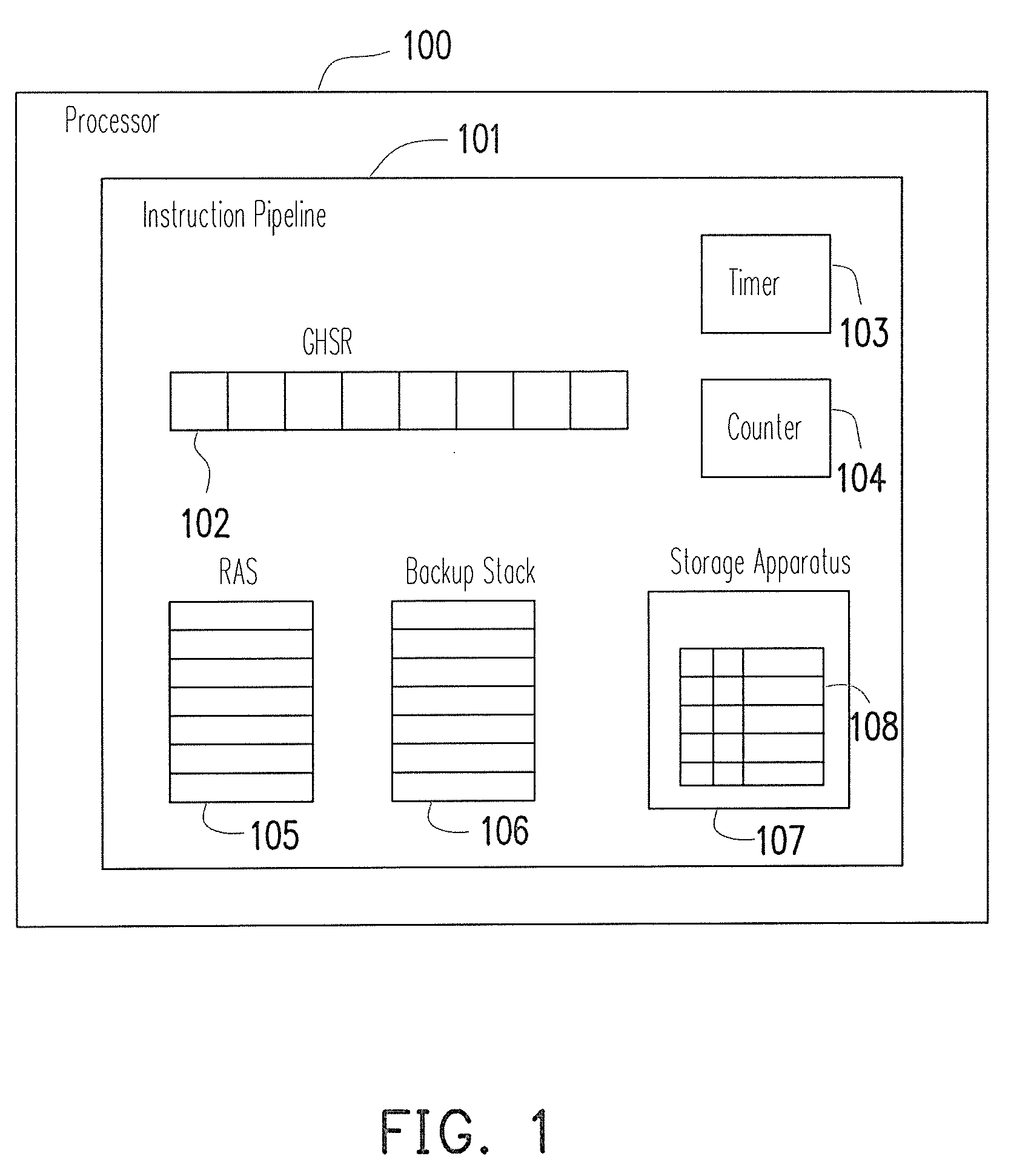

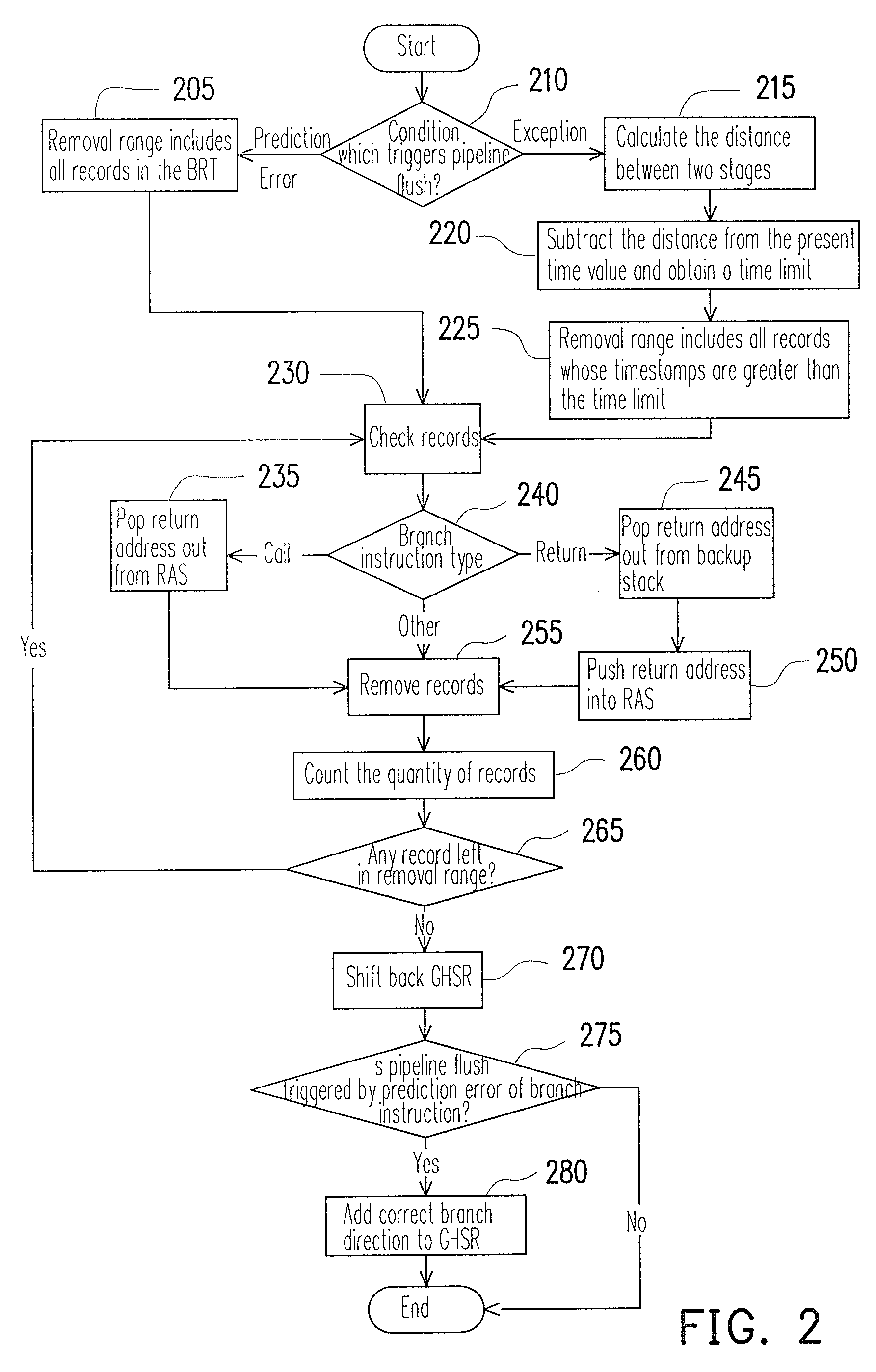

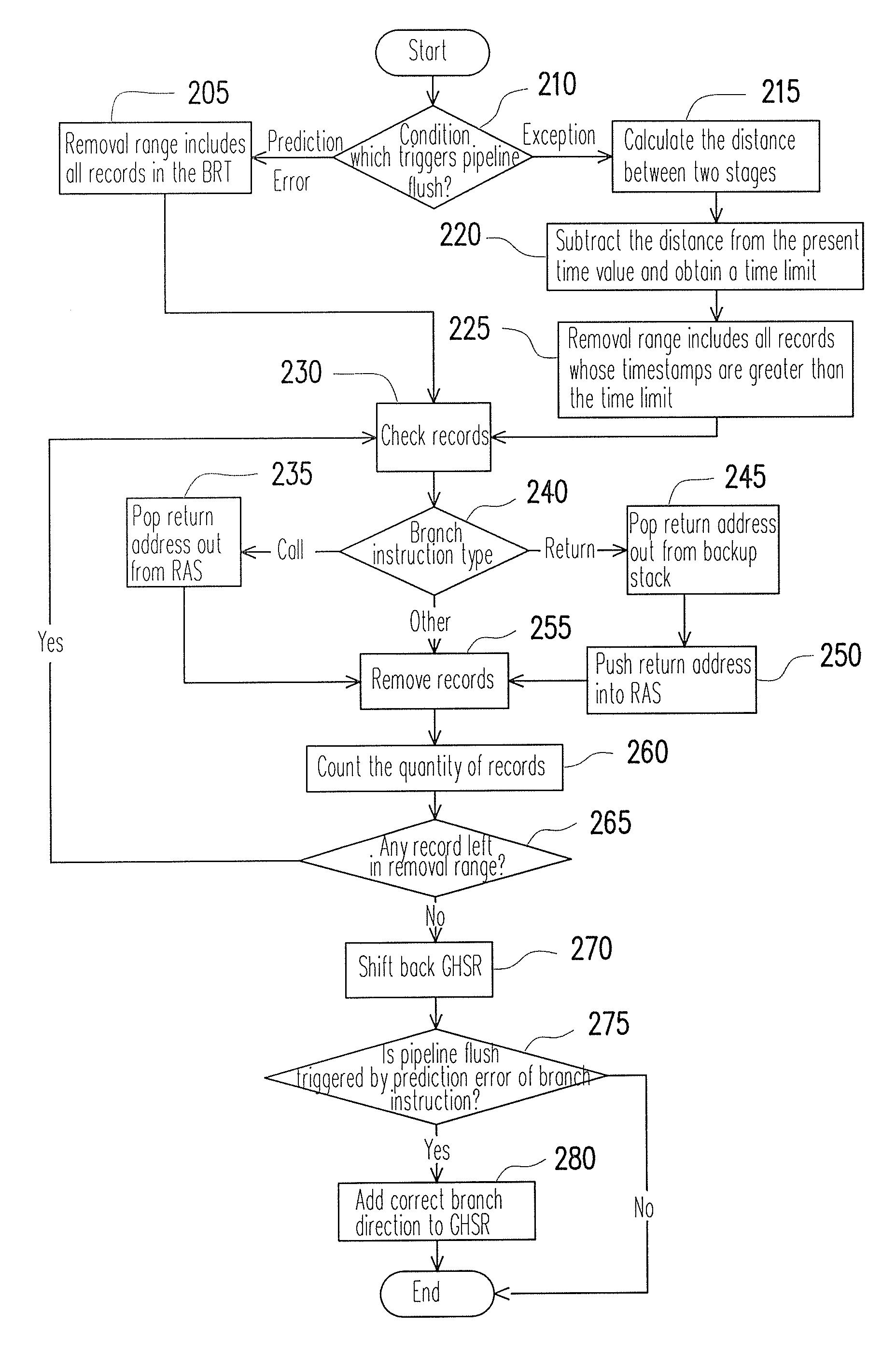

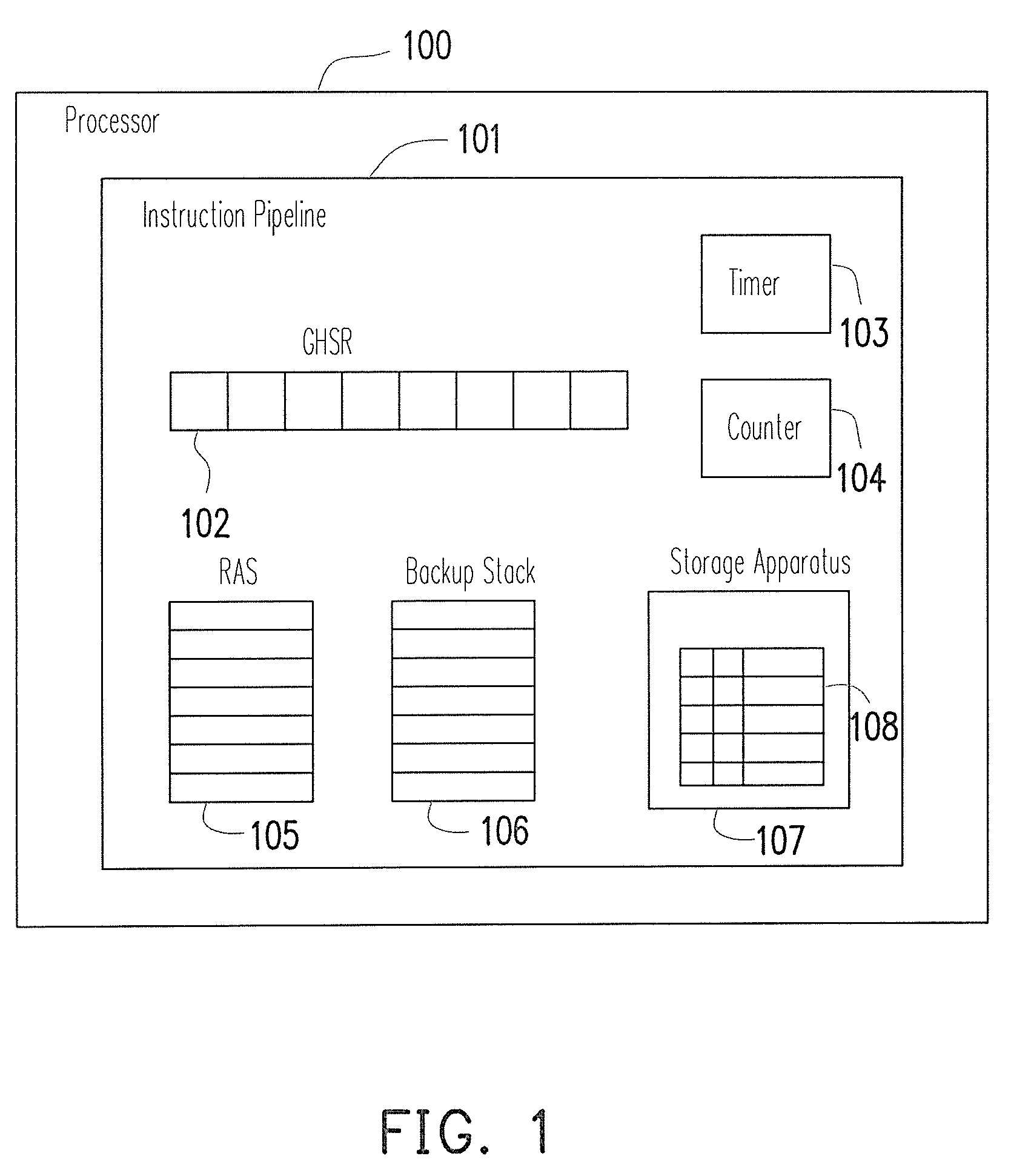

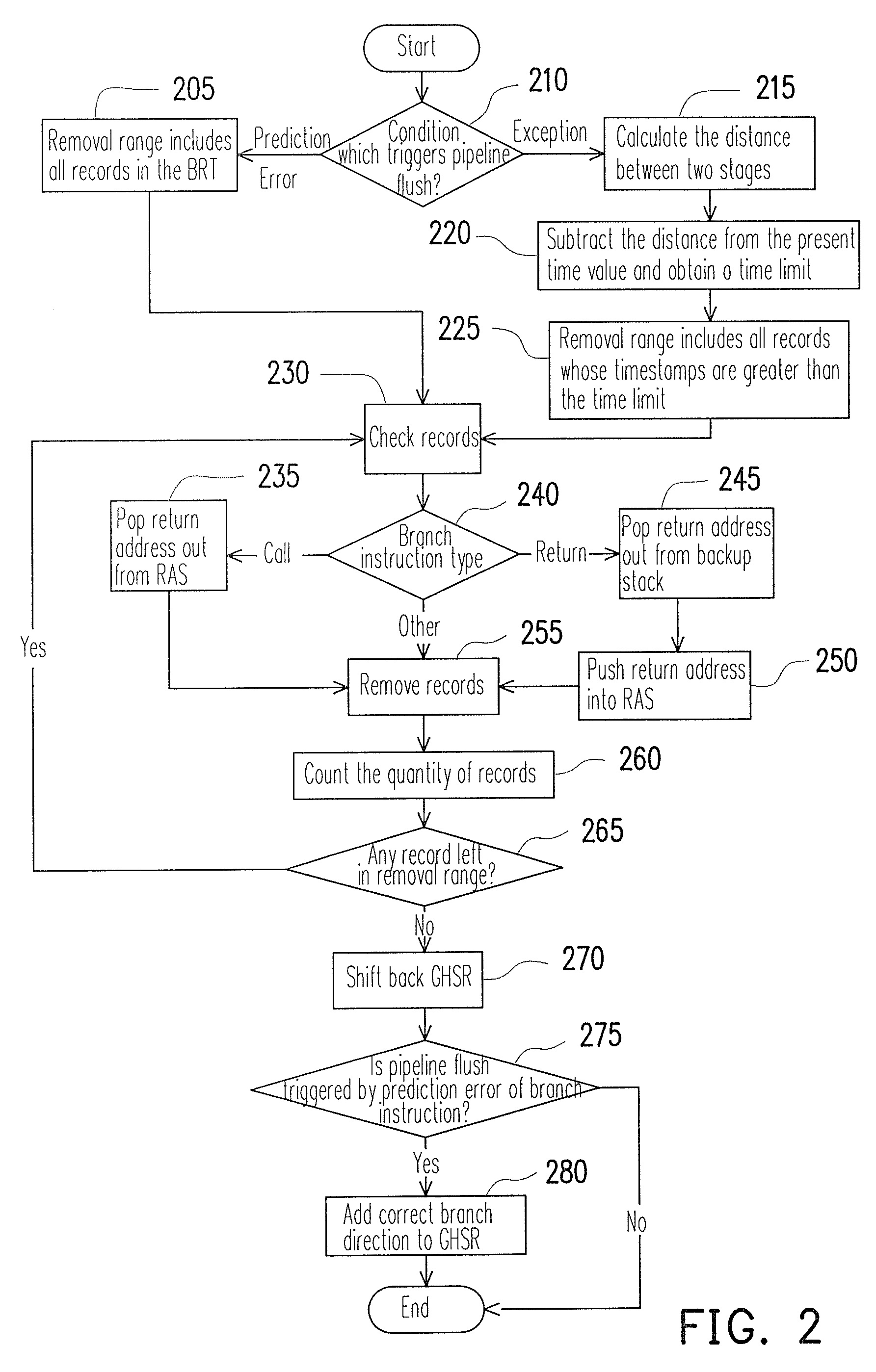

Processor and method for recovering global history shift register and return address stack thereof

ActiveUS20100161951A1Branch prediction accuracy can be increasedIncrease processor efficiencyDigital computer detailsConcurrent instruction executionShift registerReturn address stack

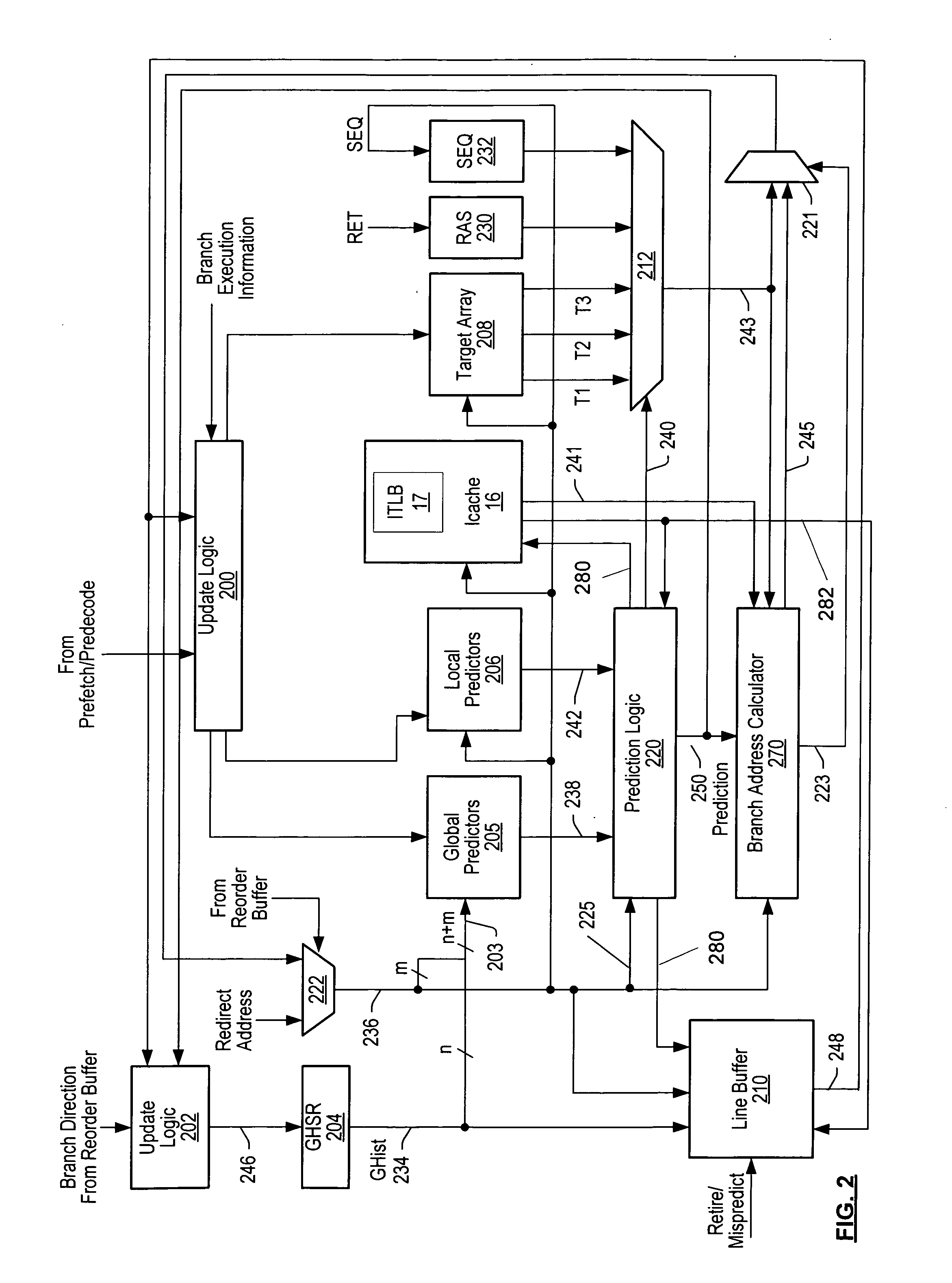

A method for recovering global history shift register (GHSR) and return address stack (RAS) is provided, which is applicable to an instruction pipeline of a processor and includes the following steps. First, provide a branch recovery table (BRT) and a backup stack. Whenever a branch instruction enters a predetermined stage of the instruction pipeline, add a record in the BRT according to the branch instruction. Whenever a return address is popped from the RAS of the instruction pipeline, push the return address into the backup stack. When flushing the instruction pipeline, determine a removal range of the BRT according to the condition which triggers the pipeline flush. Recover the RAS according to the records in the removal range and the backup stack. Remove all records in the removal range. Recover the GHSR of the instruction pipeline according to the removed records.

Owner:FARADAY TECH CORP

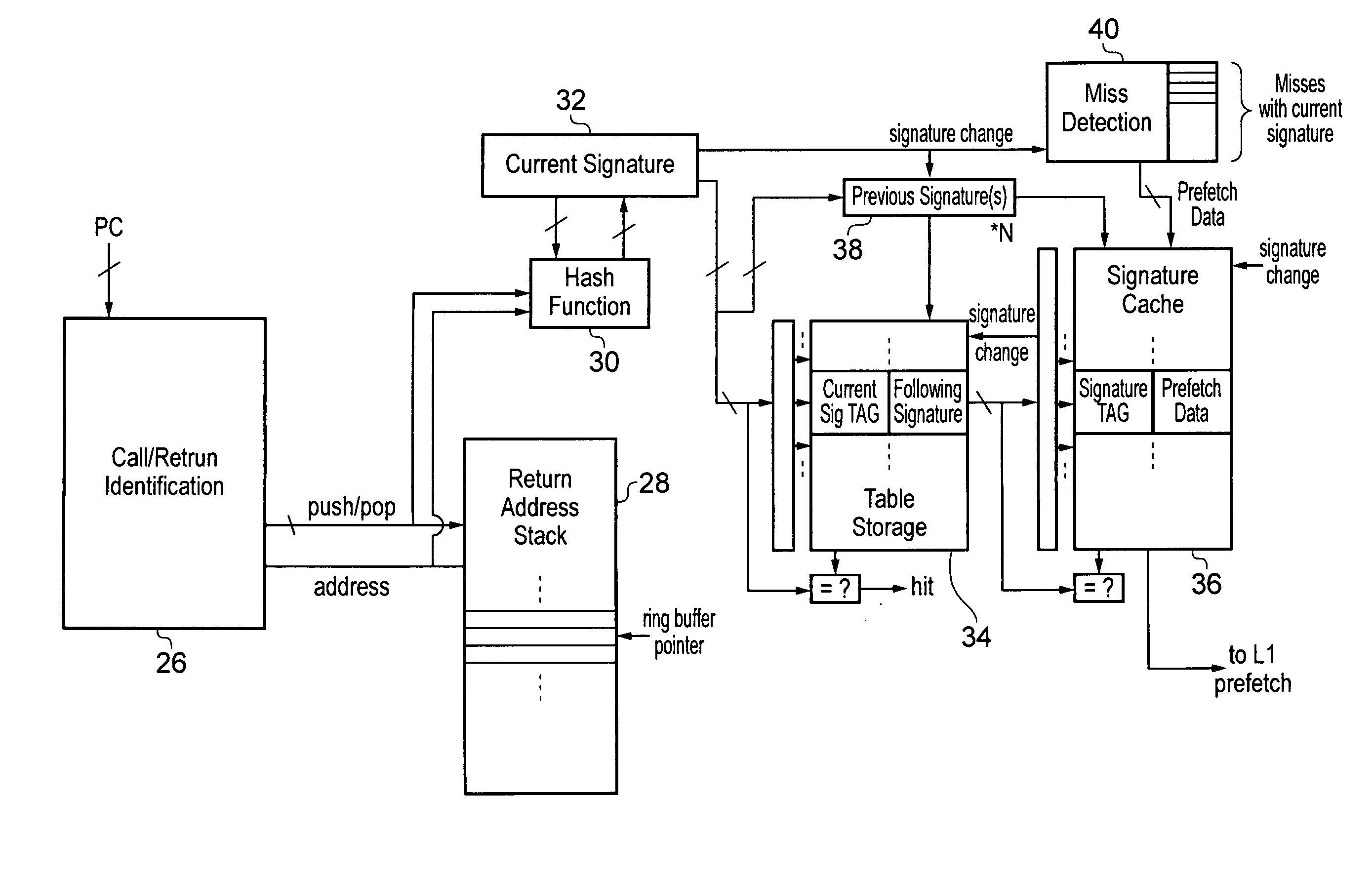

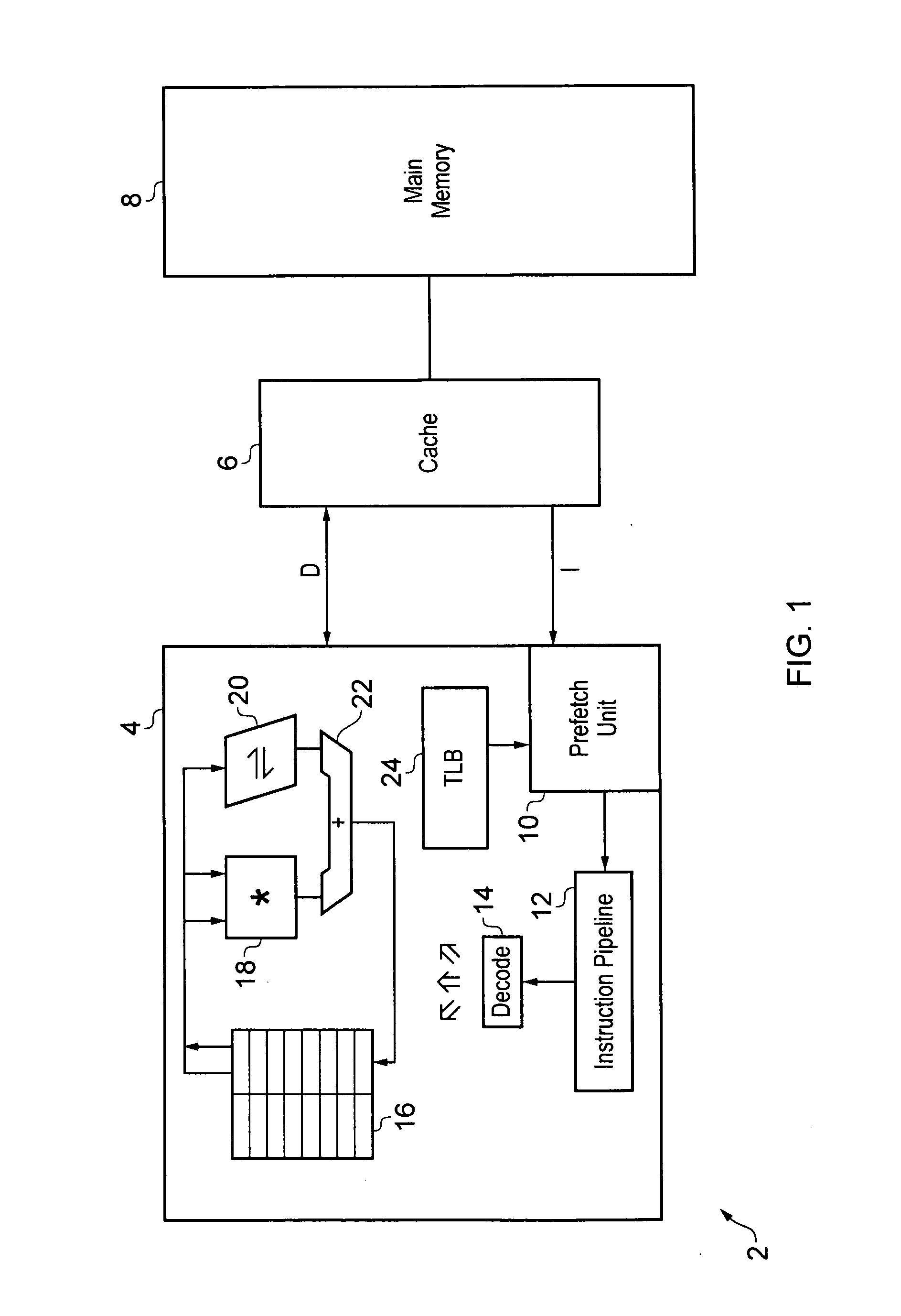

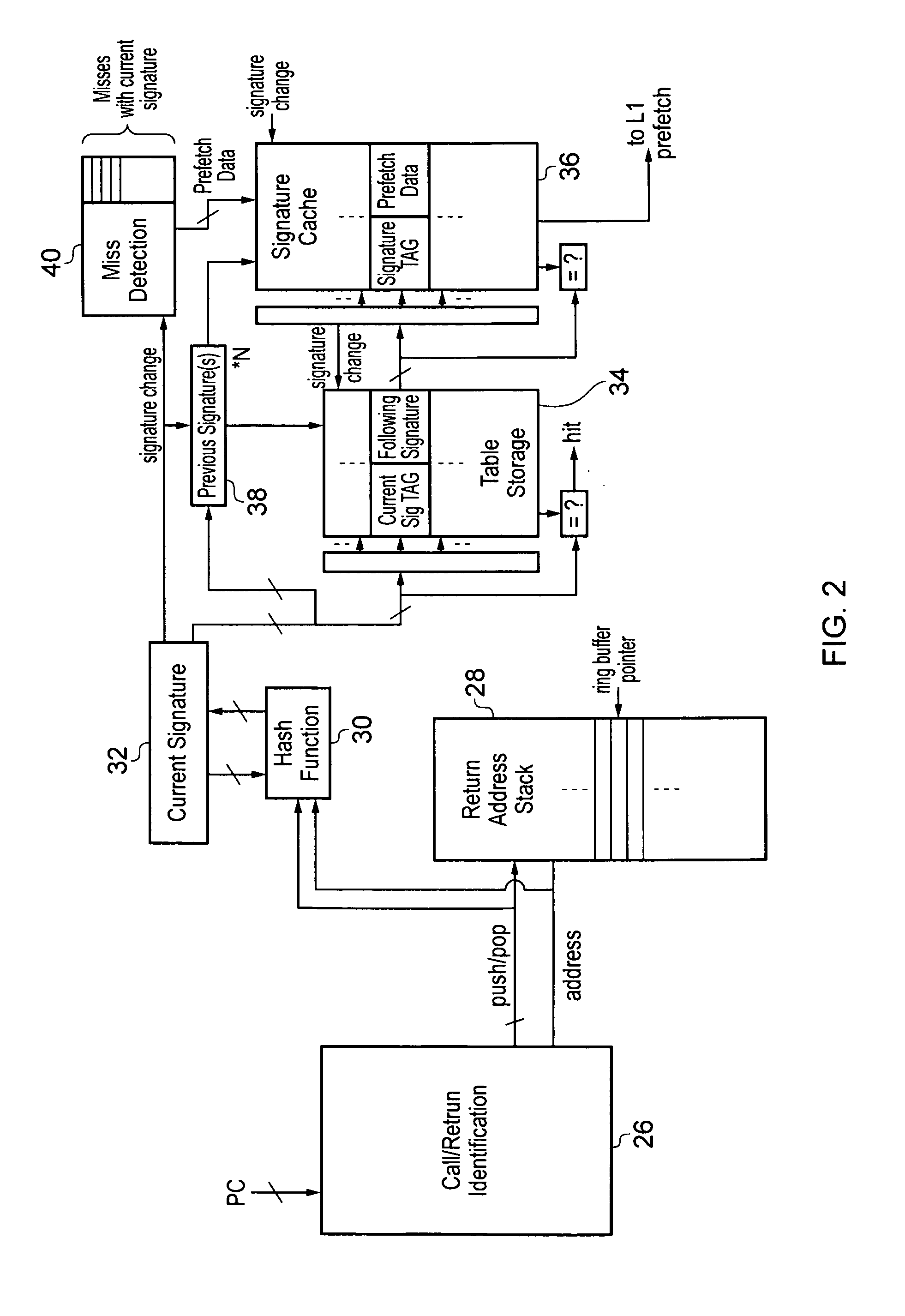

Prefetching based upon return addresses

ActiveUS20140143522A1Improve approximationReduce the overall heightDigital computer detailsConcurrent instruction executionReturn address stackProgram instruction

An apparatus for processing data includes signature generation circuitry 30, 32 for generating a signature value indicative of the current state of the apparatus in dependence upon a sequence of immediately preceding return addresses generating during execution of a stream of program instructions to reach that state of the apparatus. Prefetch circuitry 10 performs one or more prefetch operations in dependence upon the signature value that is generated. The signature value may be generated by a hashing operation (such as an XOR) performed upon return addresses stored within a return address stack 28.

Owner:ARM LTD +1

Maintaining the integrity of an execution return address stack

ActiveUS20130138931A1Digital computer detailsConcurrent instruction executionSpeculative executionComputer architecture

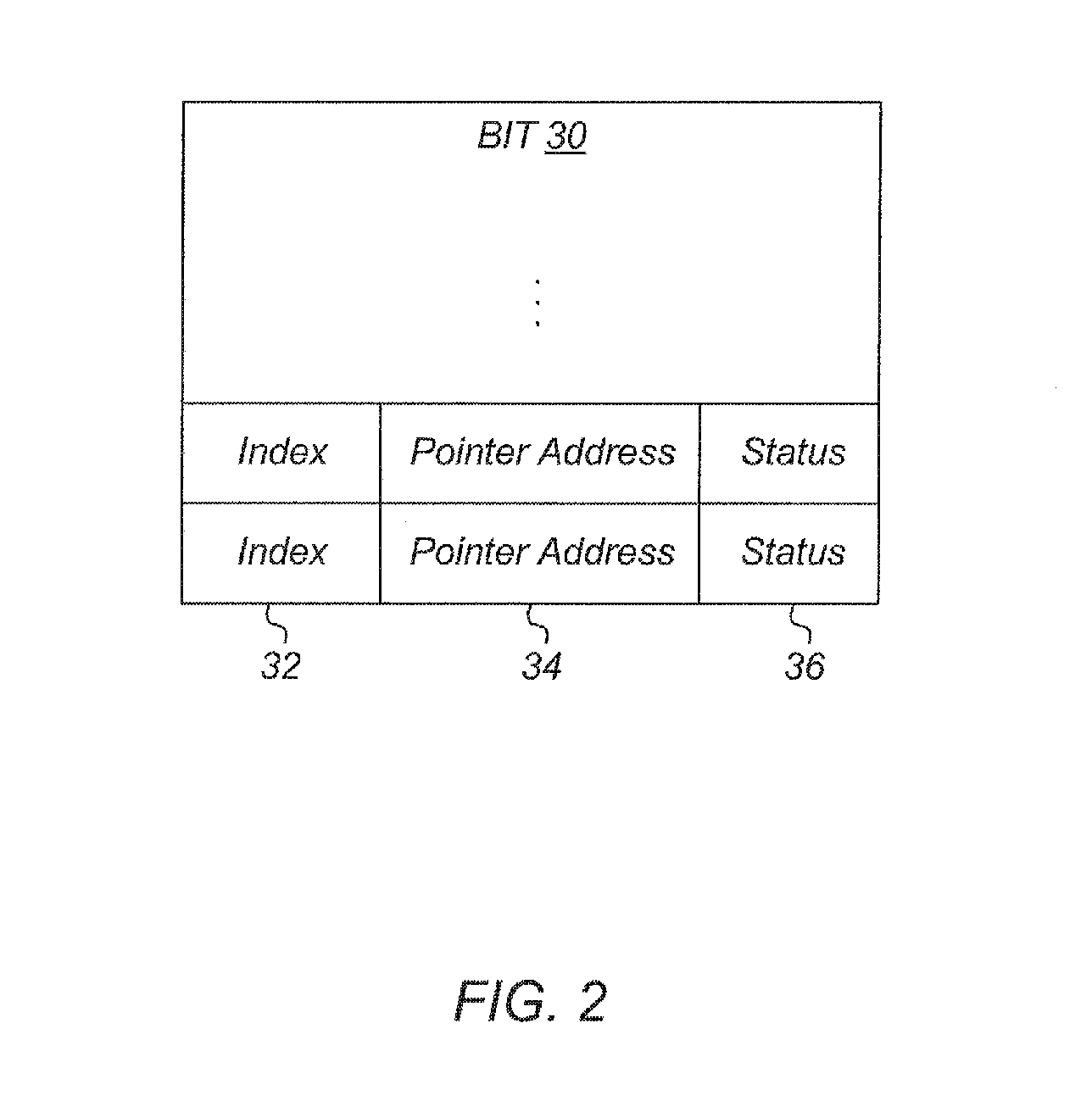

A processor and method for maintaining the integrity of an execution return address stack (RAS). The execution RAS is maintained in an accurate state by storing information regarding branch instructions in a branch information table. The first time a branch instruction is executed, an entry is allocated and populated in the table. If the branch instruction is re-executed, a pointer address is retrieved from the corresponding table entry and the execution RAS pointer is repositioned to the retrieved pointer address. The execution RAS can also be used to restore a speculative RAS due to a mis-speculation.

Owner:APPLE INC

Method and Apparatus for Guest Return Address Stack Emulation Supporting Speculation

ActiveUS20140281388A1Advantageously conserves precious spaceEfficient and flexibleRuntime instruction translationDigital computer detailsReturn address stackParallel computing

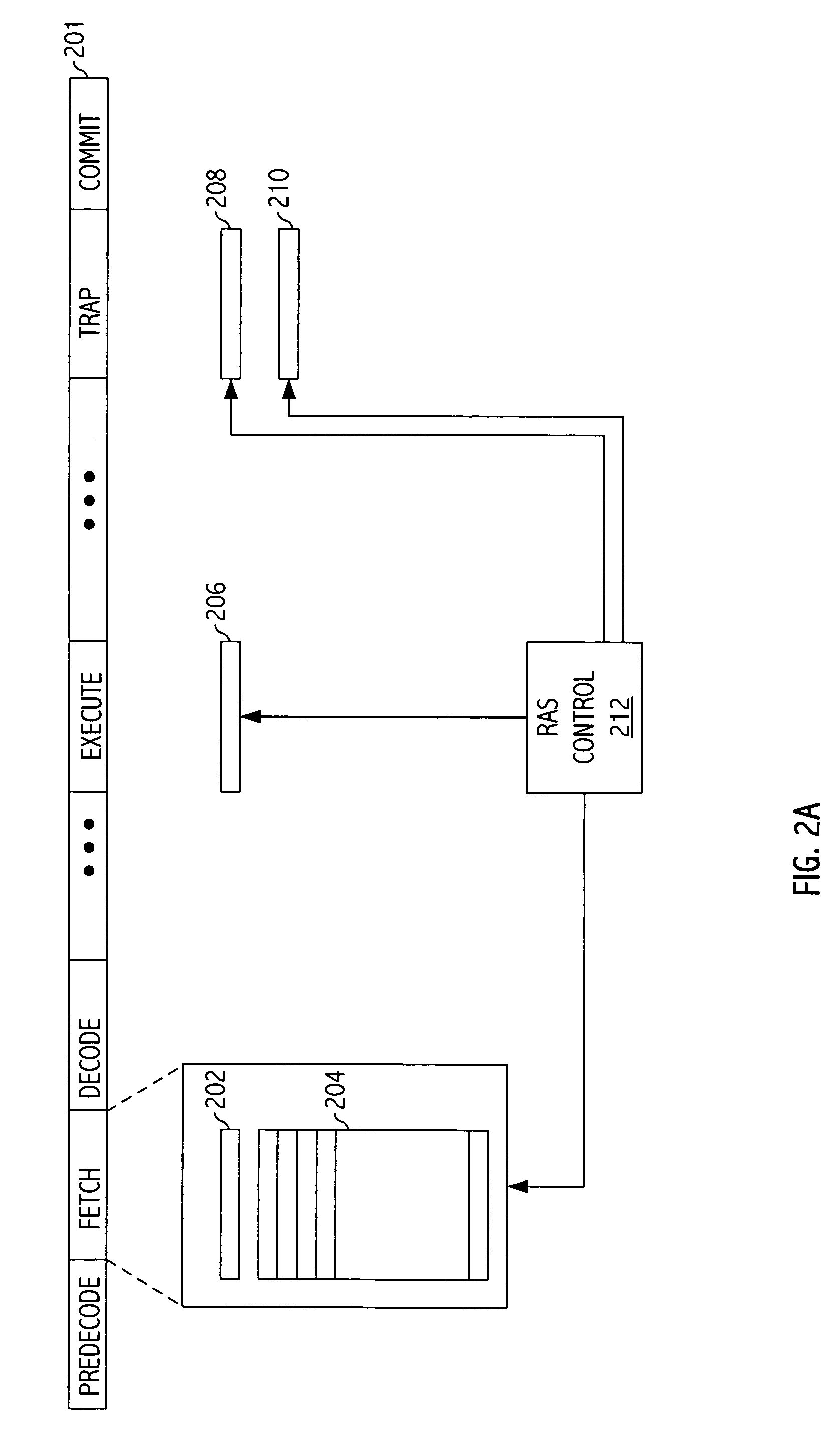

A microprocessor implemented method for maintaining a guest return address stack in an out-of-order microprocessor pipeline is disclosed. The method comprises mapping a plurality of instructions in a guest address space into a corresponding plurality of instructions in a native address space. For each function call instruction in the native address space fetched during execution, the method also comprises performing the following: (a) pushing a current entry into a guest return address stack (GRAS) responsive to a function call, wherein the GRAS is maintained at the fetch stage of the pipeline, and wherein the current entry comprises information regarding both a guest target return address and a corresponding native target return address associated with the function call; (b) popping the current entry from the GRAS in response to processing a return instruction; and (c) fetching instructions from the native target return address in the current entry after the popping from the GRAS.

Owner:INTEL CORP

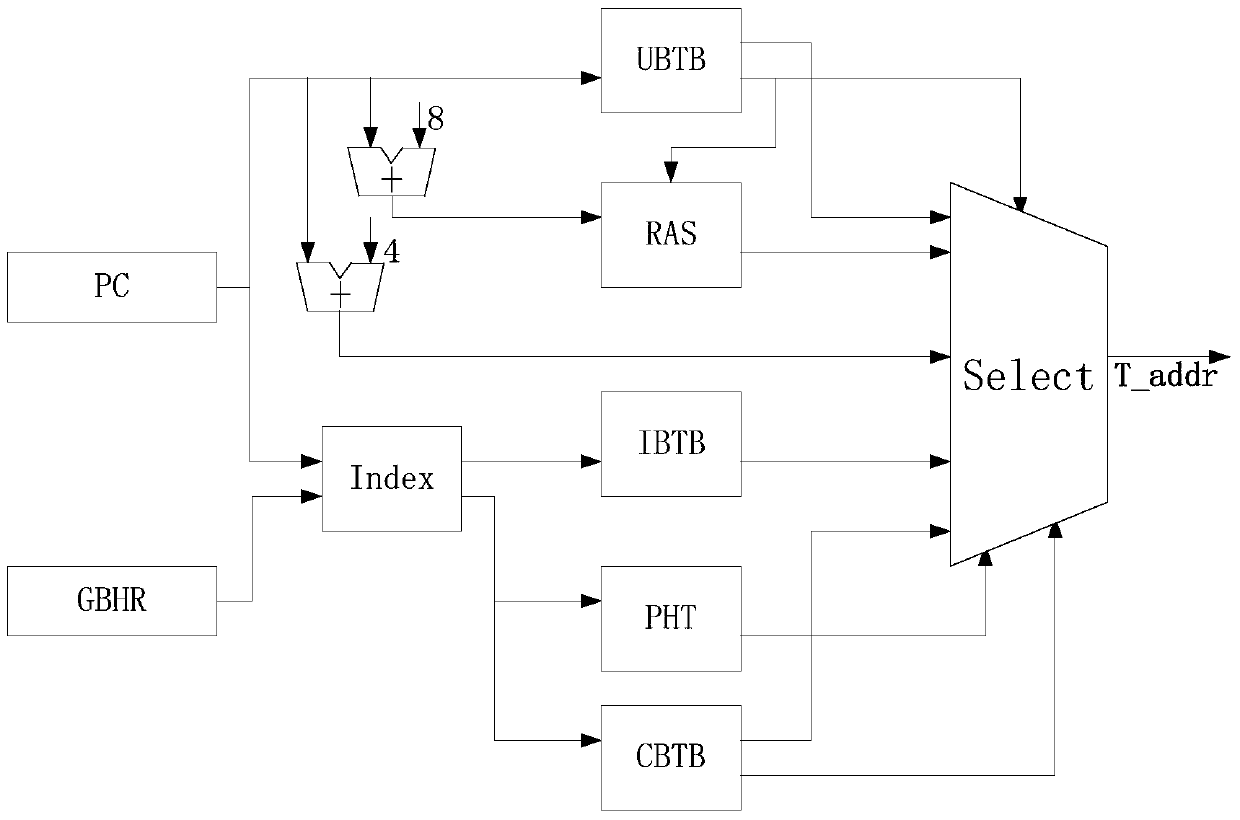

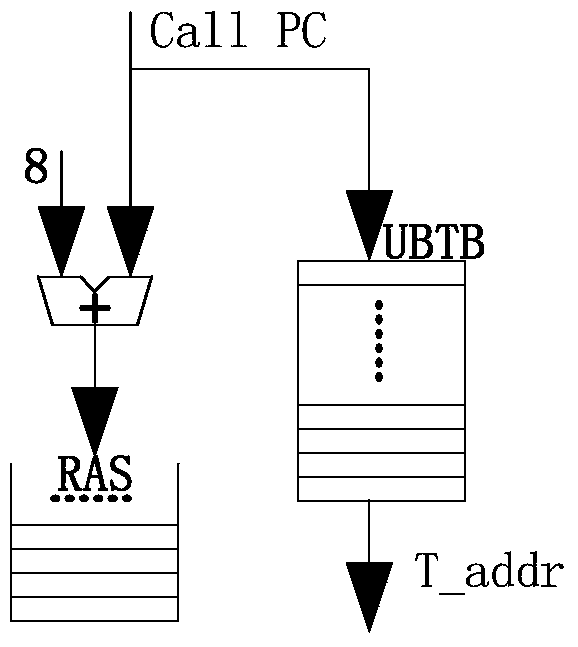

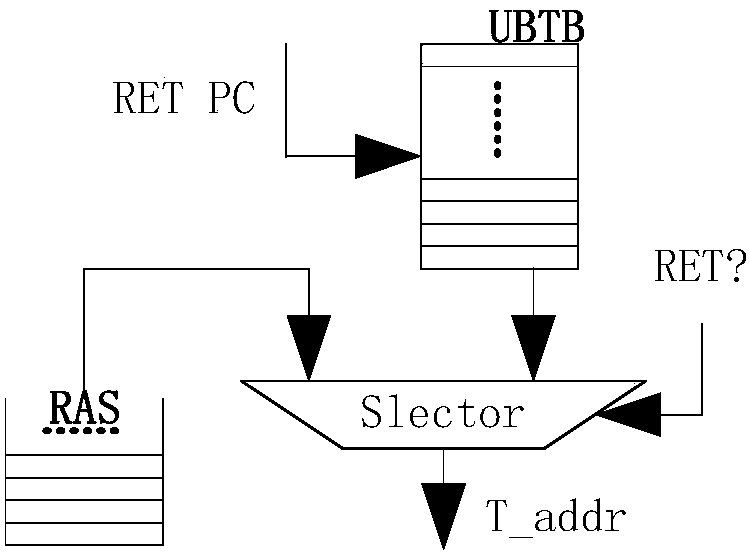

SPARC V8 system structure based classified type mixed branch prediction system

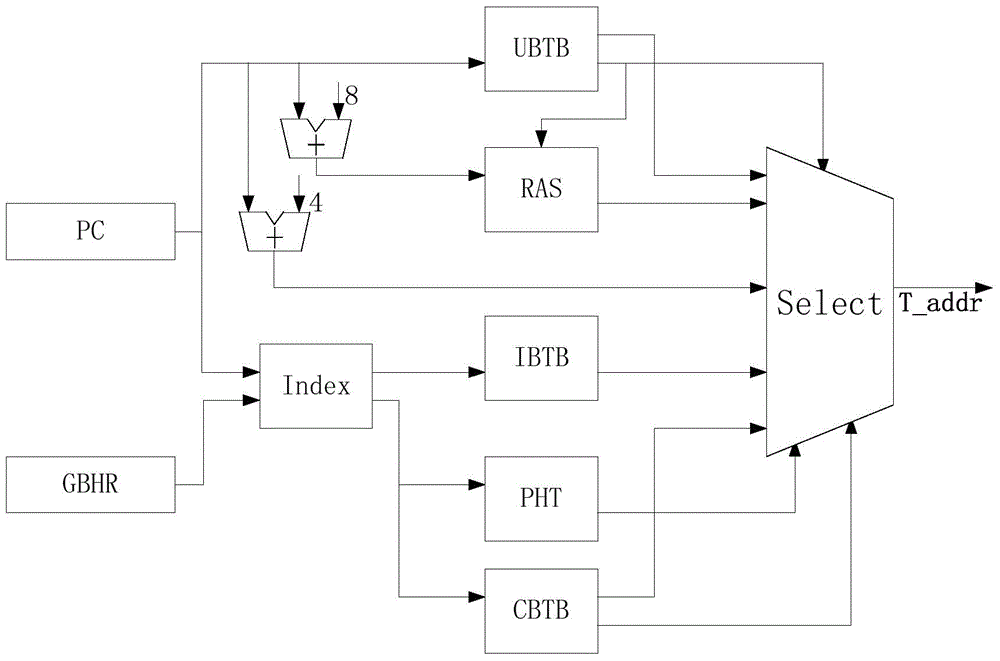

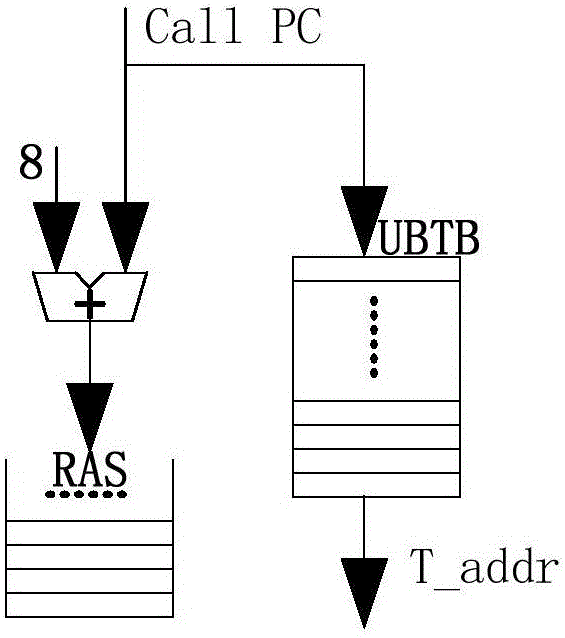

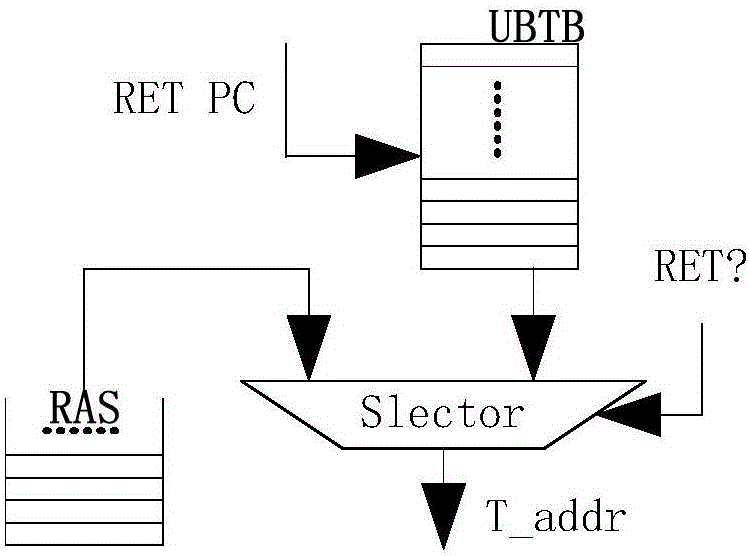

ActiveCN105718241AExpand coverageOptimal Branch Prediction SchemeNext instruction address formationMemory systemsReturn address stackAssembly line

The invention discloses an SPARC V8 system structure based classified type mixed branch prediction system. Firstly, a branch target buffer is queried according to PC values of instructions at an instruction fetching stage to obtain branch instruction types; the branch instructions are dispatched to respective prediction modules; a return address stack (RAS) with a dynamic configuration counter is used in skip branch prediction; a complementary prediction method is used in indirect branch prediction; a tag recording correctness of previous branch prediction in a conditional branch target buffer (CBTB) adopts a partial skip three-state conversion algorithm in conditional branch prediction; decoding result information of the instructions are recorded in a prediction information table (PIT) at a decoding stage; a judgment is made at an execution stage; if a prediction result of the branch instructions is that the skip occurs, the result judgment is made by using a skip prediction result arbiter Arbiter_T; and if the prediction result of the branch instructions is that the skip does not occur, the result judgment is made by using a non-skip prediction result arbiter Arbiter_N. Therefore, the instruction delay influence of the branch instructions on an assembly line is eliminated and the execution efficiency of a processor is improved.

Owner:BEIJING MXTRONICS CORP +1

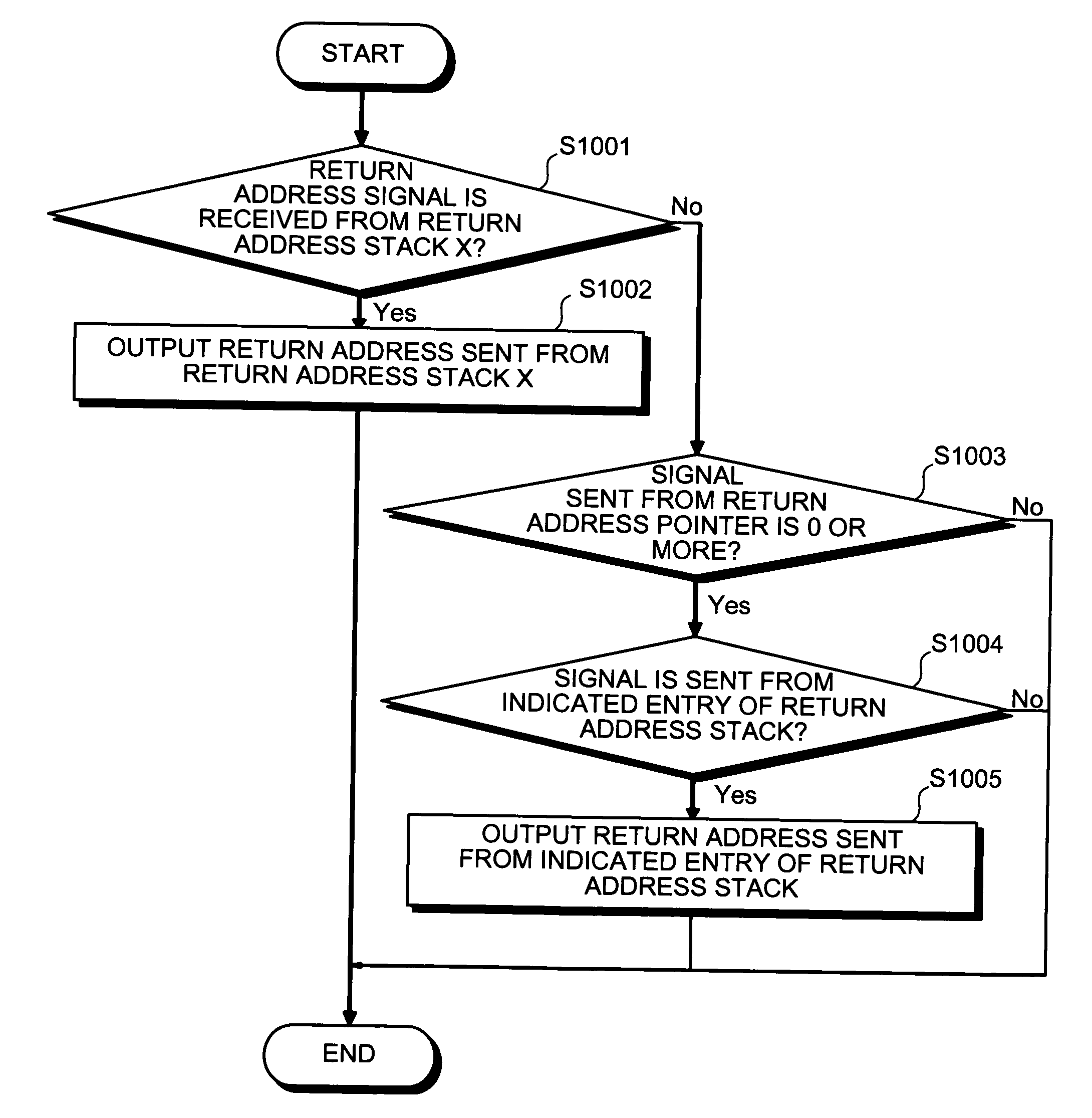

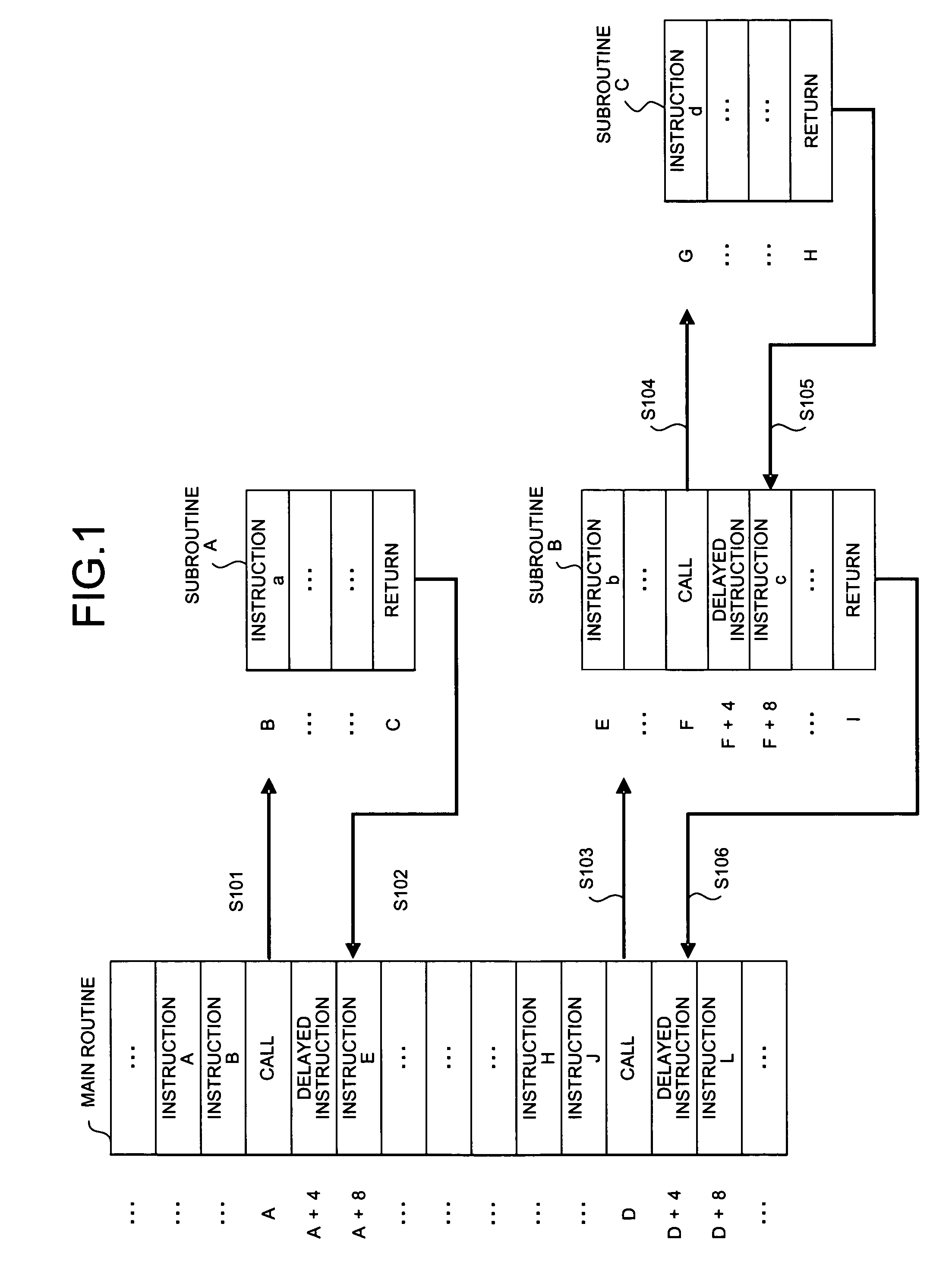

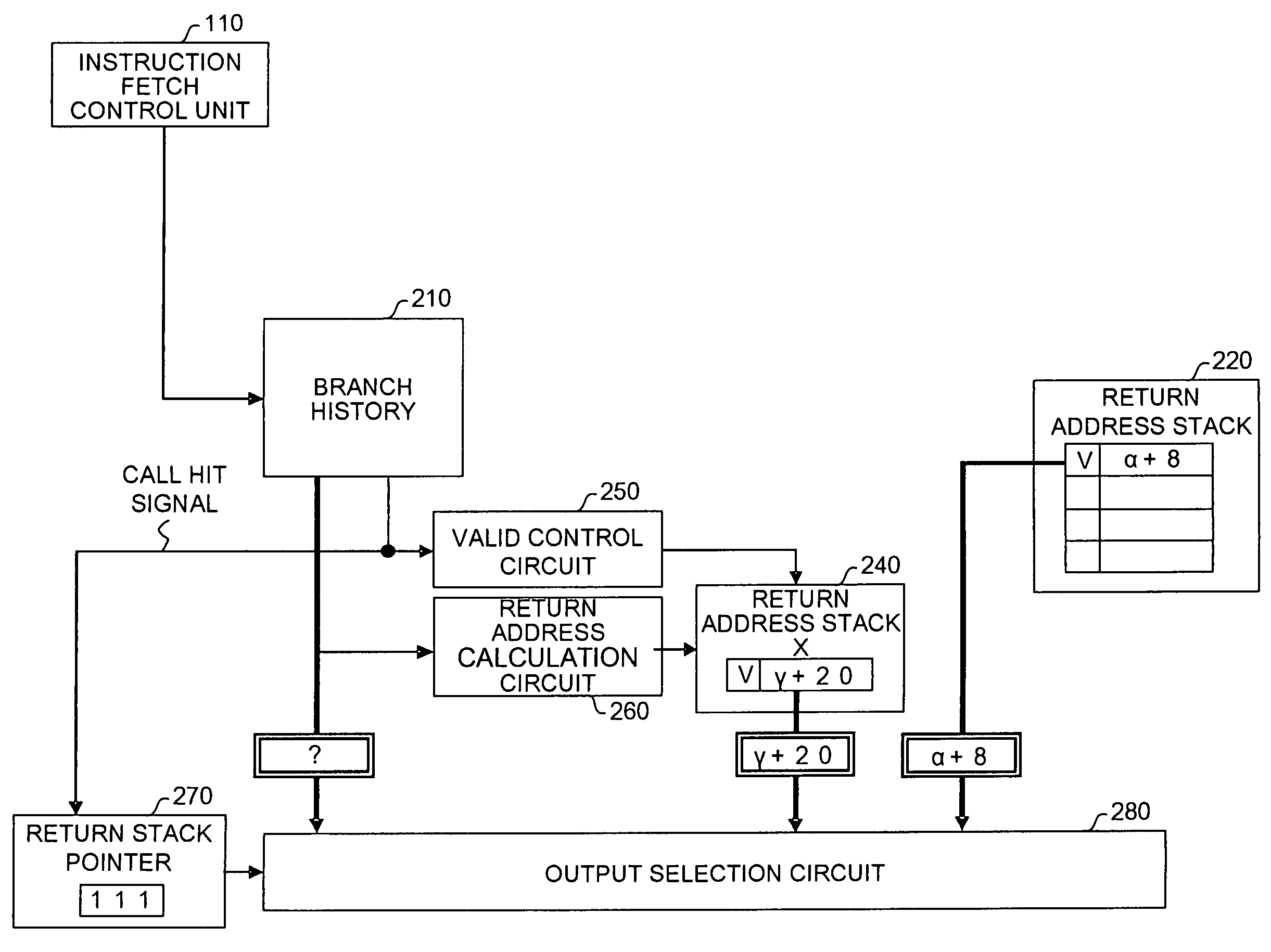

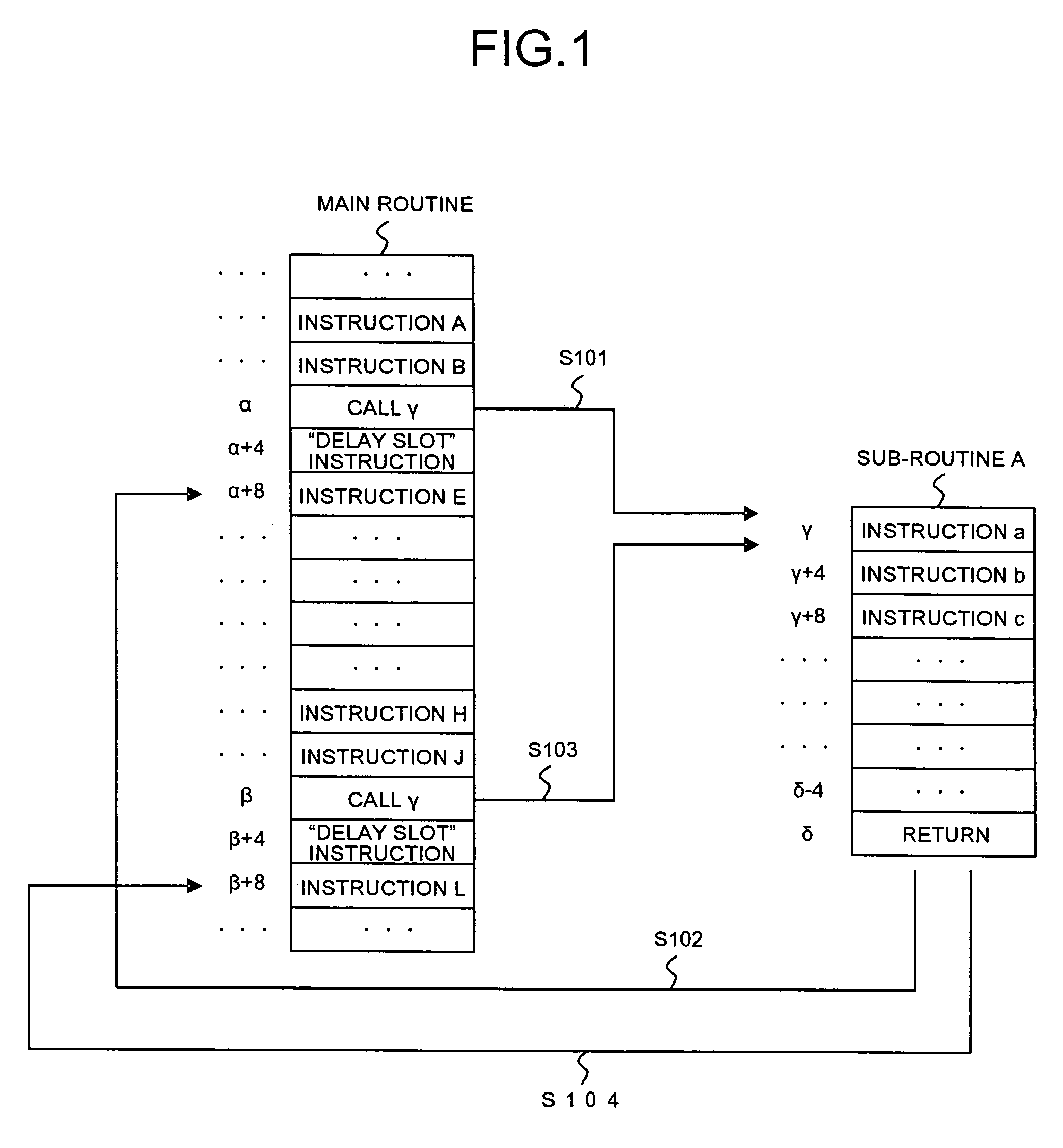

Branch predicting apparatus and branch predicting method

ActiveUS20060149948A1Digital computer detailsSpecific program execution arrangementsReturn address stackParallel computing

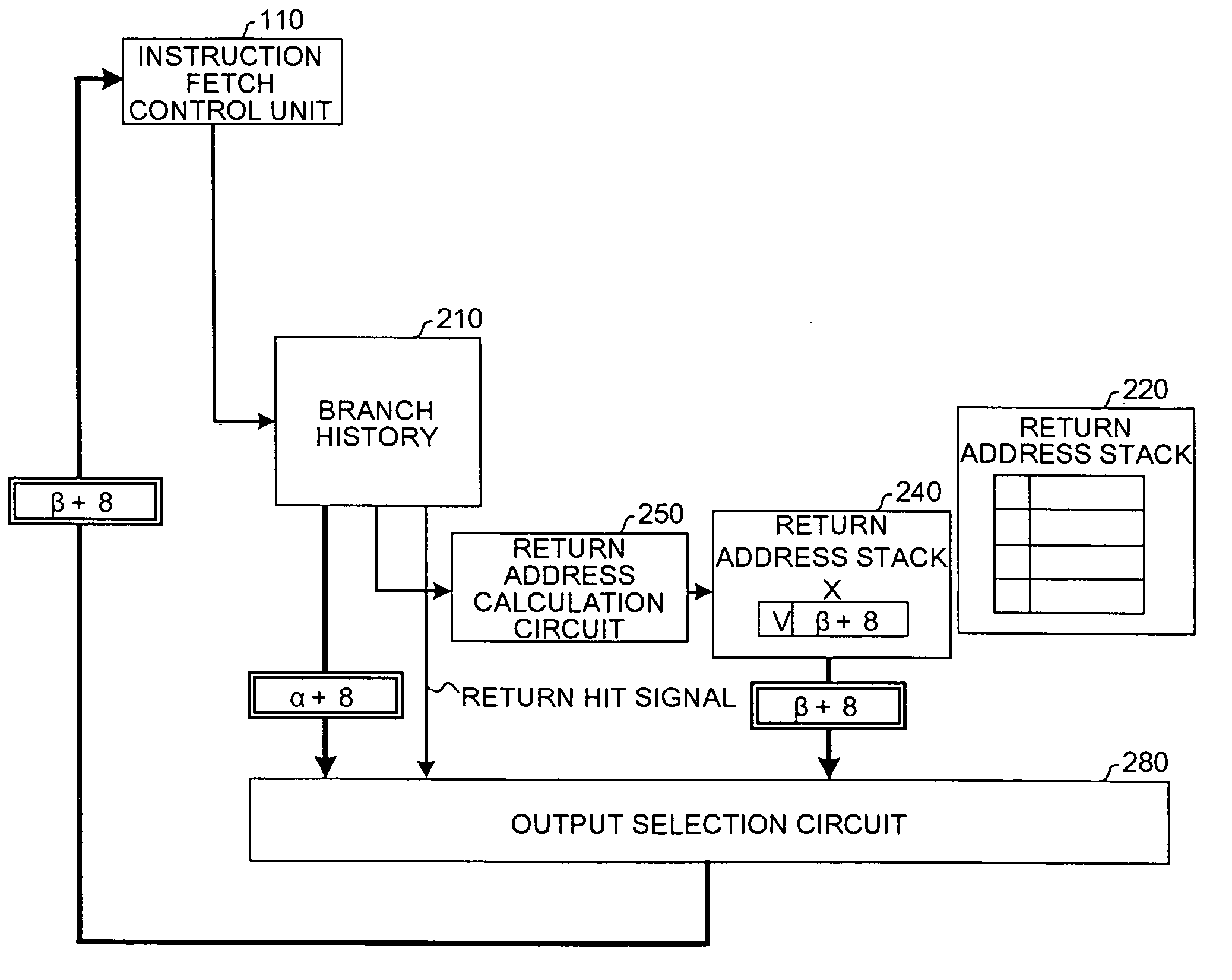

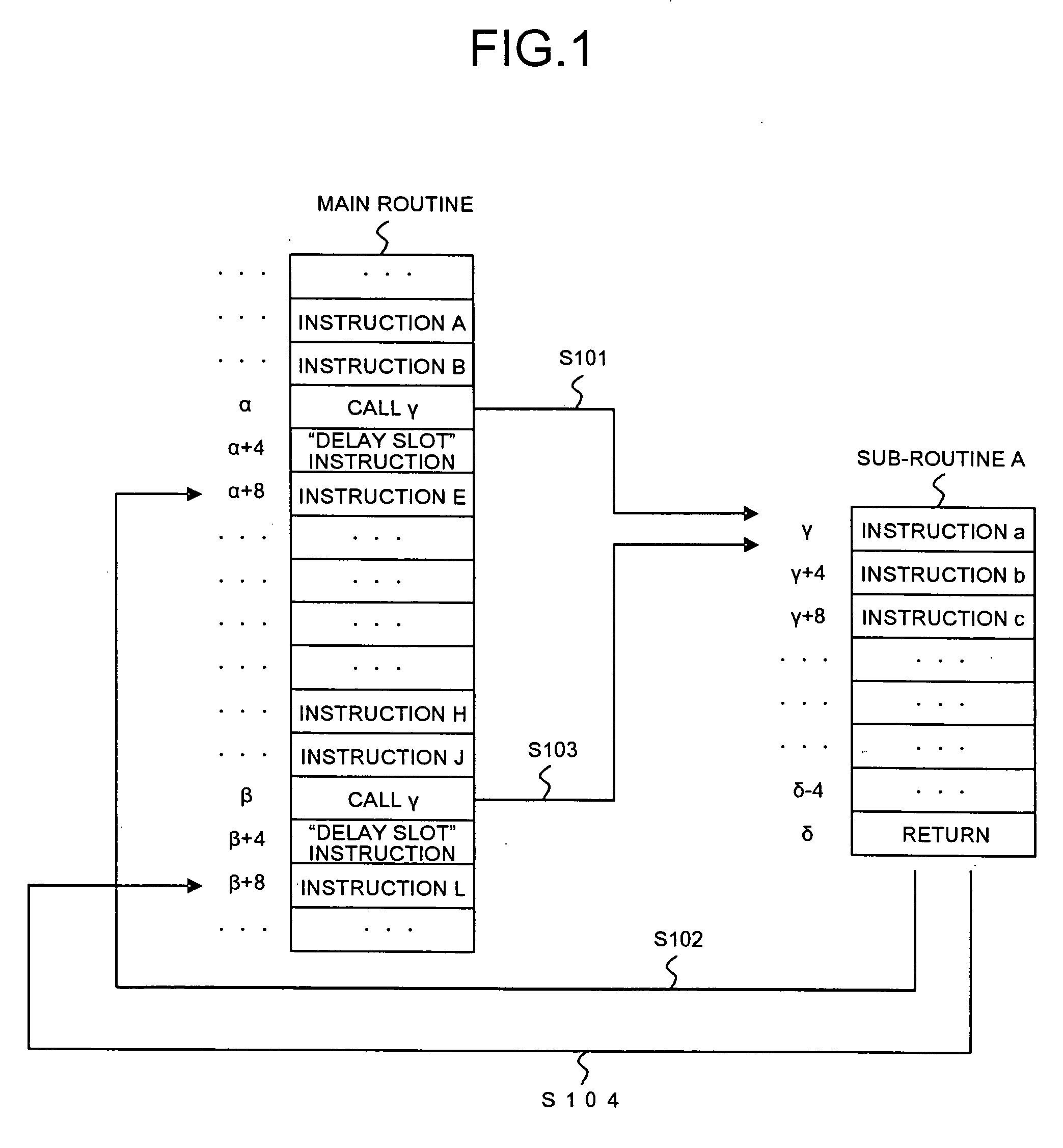

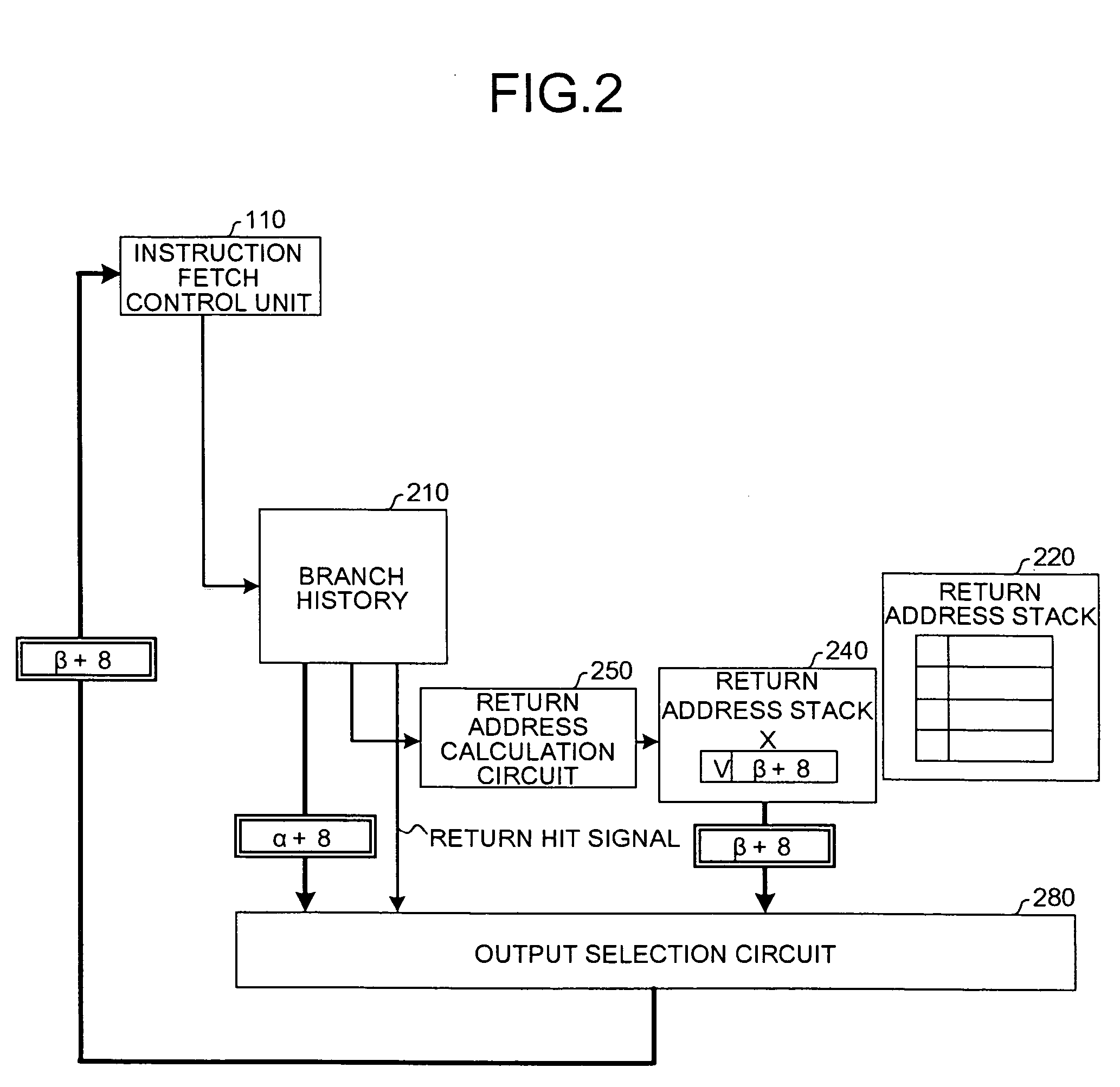

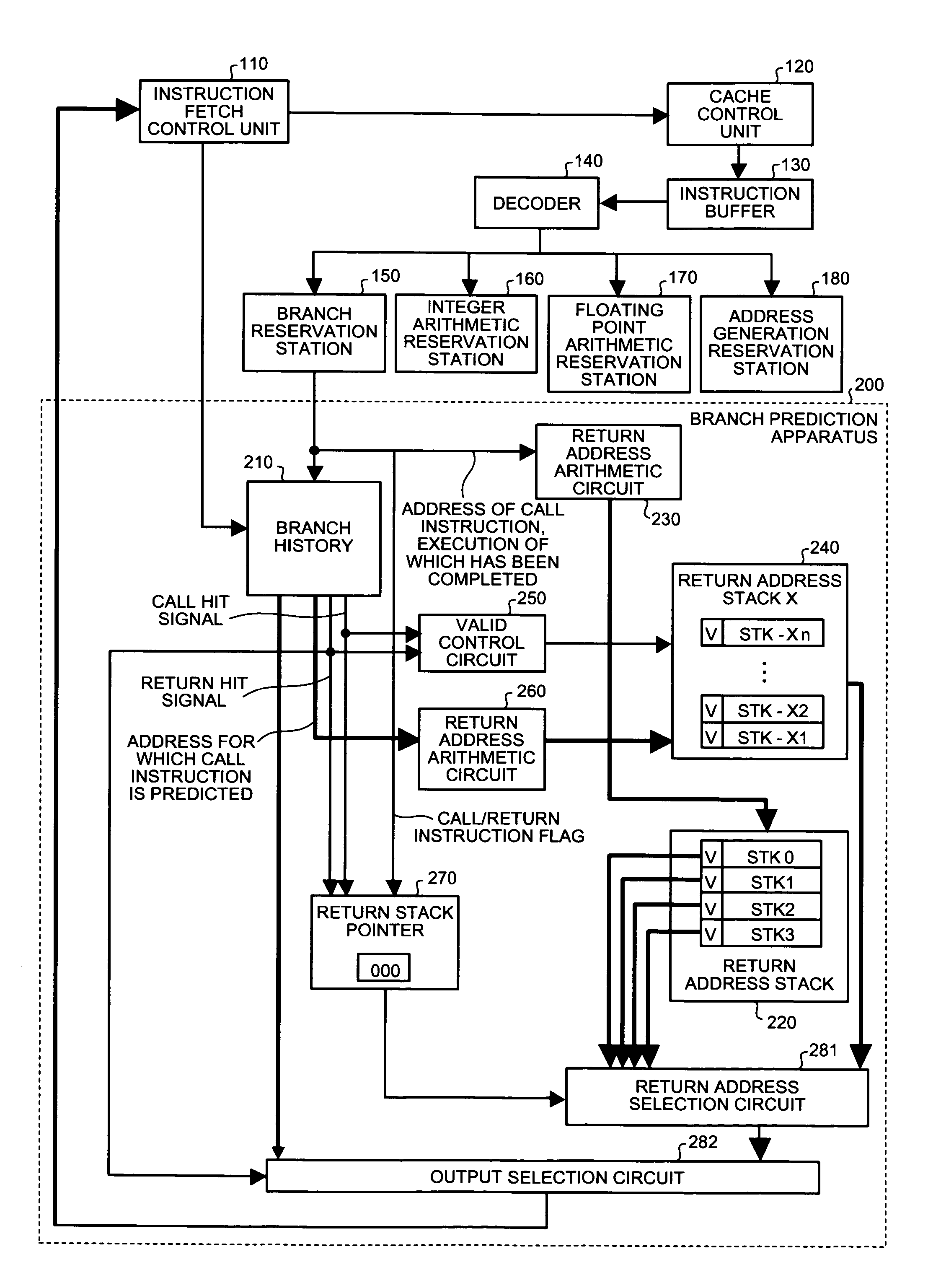

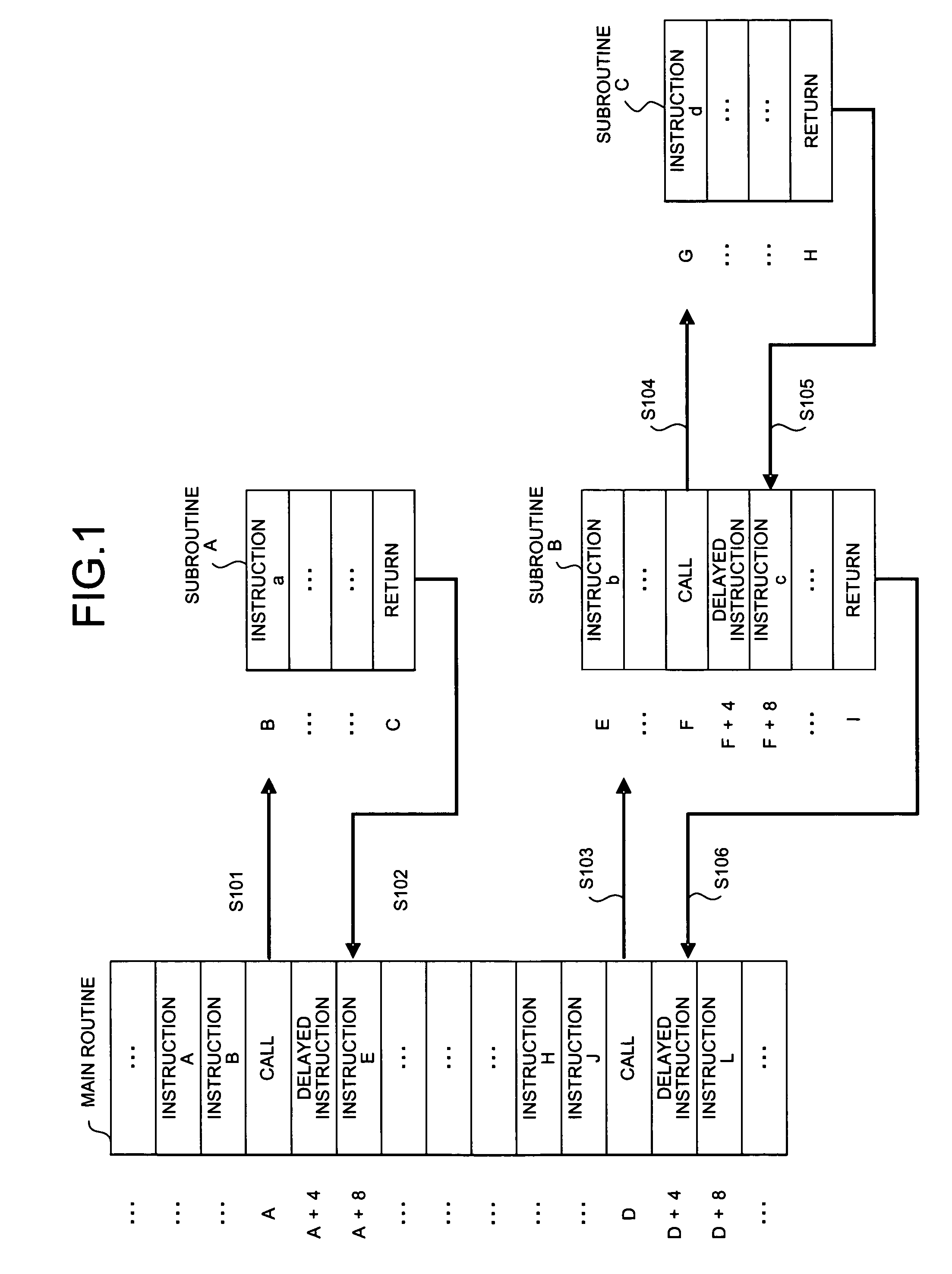

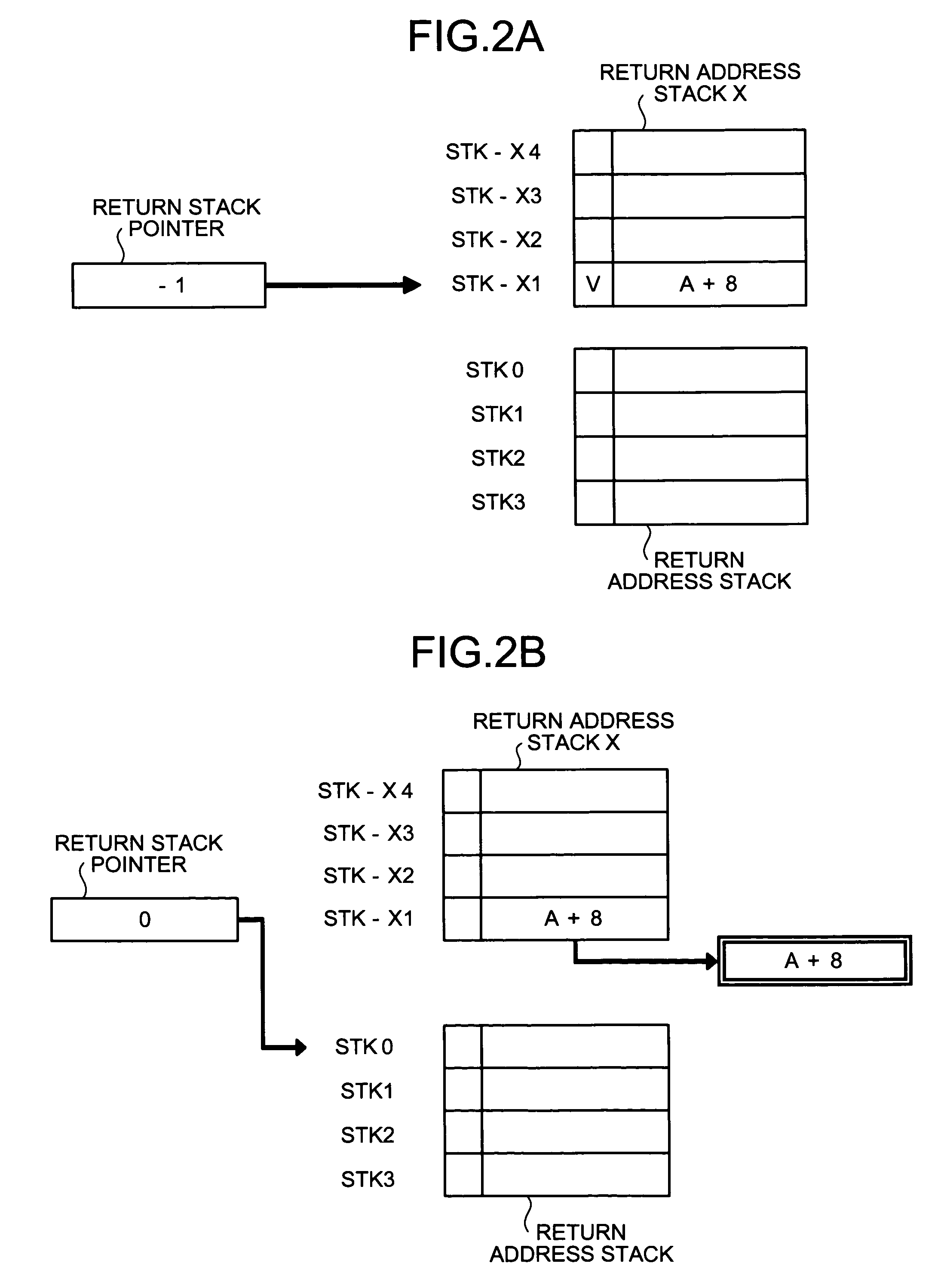

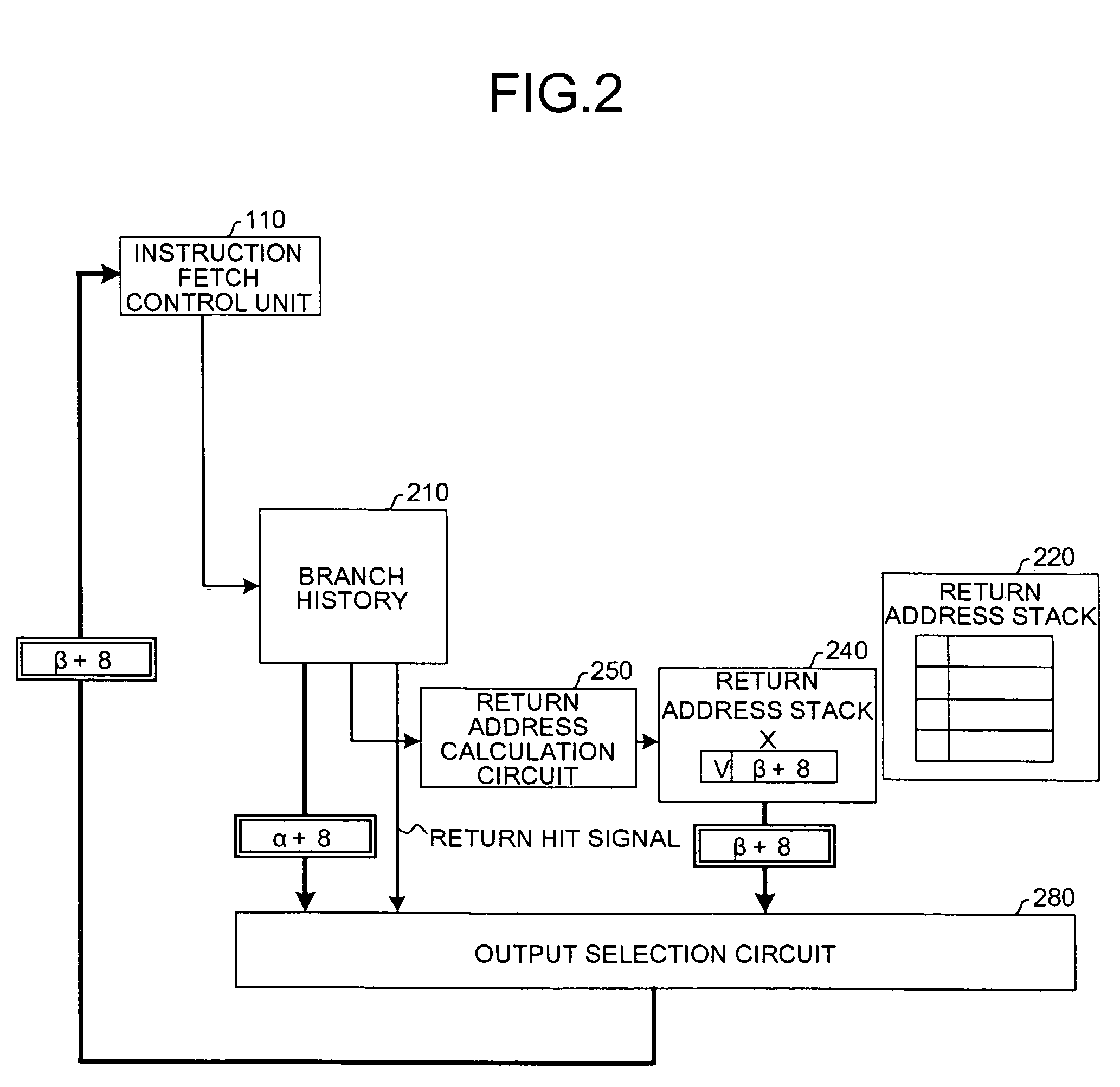

A branch history stores execution history information of branch instructions, and predicts presence of a branch instruction and a corresponding branch destination. A first return address stack stores, when an execution of a call instruction of a subroutine is completed, address information of a return destination of a corresponding return instruction. A second return address stack stores, when presence of a call instruction of a subroutine is predicted, address information of a return destination of a corresponding return instruction. An output selecting unit selects, when presence of a return instruction is predicted, if address information is stored in the second return address stack, the address information as a result of the branch prediction with a highest priority, and outputs the address information selected.

Owner:FUJITSU LTD

Branch predicting apparatus and branch predicting method

InactiveUS20060026410A1Digital computer detailsSpecific program execution arrangementsReservation stationReturn address stack

A return address in response to a return instruction corresponding to a call instruction is stored in a return address stack when a branch history detects presence of the call instruction. When the branch history detects the presence of the return instruction before a branch reservation station completes executing the call instruction, the return address in response to the return instruction is not stored in the return address stack. If so, an output selection circuit predicts a correct return target using information stored in the return address stack.

Owner:FUJITSU LTD

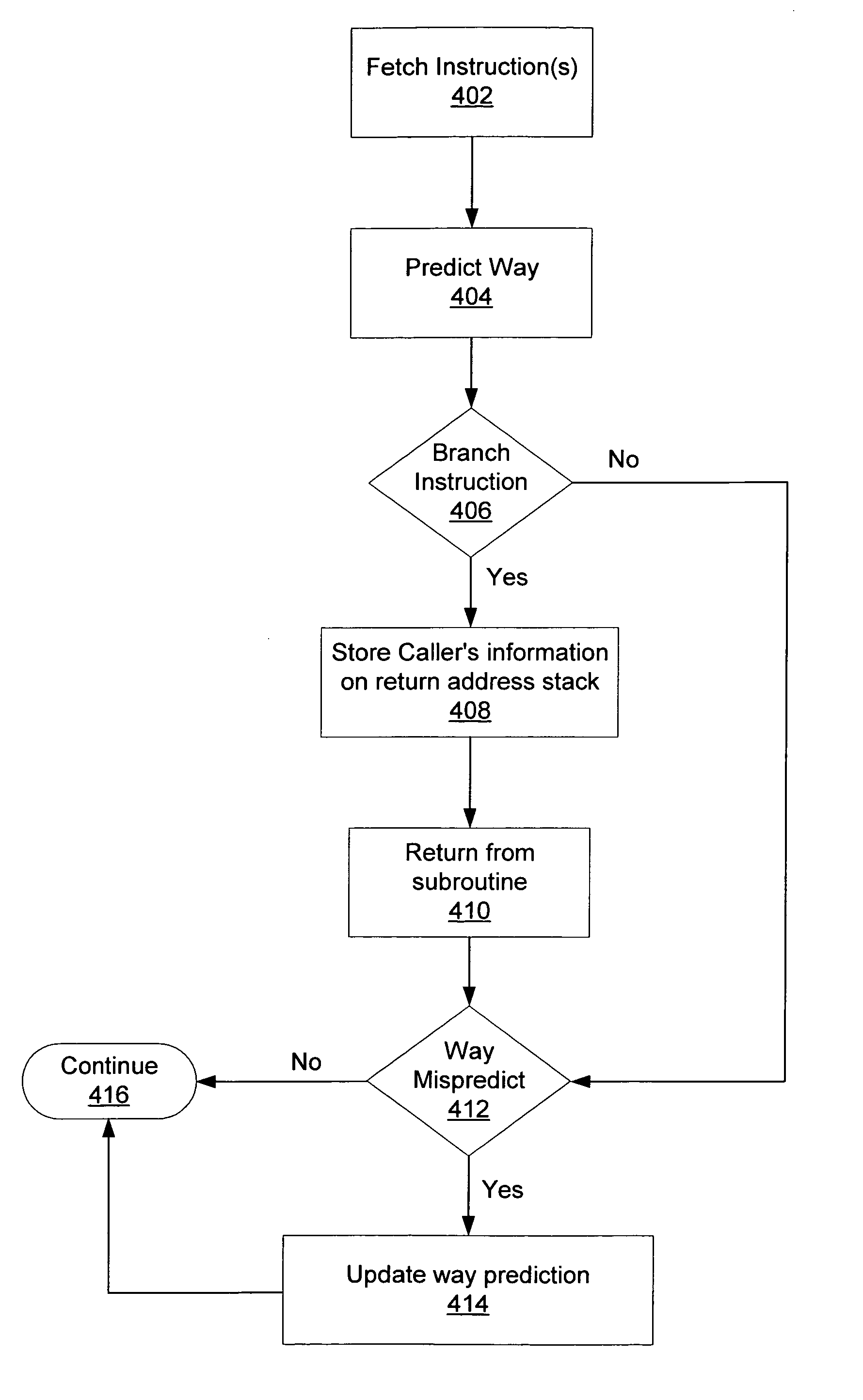

Call return stack way prediction repair

InactiveUS20070033385A1Memory architecture accessing/allocationDigital computer detailsReturn address stackParallel computing

A mechanism for repairing way mispredictions in a cache. An instruction cache in a processor is coupled to receive a fetch address and a corresponding way prediction. A return address stack is configured to store a return address corresponding to a fetched branch instruction, a return address way prediction, and information identifying the branch instruction. In response to detecting the return address way prediction is incorrect, the information identifying the branch instruction which is popped from the return address stack is utilized to identify the corresponding branch instruction and repair the return address way prediction. If way misprediction is detected by the instruction cache, the instruction cache is configured to search additional ways for a hit. In the event of a hit in the additional ways, the instruction cache is configured to convey an updated way prediction. In the event of a miss, the instruction cache is configured to convey a miss indication.

Owner:GLOBALFOUNDRIES INC

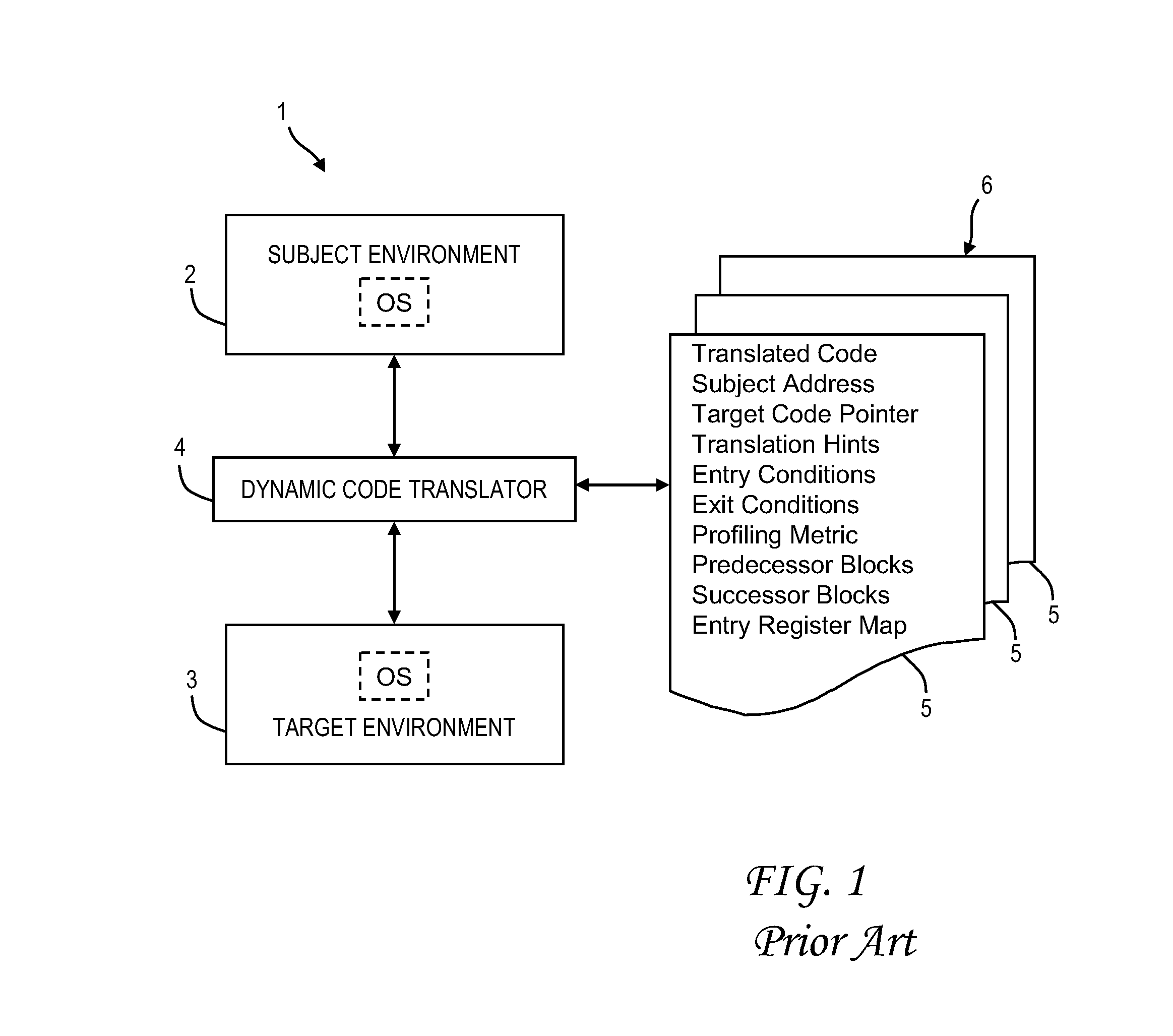

Return address optimisation for a dynamic code translator

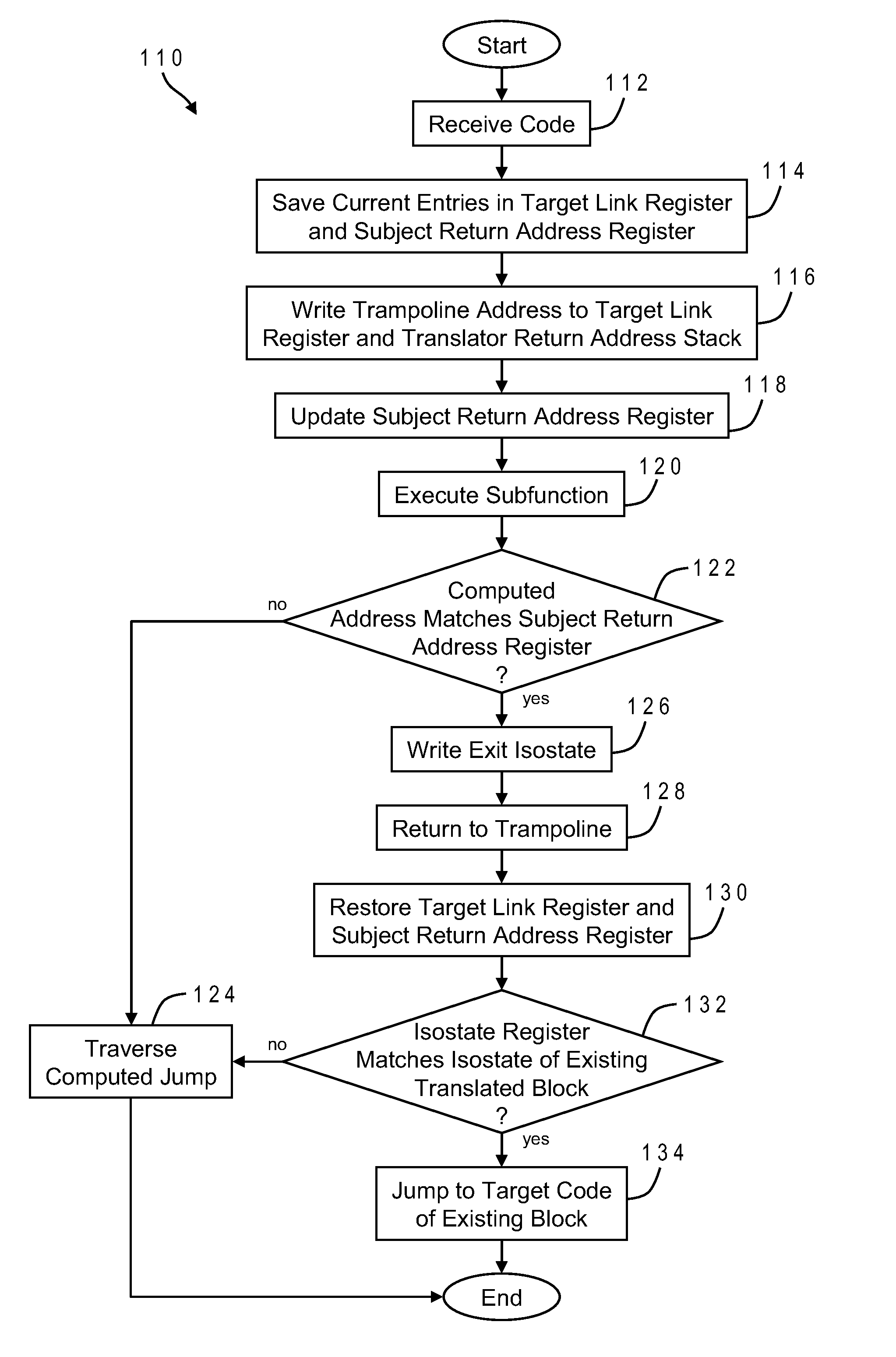

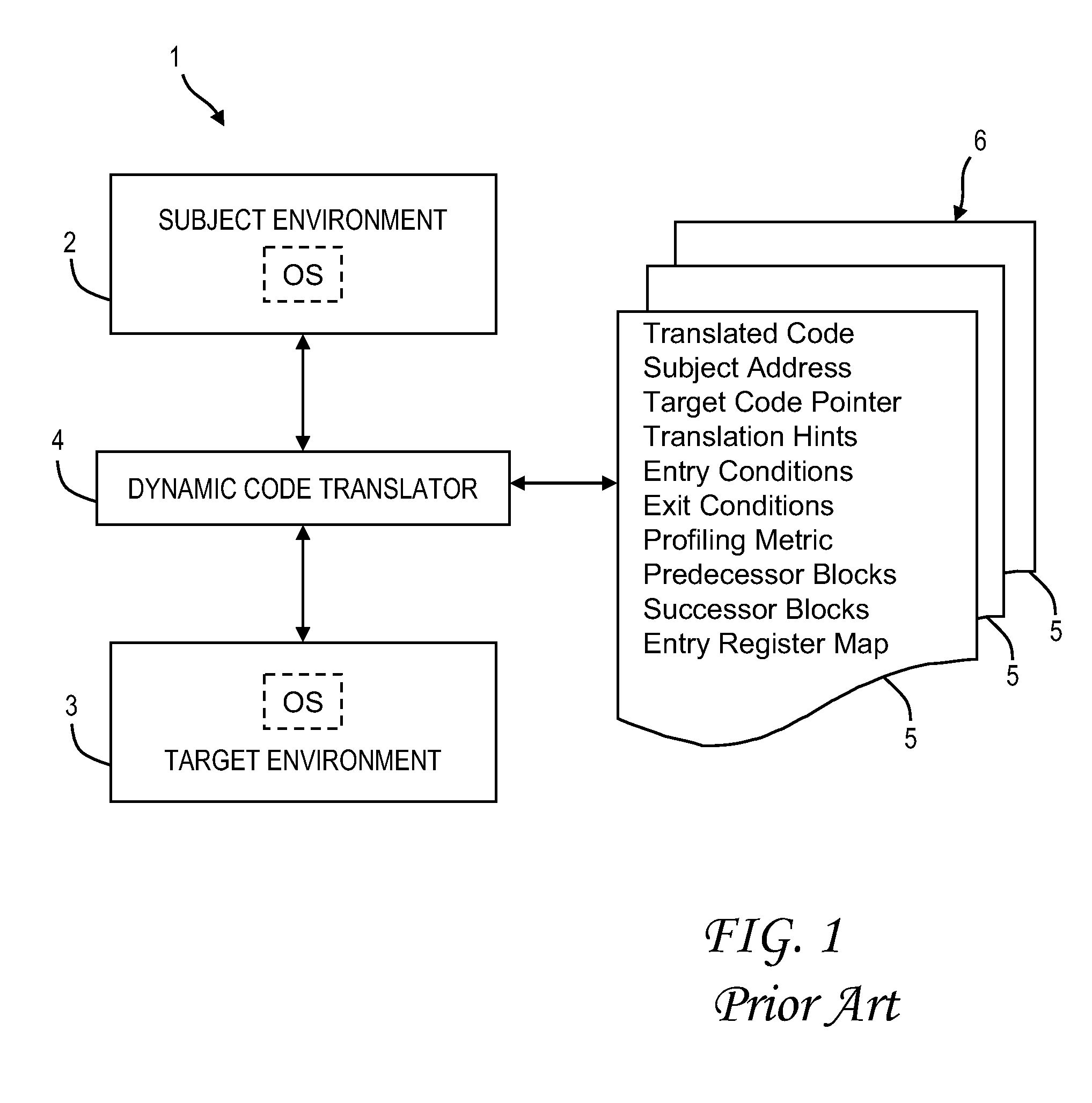

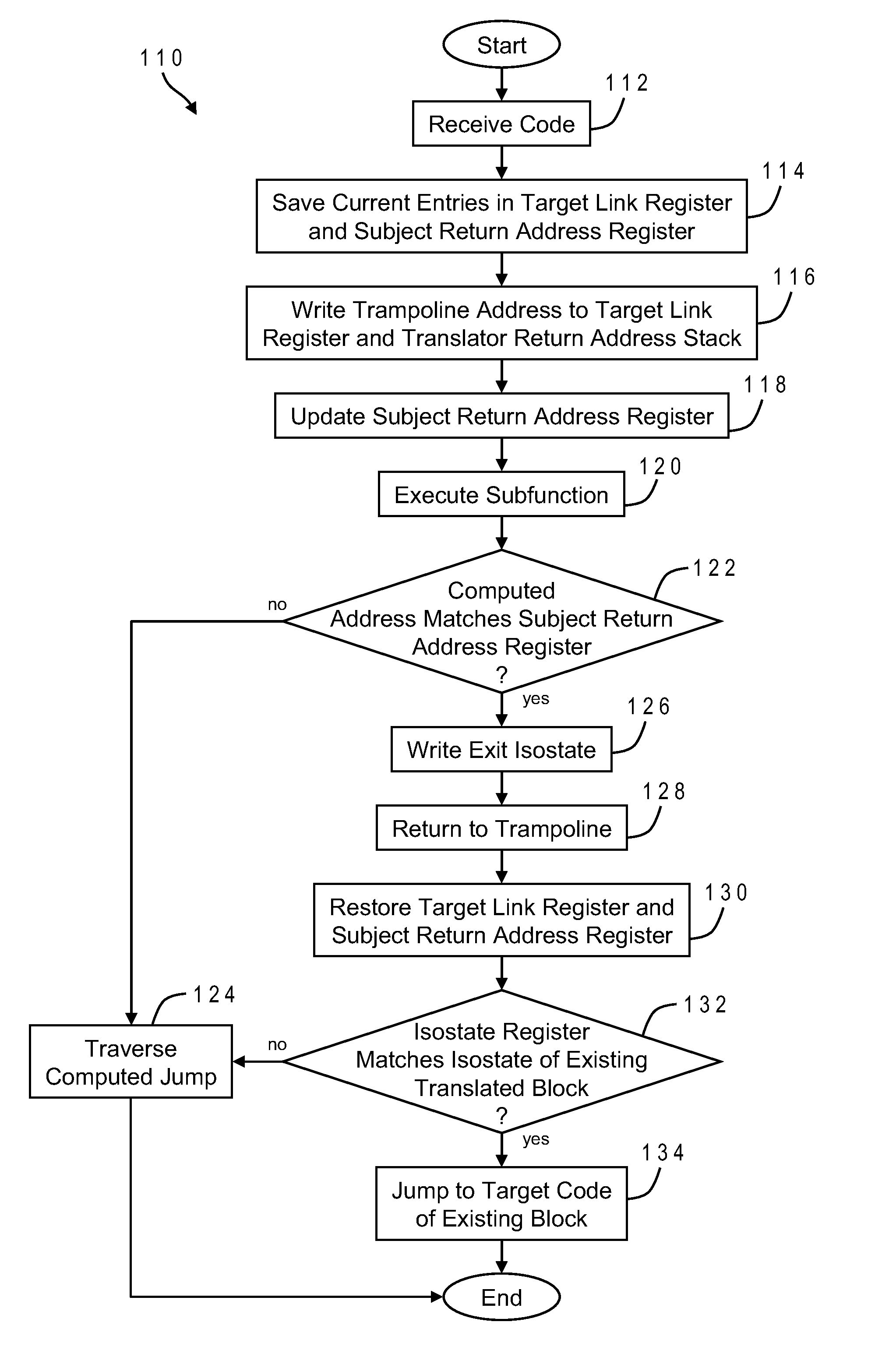

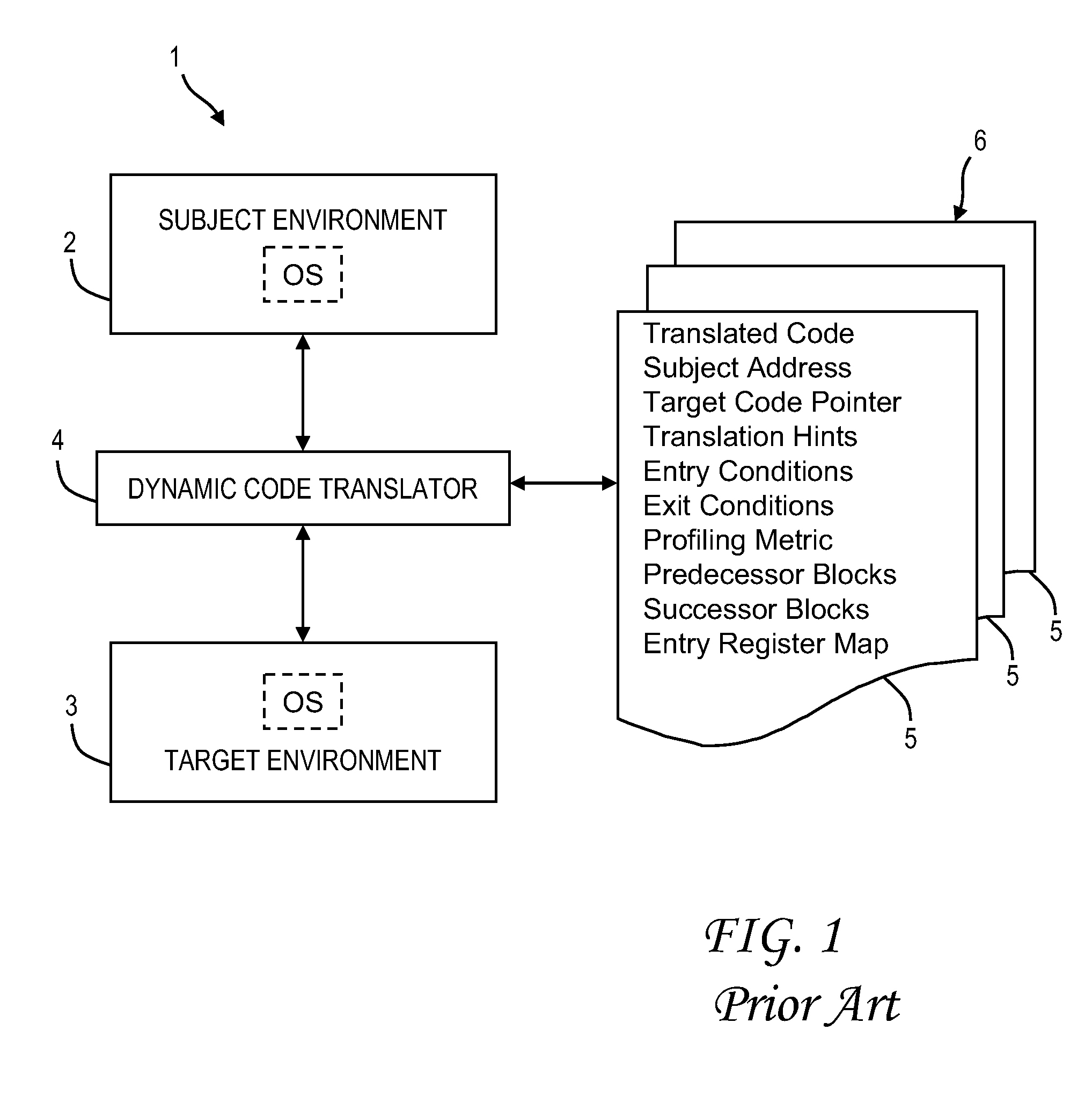

InactiveUS20130024675A1Digital computer detailsConcurrent instruction executionReturn address stackProcessor register

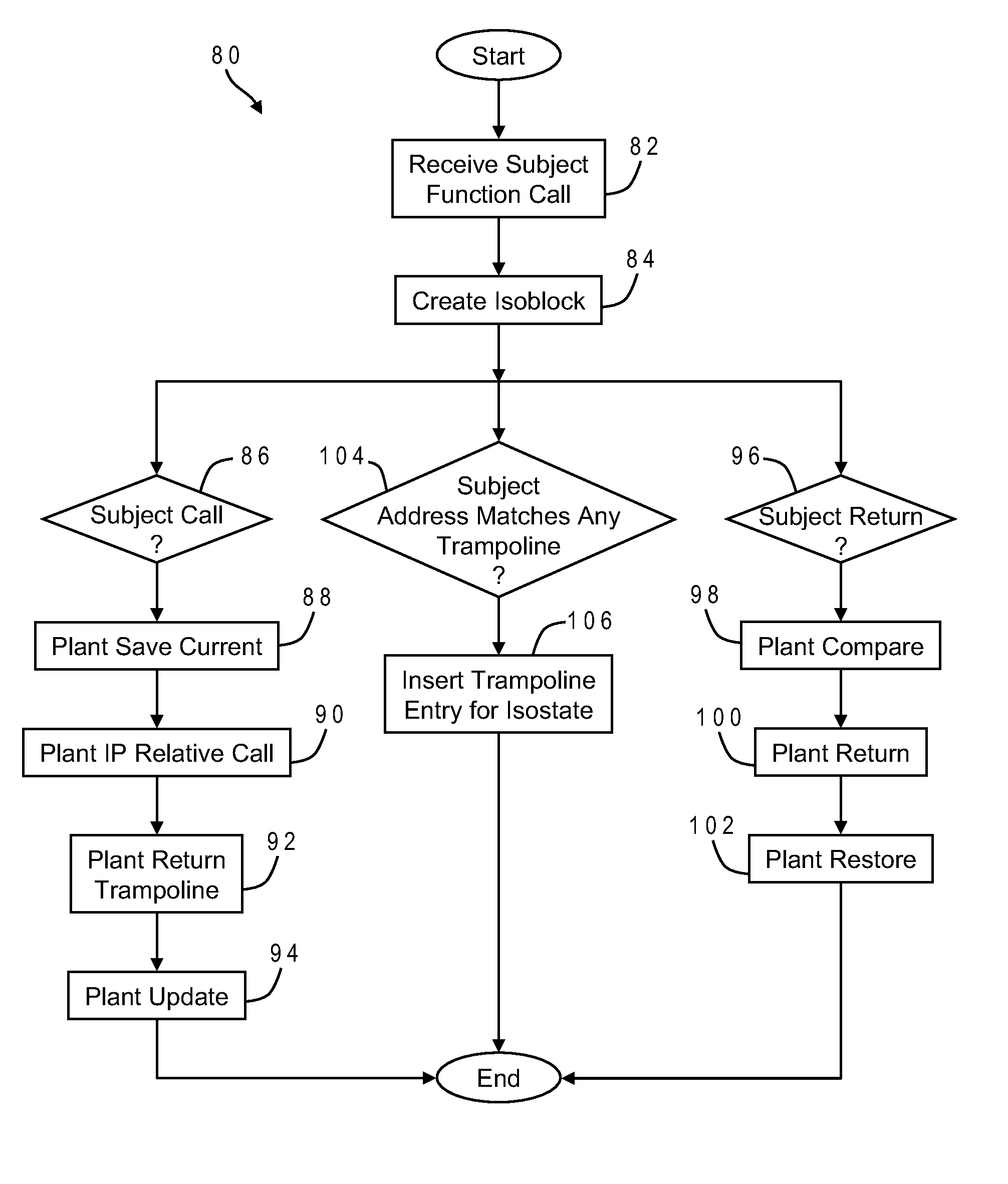

A dynamic code translator with isoblocking uses a return trampoline having branch instructions conditioned on different isostates to optimize return address translation, by allowing the hardware to predict that the address of a future return will be the address of trampoline. An IP relative call is inserted into translated code to write the trampoline address to a target link register and a target return address stack used by the native machine to predict return addresses. If a computed subject return address matches a subject return address register value, the current isostate of the isoblock is written to an isostate register. The isostate value in the isostate register is then used to select the branch instruction in the trampoline for the true subject return address. Sufficient code area in the trampoline instruction set can be reserved for a number of compare / branch pairs which is equal to the number of available isostates.

Owner:IBM CORP

Branch predicting apparatus and branch predicting method

ActiveUS7320066B2Digital computer detailsConcurrent instruction executionReturn address stackParallel computing

A branch history stores execution history information of branch instructions, and predicts presence of a branch instruction and a corresponding branch destination. A first return address stack stores, when an execution of a call instruction of a subroutine is completed, address information of a return destination of a corresponding return instruction. A second return address stack stores, when presence of a call instruction of a subroutine is predicted, address information of a return destination of a corresponding return instruction. An output selecting unit selects, when presence of a return instruction is predicted, if address information is stored in the second return address stack, the address information as a result of the branch prediction with a highest priority, and outputs the address information selected.

Owner:FUJITSU LTD

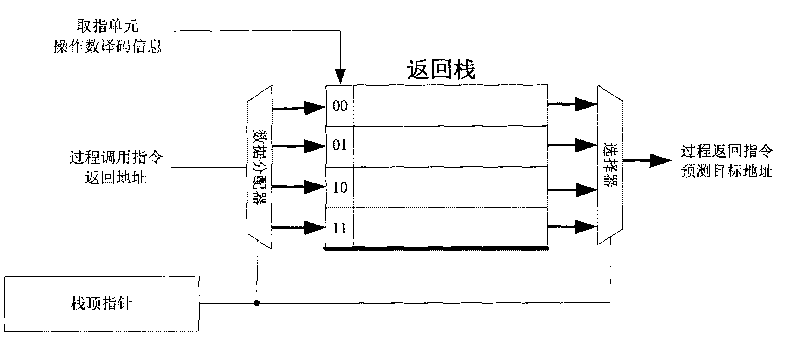

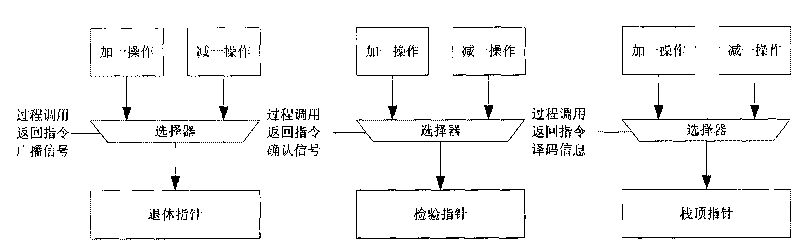

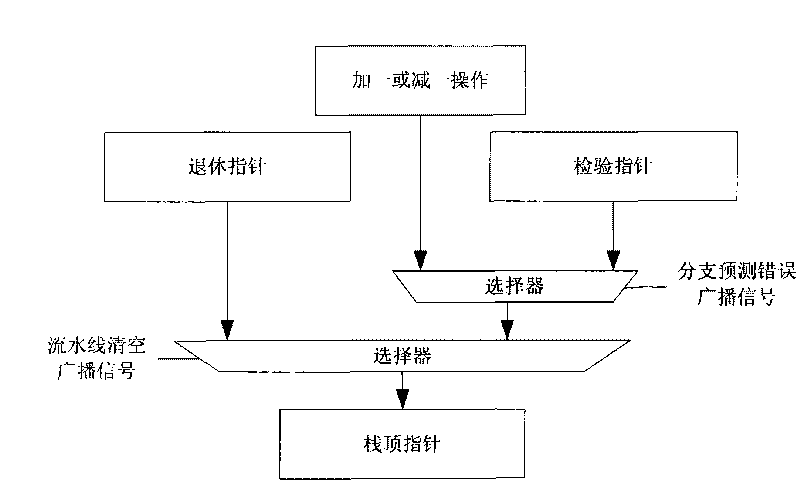

Realization method of return-address stack for supporting automatic error correction function

ActiveCN101727312AImprove forecast accuracyTo achieve the purpose of acceleratingConcurrent instruction executionReturn address stackBusiness forecasting

The invention discloses a realization method of a return-address stack for supporting an automatic error correction function, which comprises the steps of: 1) precoding a function calling instruction and a function returning instruction during prefetching the instructions, and pushing the tack and popping the stack to function returning address information according to a precoding result; and 2) setting the position of the current operation of the return-address stack when precoding an identification instruction of a stack top address stack needle; and 3) recording the status of the return-address stack after the function calling instruction and the function returning instruction are retired with a retired needle, and automatically recovering the stack top needle with the retired needle when emptying a flow line. The method can effectively improve the forecasting precision of the return of the function and improving the performance of a processor.

Owner:C SKY MICROSYST CO LTD

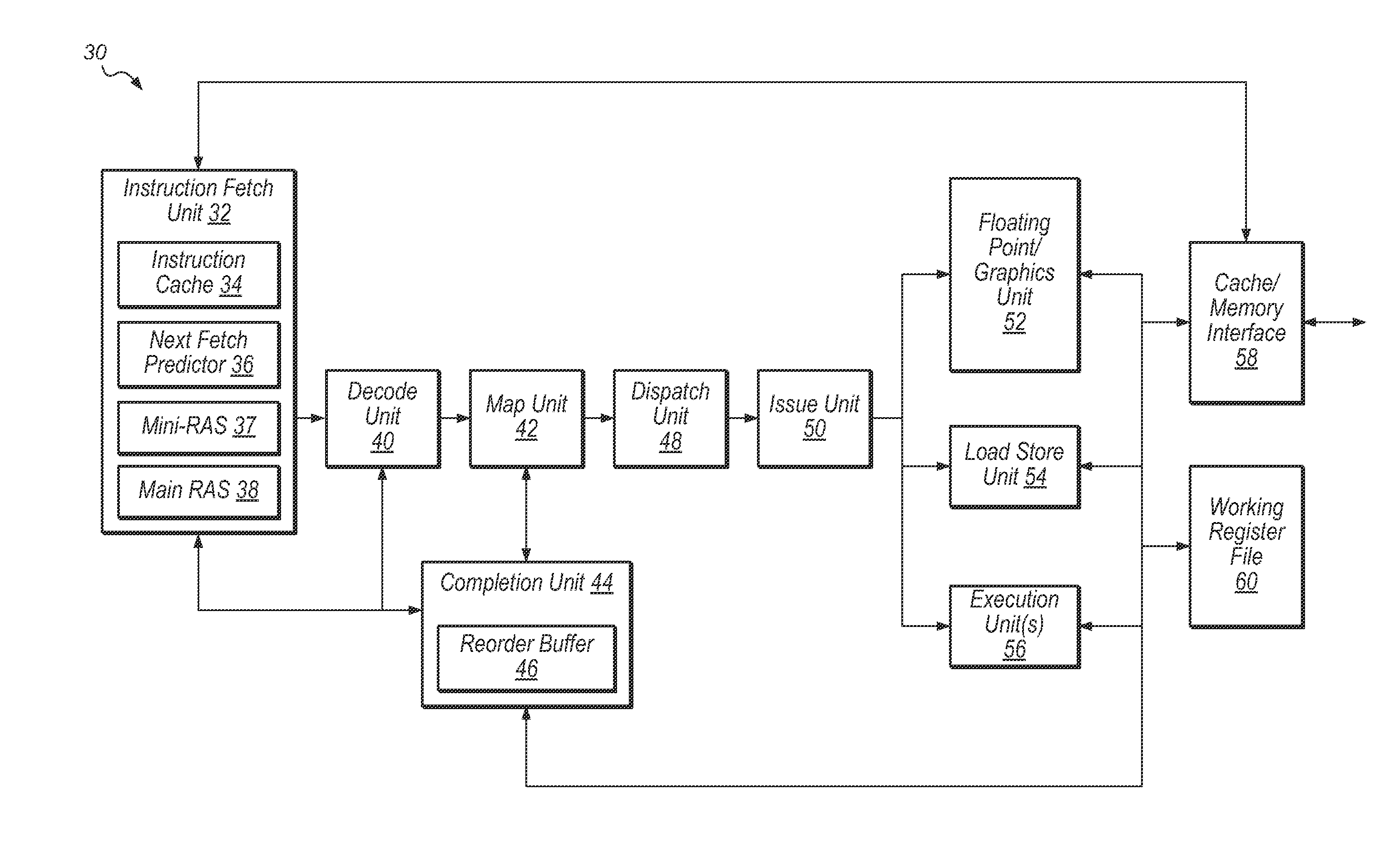

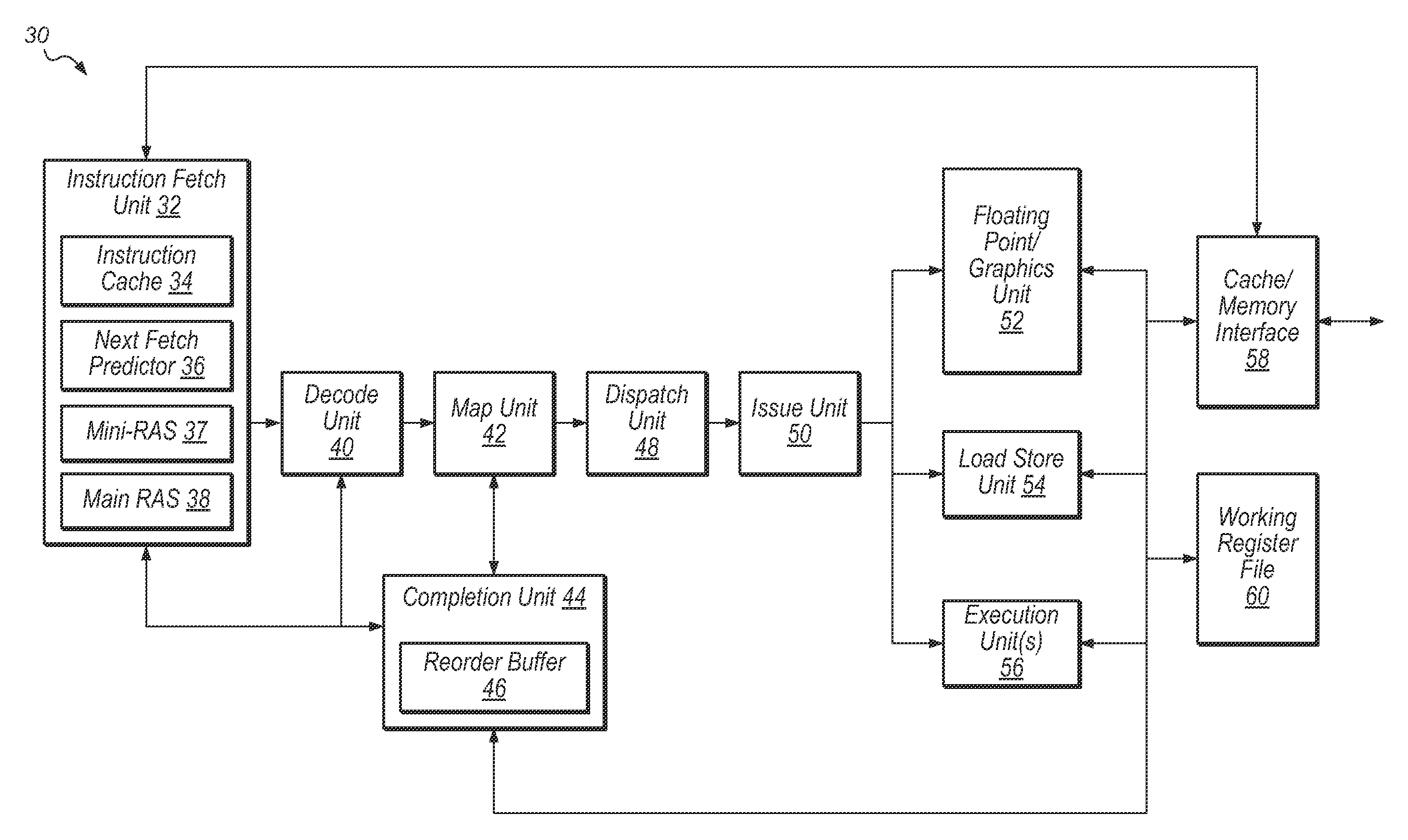

Next fetch predictor return address stack

ActiveUS20140344558A1Faster and accurate branch predictionQuick buildDigital computer detailsConcurrent instruction executionReturn address stackParallel computing

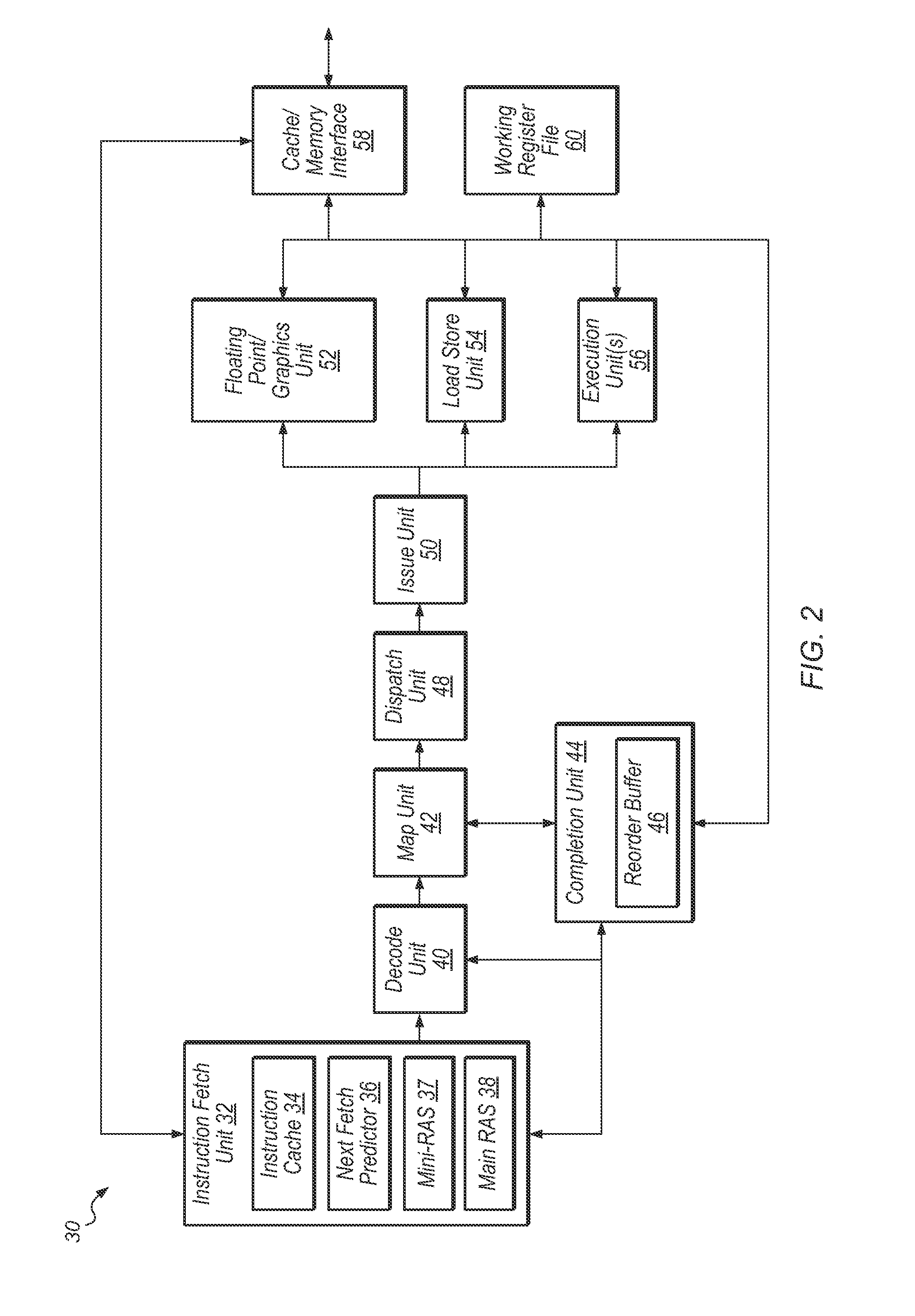

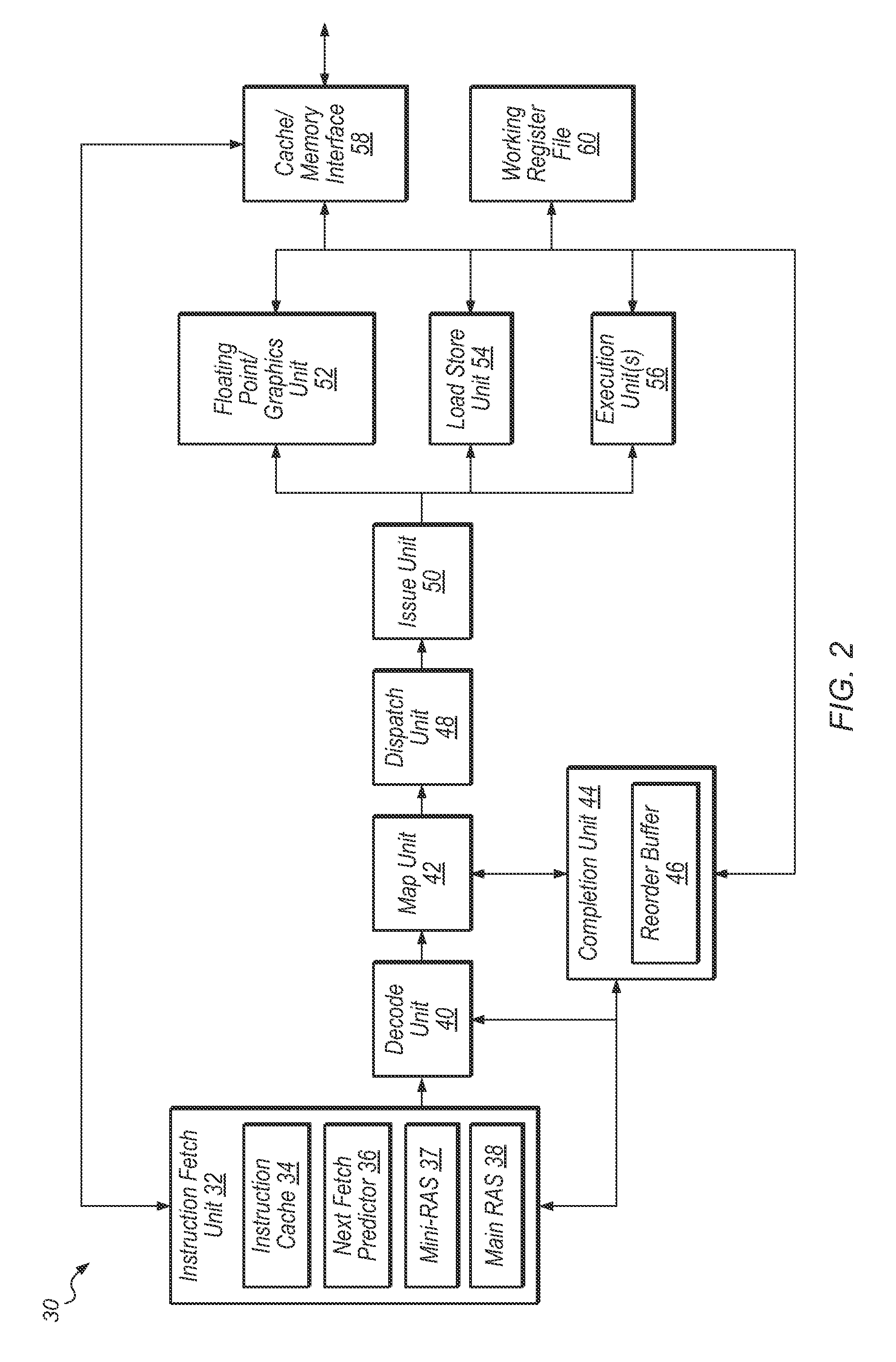

A system and method for efficient branch prediction. A processor includes a next fetch predictor to generate a fast branch prediction for branch instructions at an early pipeline stage. The processor also includes a main return address stack (RAS) at a later pipeline stage for predicting the target of return instructions. When a return instruction is encountered, the prediction from the next fetch predictor is replaced by the top of the main RAS. If there are any recent call or return instructions in flight toward the main RAS, then a separate prediction is generated by a mini-RAS.

Owner:APPLE INC

Return address stack recovery in a speculative execution computing apparatus

ActiveUS7836290B2Digital computer detailsSpecific program execution arrangementsSpeculative executionReturn address stack

Owner:ORACLE INT CORP

Branch prediction control device having return address stack and method of branch prediction

InactiveUS8250349B2Improve accuracyDigital computer detailsPlatform integrity maintainanceInformation processingReturn address stack

A branch prediction control device, in an information processing unit which performs a pipeline process, generates a branch prediction address used for verification of an instruction being speculatively executed. The branch prediction control device includes a first return address storage unit storing the prediction return address, a second return address storage unit storing a return address to be generated depending on an execution result of the call instruction, and a branch prediction address storage unit sending a stored prediction return address as a branch prediction address and storing the sent branch prediction address. When the branch prediction address differs from a return address, which is generated after executing a branch instruction or a return instruction, contents stored in the second return address storage unit are copied to the first return address storage unit.

Owner:RENESAS ELECTRONICS CORP

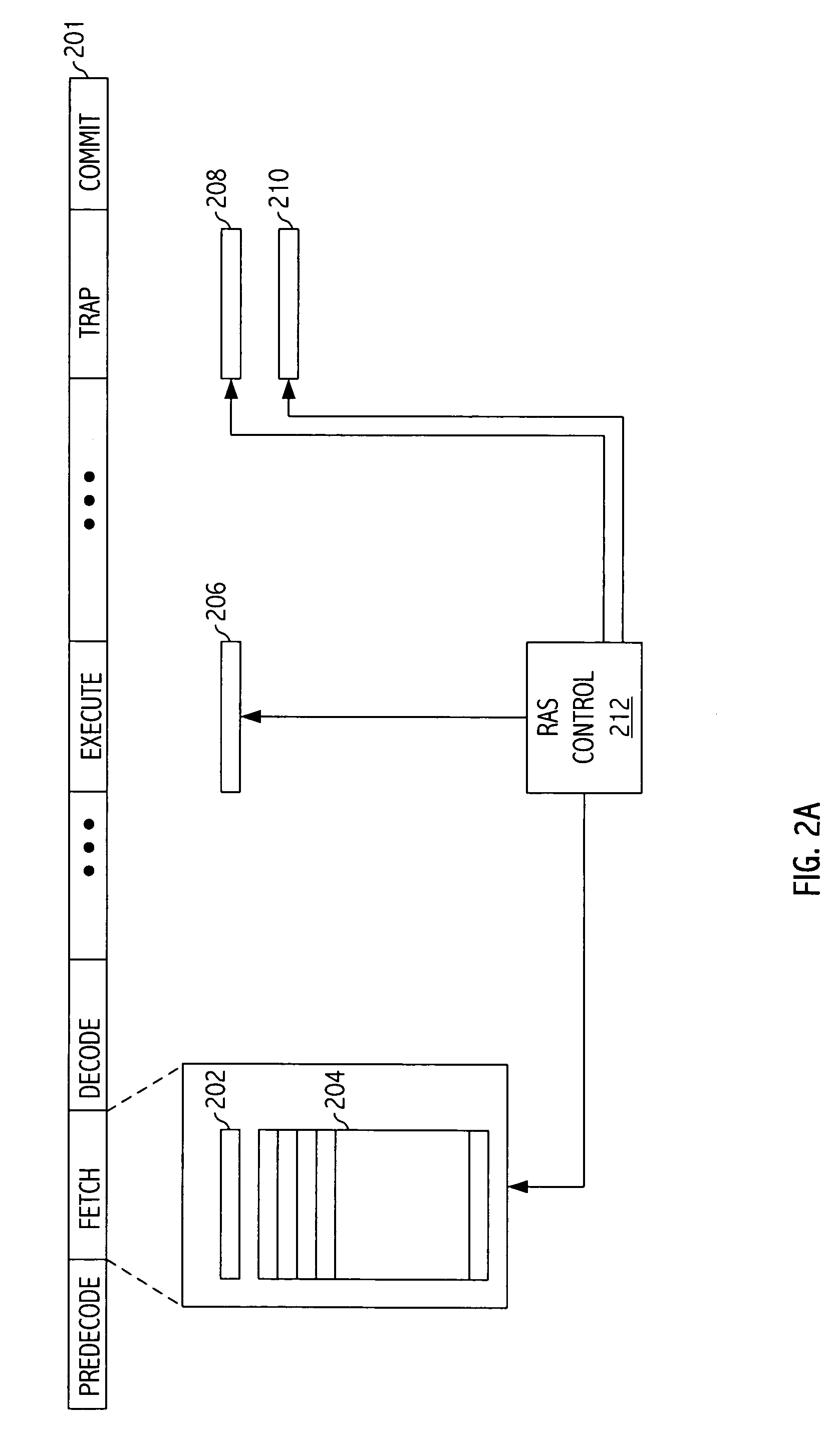

Return address stack recovery in a speculative execution computing apparatus

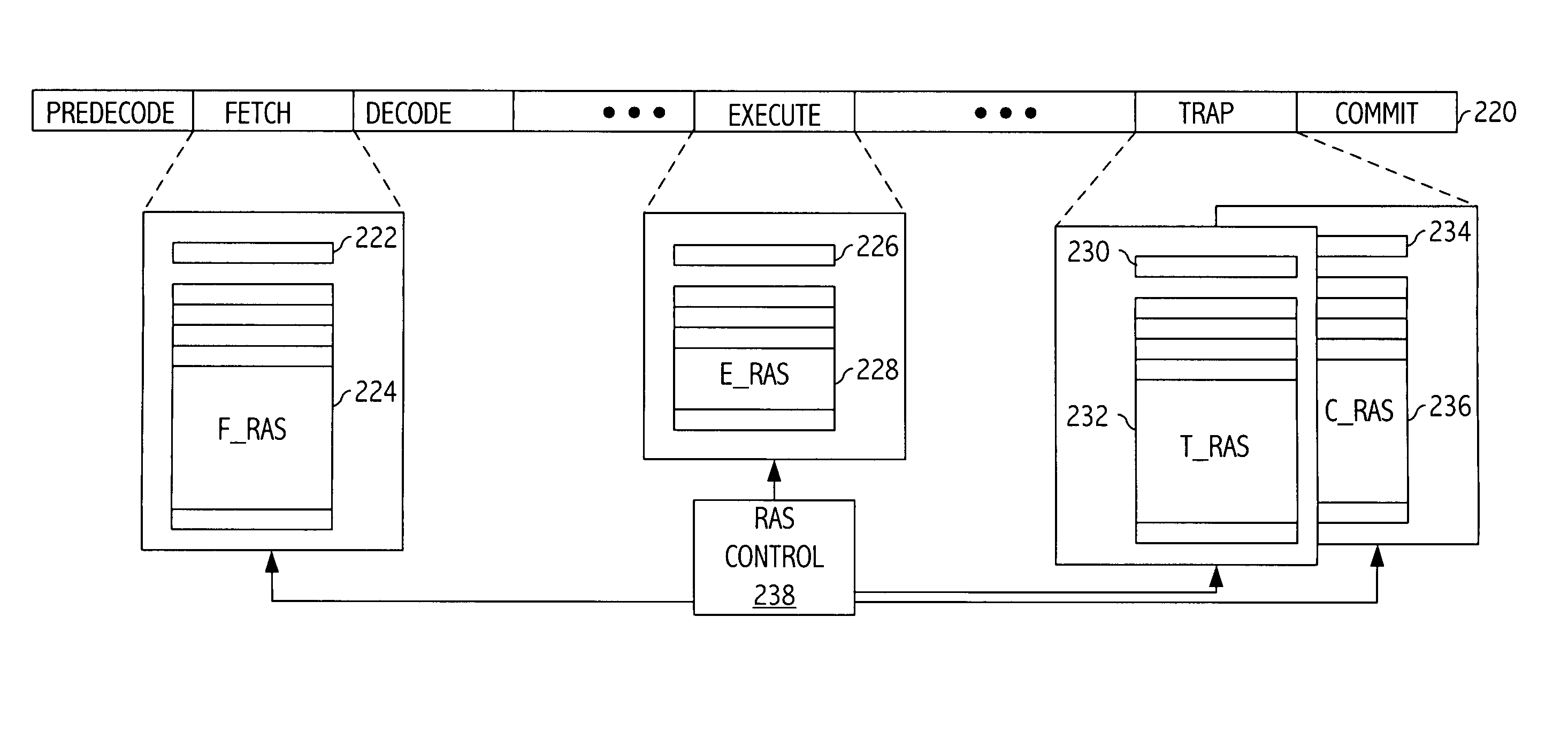

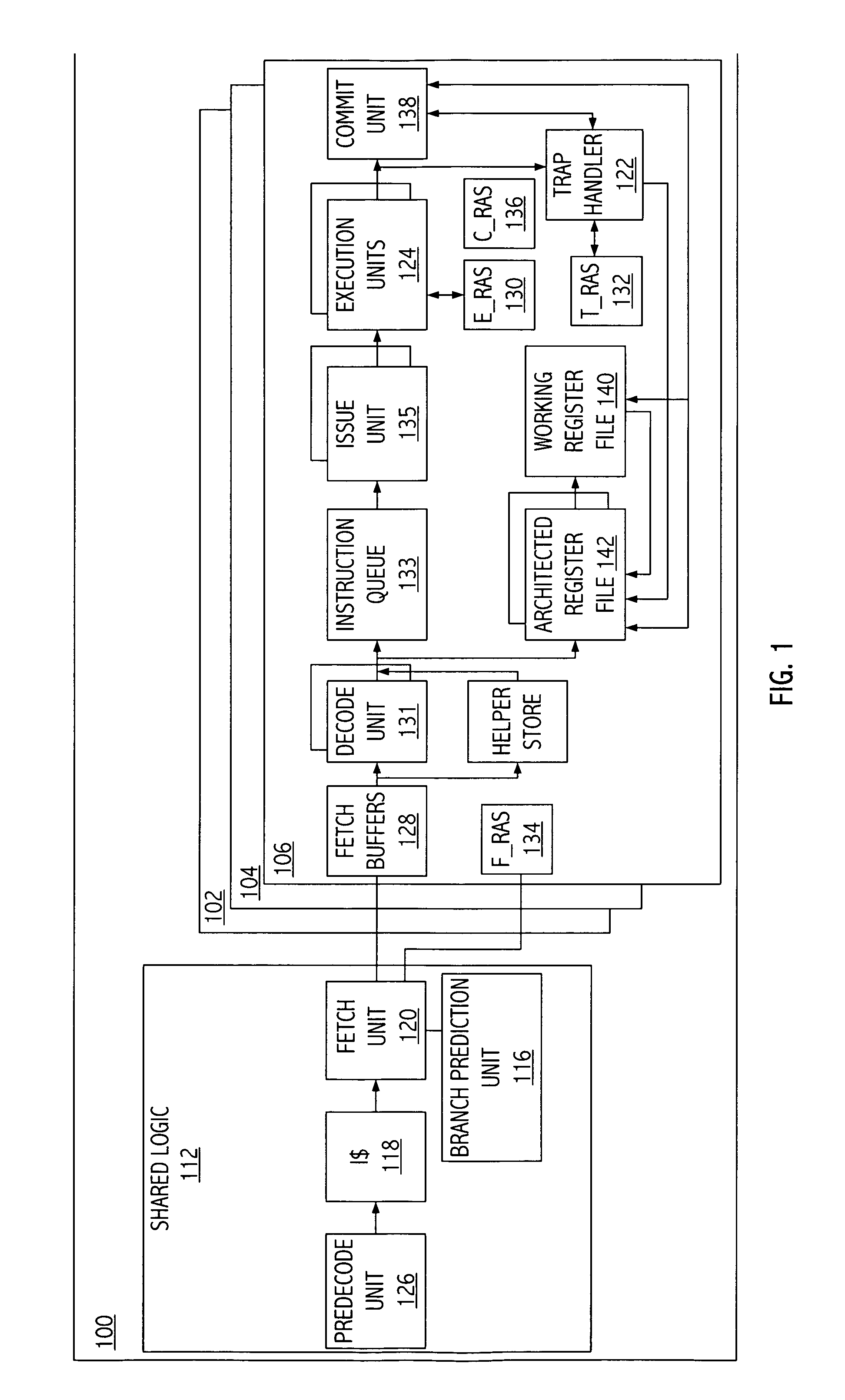

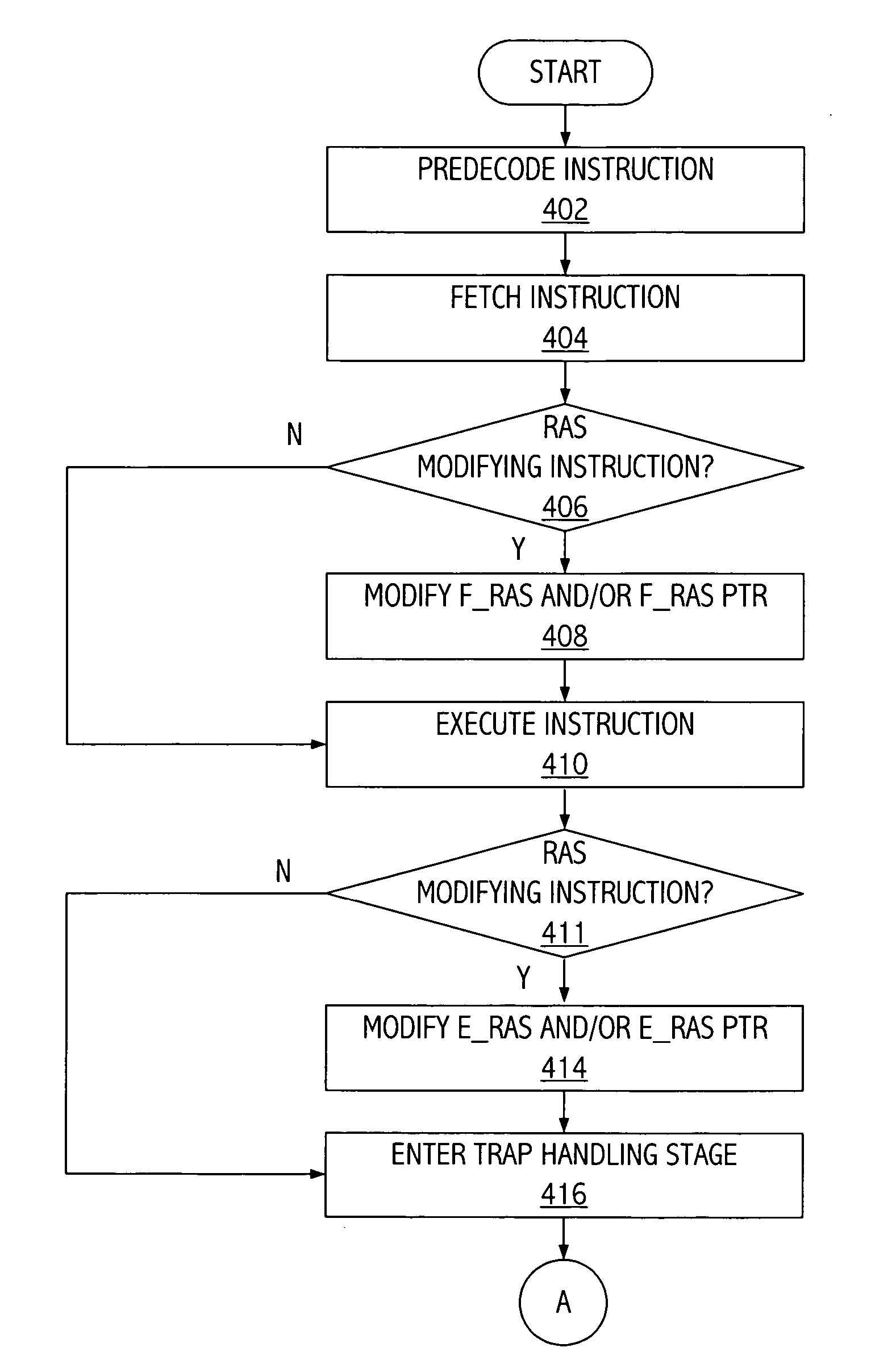

ActiveUS20070106888A1Digital computer detailsSpecific program execution arrangementsSpeculative executionReturn address stack

A technique recovers return address stack (RAS) content and restores alignment of a RAS top-of-stack (TOS) pointer for occurrences of mispredictions due to speculative operation, out-of-order instruction processing, and exception handling. In at least one embodiment of the invention, an apparatus includes a speculative execution processor pipeline, a first structure for maintaining return addresses relative to instruction flow at a first stage of the pipeline, at least a second structure for maintaining return addresses relative to instruction flow at a second stage of the pipeline. The second stage of the pipeline is deeper in the pipeline than the first stage. The apparatus includes circuitry operable to reproduce at least return addresses from the second structure to the first structure.

Owner:ORACLE INT CORP

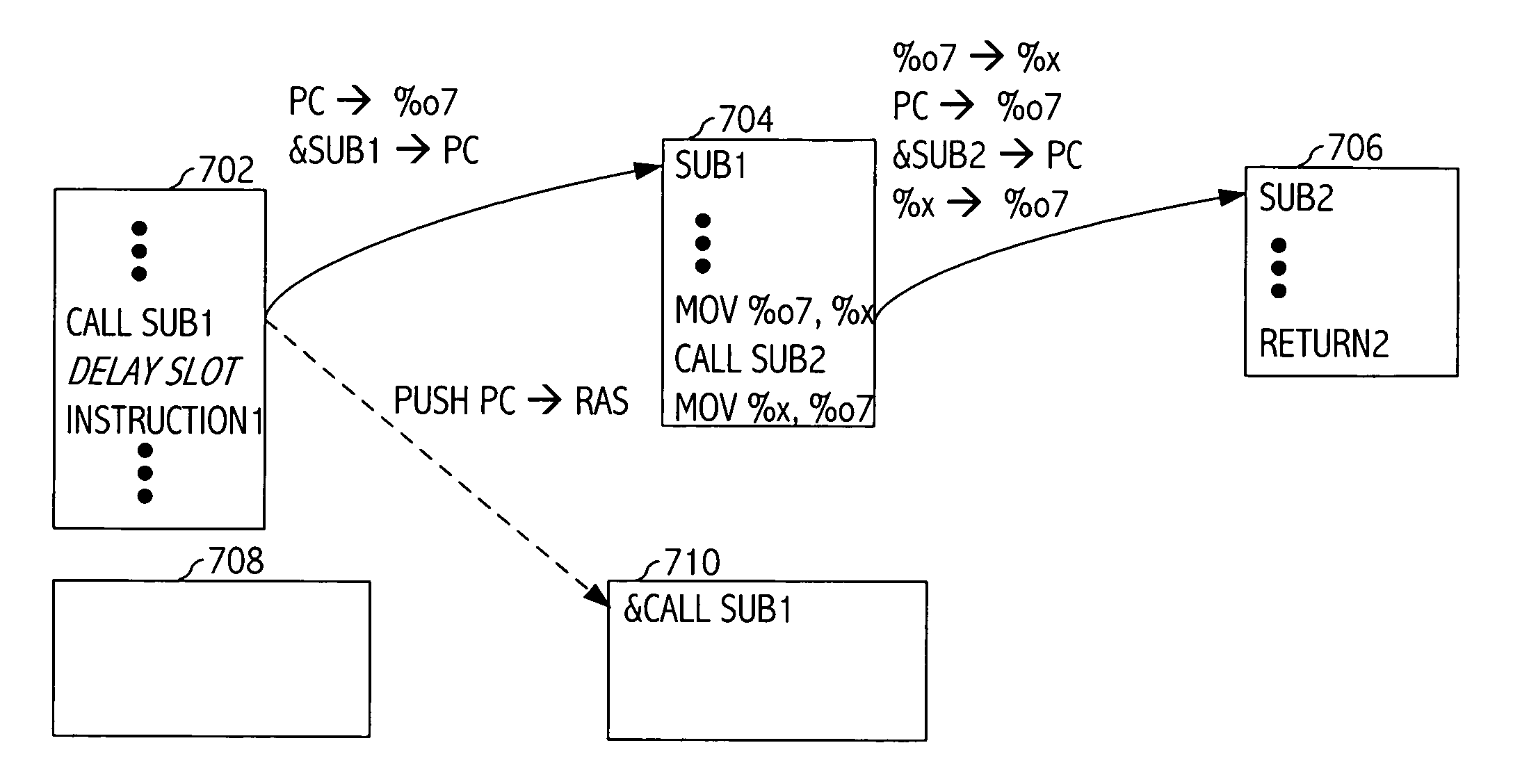

Mechanism for hardware tracking of return address after tail call elimination of return-type instruction

ActiveUS20070130451A1Digital computer detailsSpecific program execution arrangementsReturn address stackParallel computing

A technique maintains return address stack (RAS) content and alignment of a RAS top-of-stack (TOS) pointer upon detection of a tail-call elimination of a return-type instruction. In at least one embodiment of the invention, an apparatus includes a processor pipeline and at least a first return address stack for maintaining a stack of return addresses associated with instruction flow at a first stage of the processor pipeline. The processor pipeline is configured to maintain the first return address stack unchanged in response to detection of a tail-call elimination sequence of one or more instructions associated with a first call-type instruction encountered by the first stage. The processor pipeline is configured to push a return address associated with the first call-type instruction onto the first return address stack otherwise.

Owner:ORACLE INT CORP

Mechanism for hardware tracking of return address after tail call elimination of return-type instruction

ActiveUS7610474B2Digital computer detailsSpecific program execution arrangementsReturn address stackParallel computing

Owner:ORACLE INT CORP

Return address optimisation for a dynamic code translator

InactiveUS8893100B2Digital computer detailsNext instruction address formationReturn address stackProcessor register

Owner:INT BUSINESS MASCH CORP

Dynamic identification of stack frames

ActiveUS11188470B2Limited accessMemory architecture accessing/allocationDigital data protectionReturn address stackAlgorithm

A method, system and product, configured to perform: during an execution of a program, obtaining boundaries of a stack frame of a function that is currently present in a stack, wherein said obtaining the boundaries comprises: obtaining a return address of the function in the stack; determining a length of the function using a mapping of return addresses of one or more functions in the program and corresponding lengths of the one or more functions; and determining the boundaries of the stack frame of the function based on a value of a stack pointer of the stack and based on the length of the function; based on the boundaries of the stack frame of the function, determining that the stack frame is overflown; and in response to said determining that the stack frame is overflown, performing a responsive action.

Owner:JFROG LTD

Return address optimisation for a dynamic code translator

InactiveUS20130024674A1Digital computer detailsSoftware simulation/interpretation/emulationReturn address stackProcessor register

A dynamic code translator with isoblocking uses a return trampoline having branch instructions conditioned on different isostates to optimize return address translation, by allowing the hardware to predict that the address of a future return will be the address of trampoline. An IP relative call is inserted into translated code to write the trampoline address to a target link register and a target return address stack used by the native machine to predict return addresses. If a computed subject return address matches a subject return address register value, the current isostate of the isoblock is written to an isostate register. The isostate value in the isostate register is then used to select the branch instruction in the trampoline for the true subject return address. Sufficient code area in the trampoline instruction set can be reserved for a number of compare / branch pairs which is equal to the number of available isostates.

Owner:IBM CORP

Branch predicting apparatus and branch predicting method

InactiveUS7757071B2Digital computer detailsSpecific program execution arrangementsReturn address stackReservation station

Owner:FUJITSU LTD

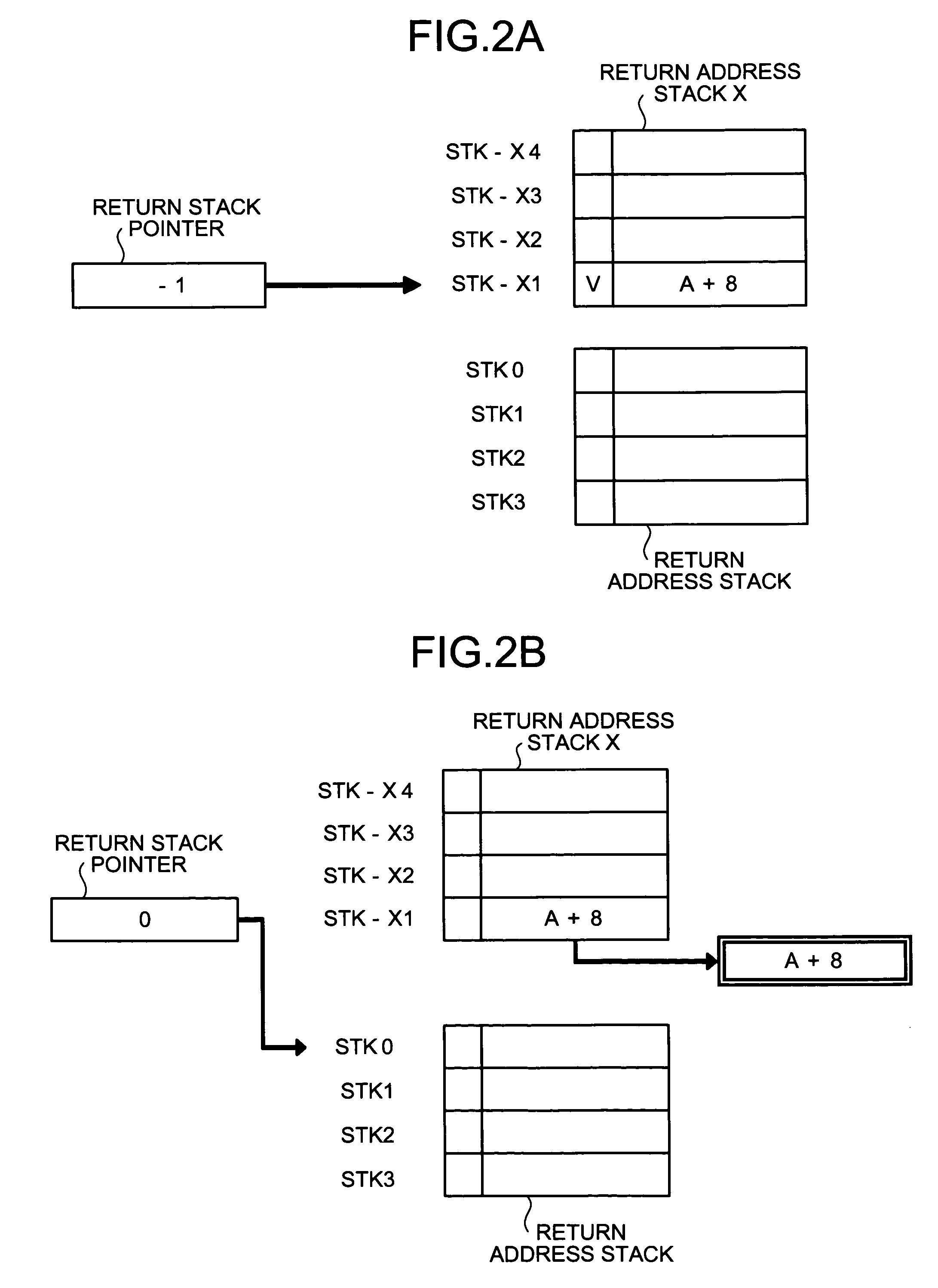

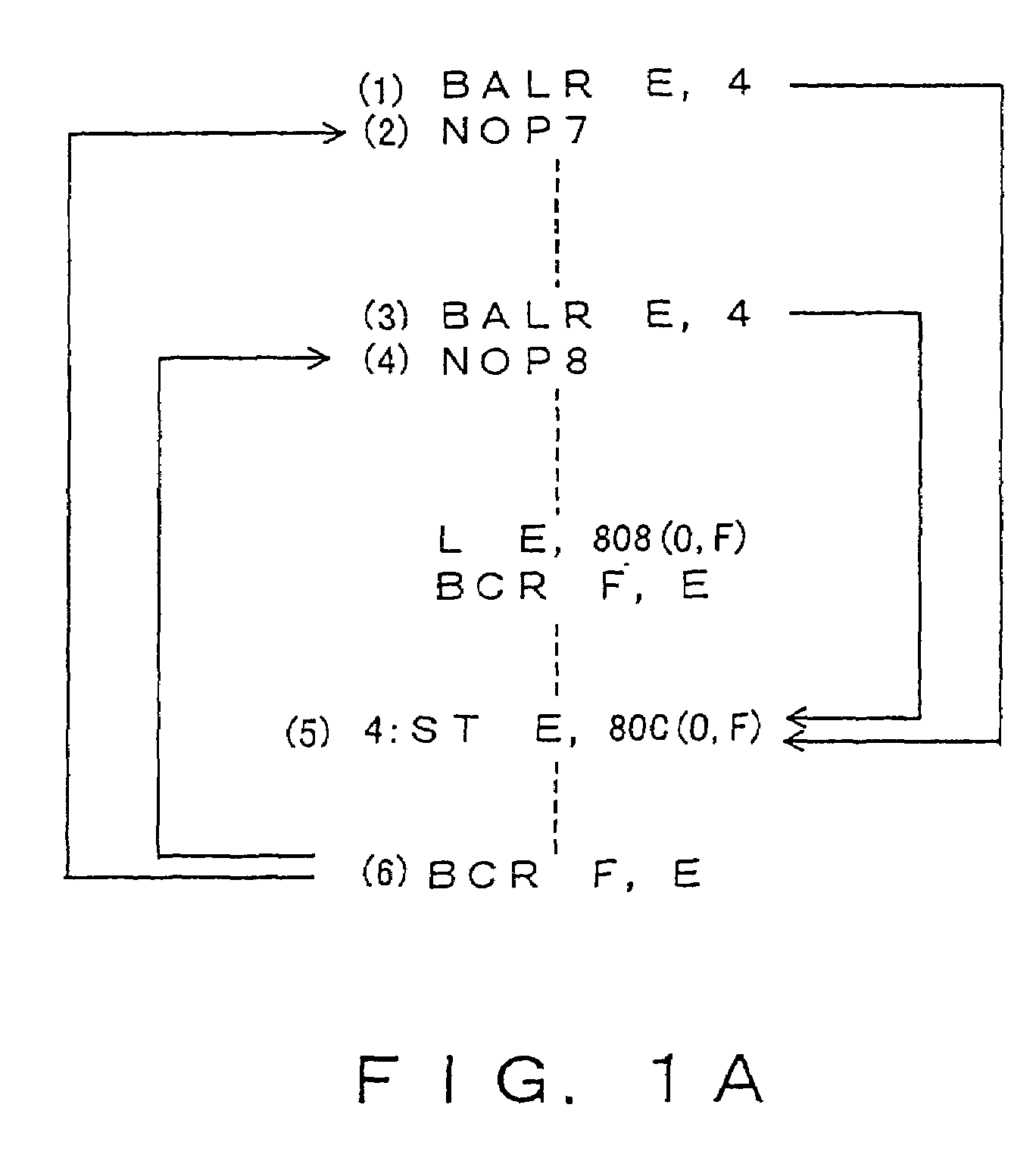

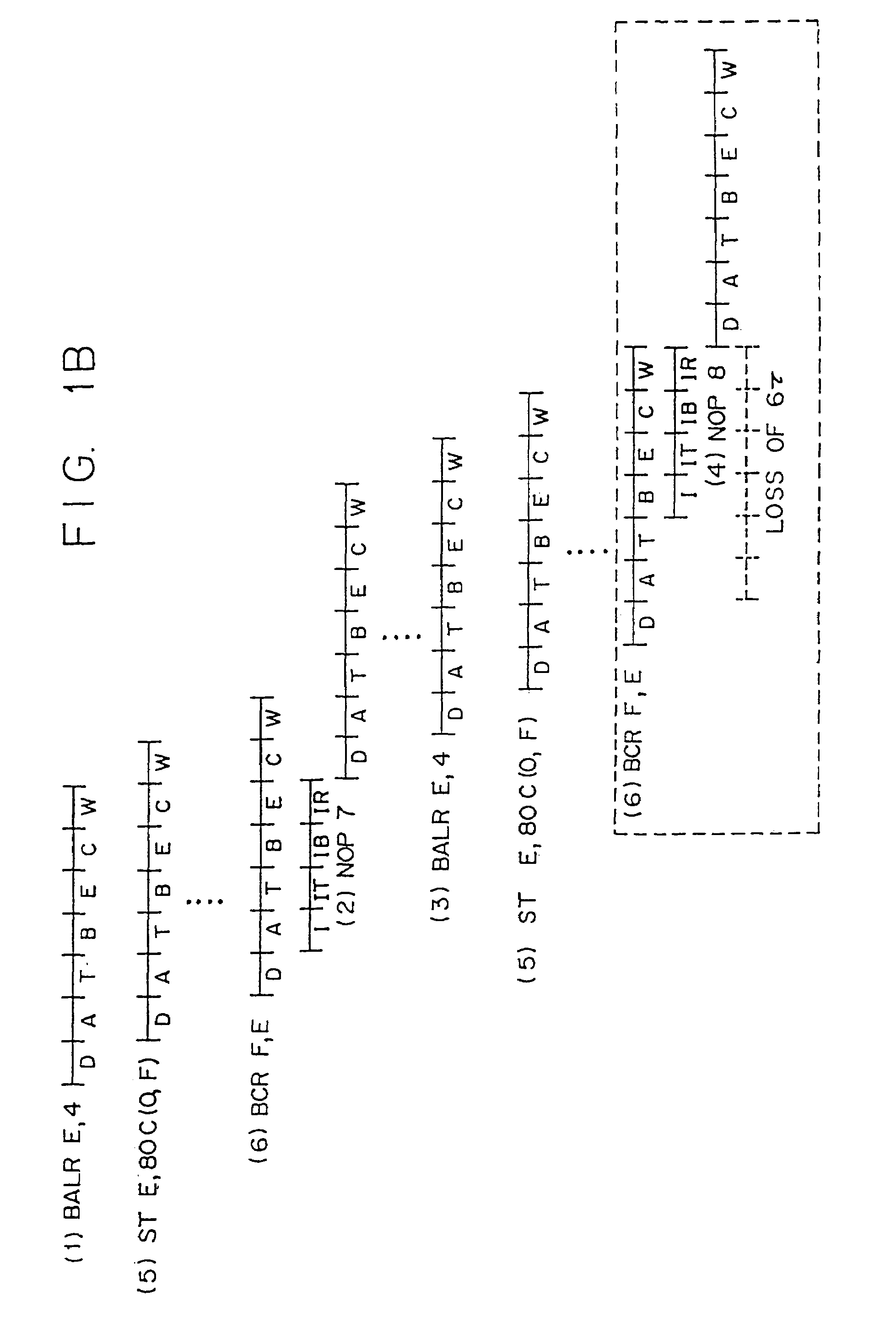

Predicted return address selection upon matching target in branch history table with entries in return address stack

InactiveUS20050278516A1High speed machiningDigital computer detailsNext instruction address formationInformation processingReturn address stack

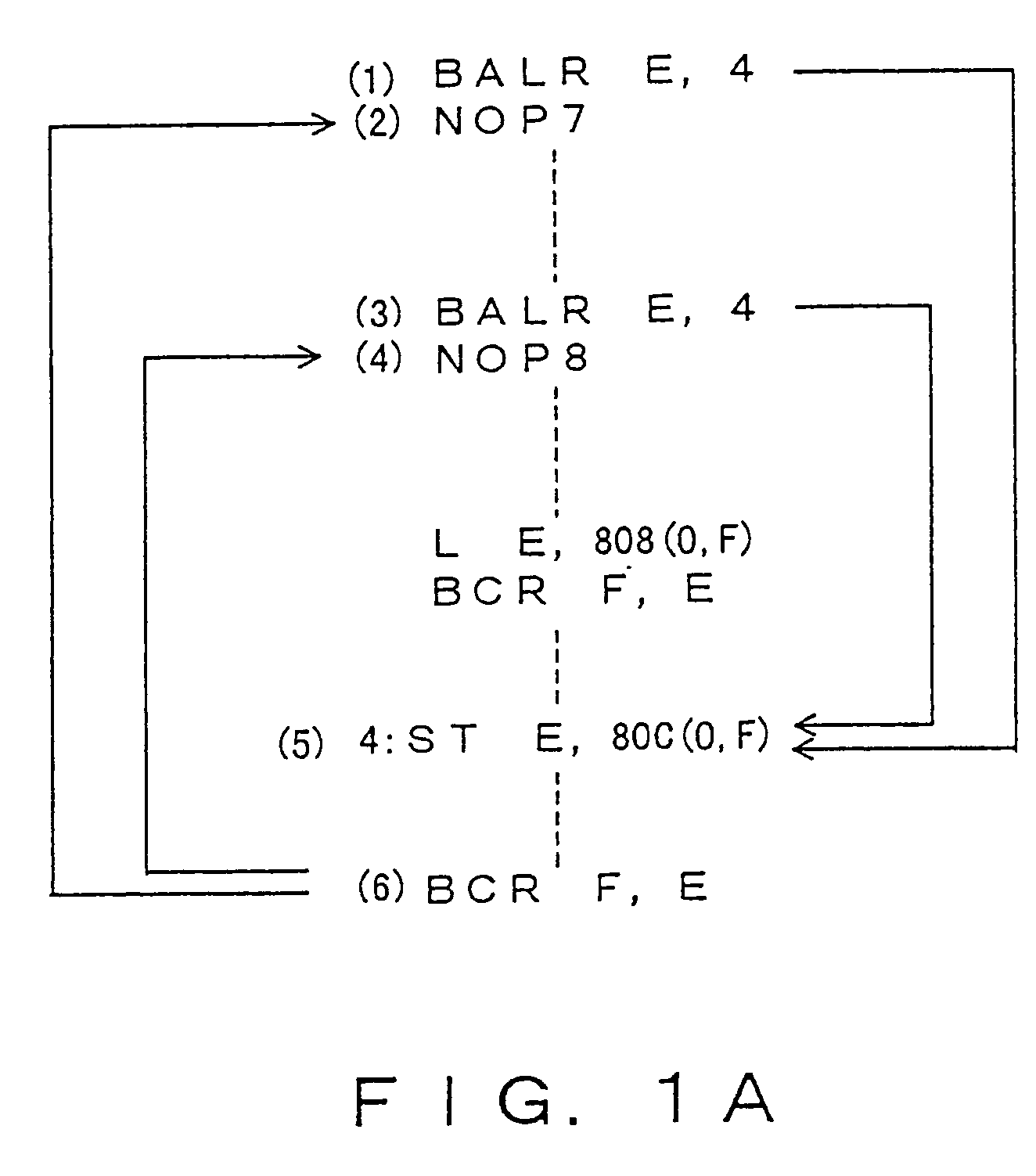

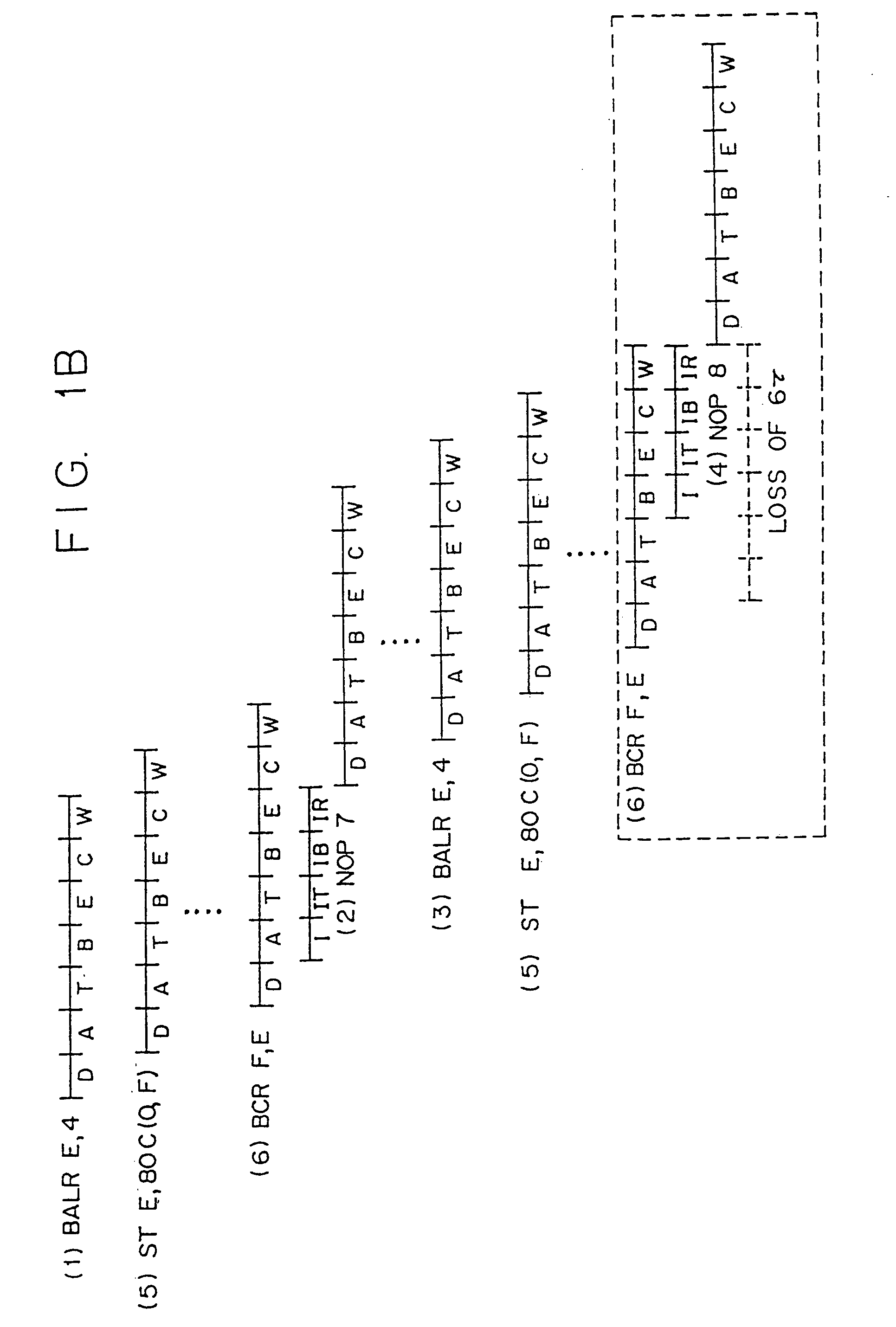

An information processing apparatus is capable of speculatively performing an execution, such as a pipeline / superscalar / out-of-order execution and equipped with a branch prediction mechanism (a branch history). The information processing apparatus, in order to process an instruction sequence that includes a subroutine at a high speed, is further equipped with a return address stack, of which the stack operation is activated at a time of completing execution of an subroutine call / return correspondent instruction and an entry designating unit (pointer), in order to adjust a time difference resulting from an instruction fetch being executed prior to completing an instruction, pointing to a position relative to the stack front and adjusting a time difference between an instruction fetch performed speculatively in advance and completion of an instruction both at a time of completing execution of a branch instruction that is correspondent to a subroutine call / return and at a time of predicting a subroutine call / return in synchrony to the instruction fetch. An entry position correspondent to a stack position pointed to by the entry designation unit is adopted as a subroutine call / return prediction address and consequently the prediction of the subroutine return address becomes more accurate and the processing speed becomes higher.

Owner:FUJITSU LTD

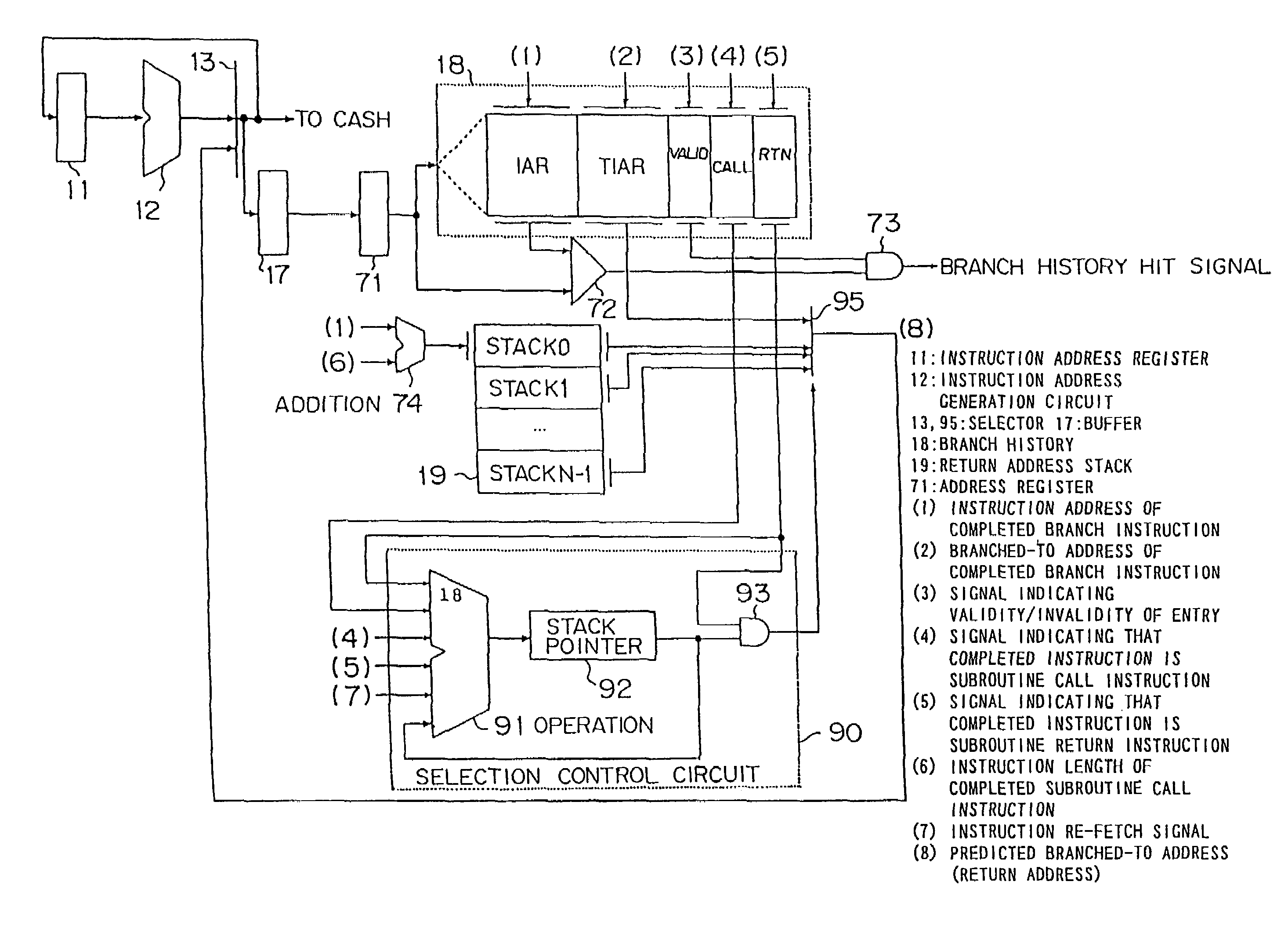

Predicted return address from return stack entry designated by computation unit with multiple inputs including return hit flag and re-fetch signal

InactiveUS7350062B2Digital computer detailsNext instruction address formationInformation processingReturn address stack

An information processing apparatus is capable of speculatively performing an execution, such as a pipeline / superscalar / out-of-order execution and equipped with a branch prediction mechanism (a branch history). The information processing apparatus, in order to process an instruction sequence that includes a subroutine at a high speed, is further equipped with a return address stack, of which the stack operation is activated at a time of completing execution of an subroutine call / return correspondent instruction and an entry designating unit (pointer), in order to adjust a time difference resulting from an instruction fetch being executed prior to completing an instruction, pointing to a position relative to the stack front and adjusting a time difference between an instruction fetch performed speculatively in advance and completion of an instruction both at a time of completing execution of a branch instruction that is correspondent to a subroutine call / return and at a time of predicting a subroutine call / return in synchrony to the instruction fetch. An entry position correspondent to a stack position pointed to by the entry designation unit is adopted as a subroutine call / return prediction address and consequently the prediction of the subroutine return address becomes more accurate and the processing speed becomes higher.

Owner:FUJITSU LTD

Next fetch predictor return address stack

ActiveUS9405544B2Concurrent instruction executionMemory systemsReturn address stackParallel computing

A system and method for efficient branch prediction. A processor includes a next fetch predictor to generate a fast branch prediction for branch instructions at an early pipeline stage. The processor also includes a main return address stack (RAS) at a later pipeline stage for predicting the target of return instructions. When a return instruction is encountered, the prediction from the next fetch predictor is replaced by the top of the main RAS. If there are any recent call or return instructions in flight toward the main RAS, then a separate prediction is generated by a mini-RAS.

Owner:APPLE INC

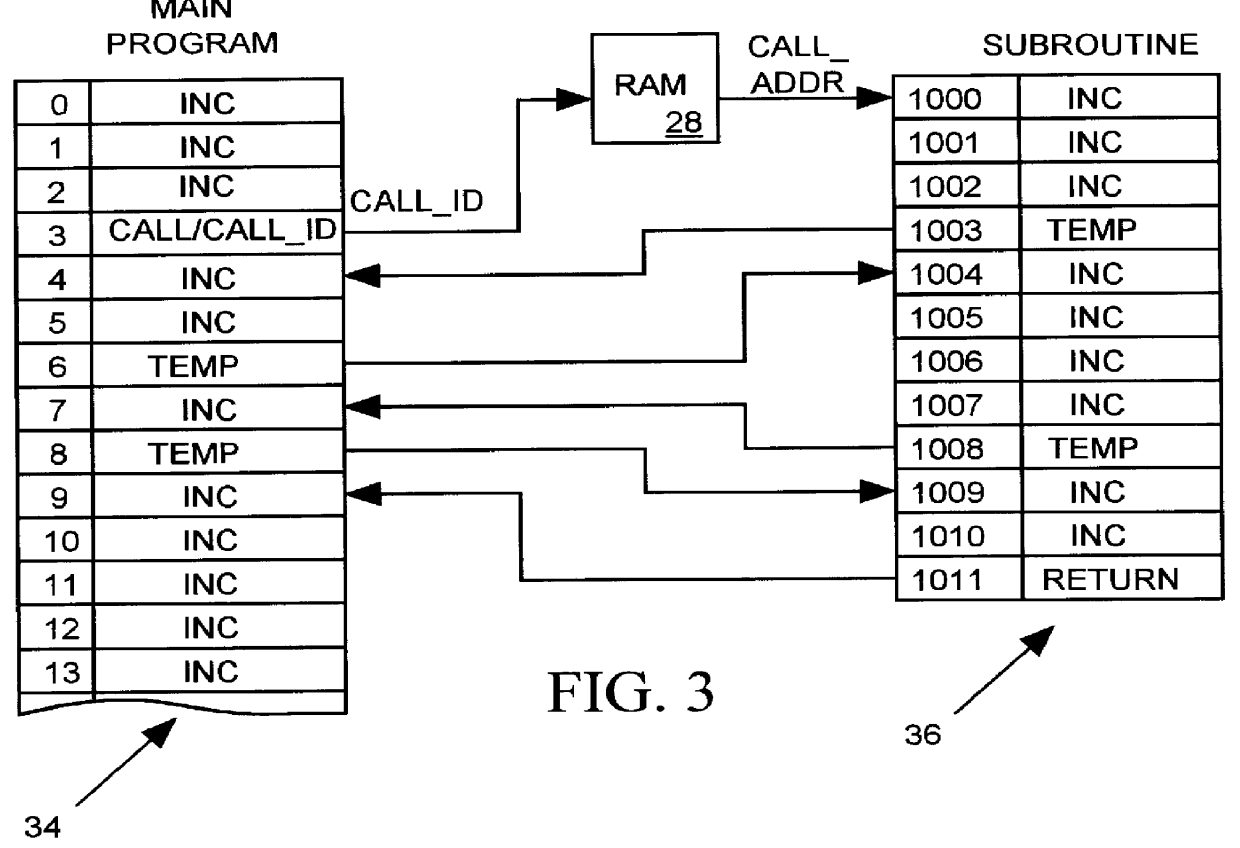

Instruction processing pattern generator controlling an integrated circuit tester

InactiveUS6154865ADigital circuit testingDetecting faulty computer hardwareInstruction memoryReturn address stack

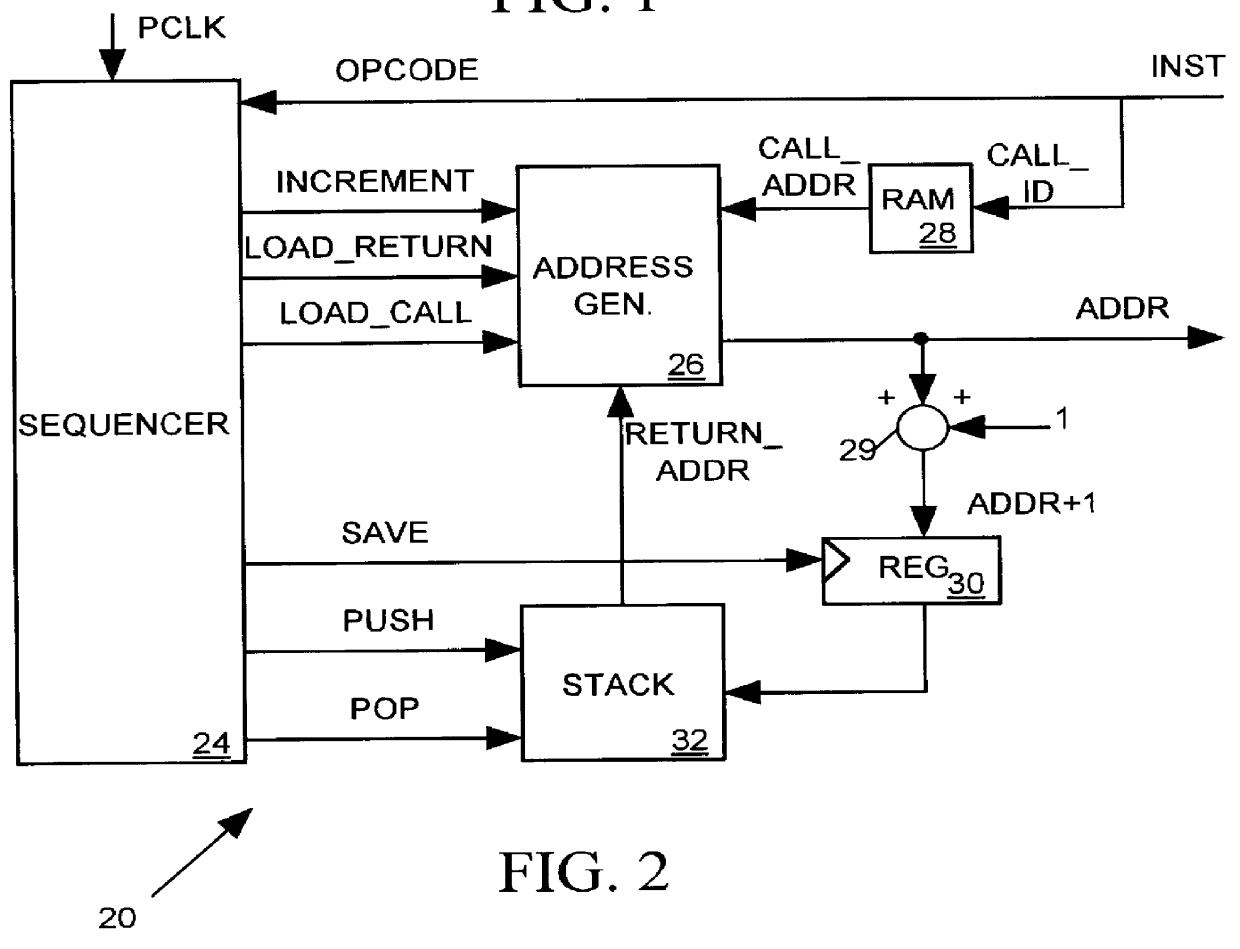

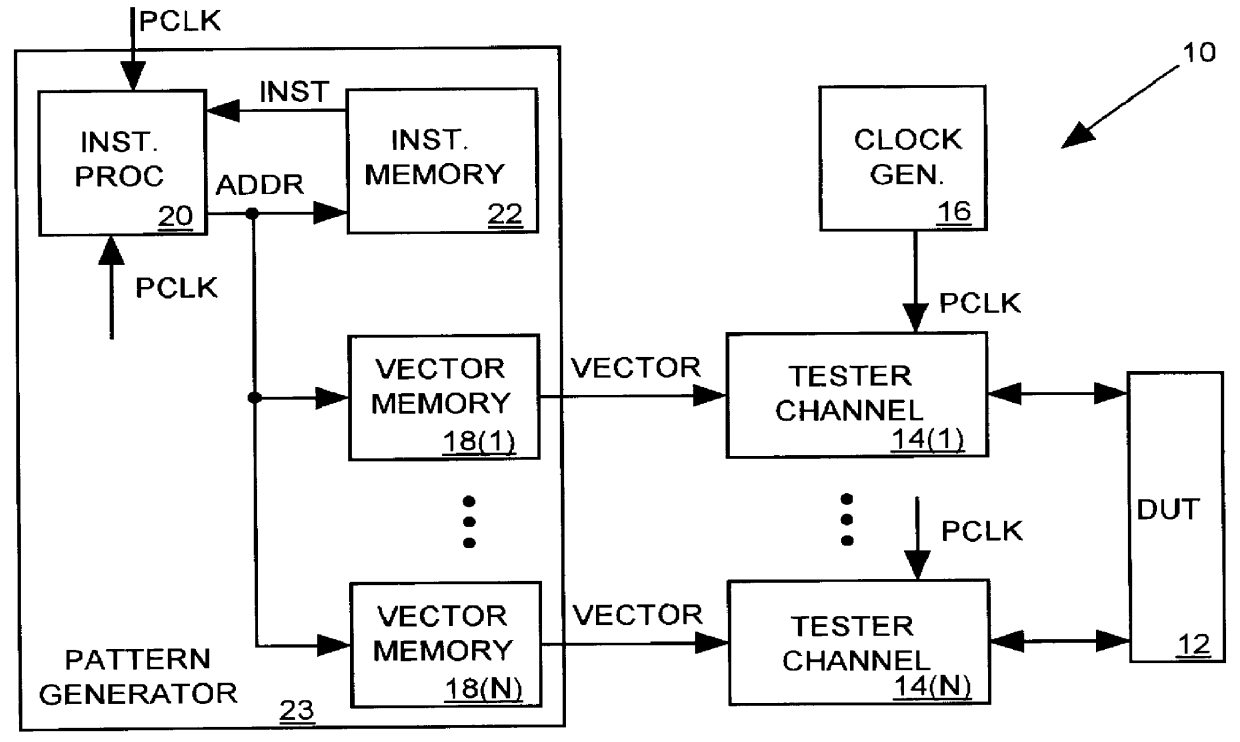

A pattern generator for an integrated circuit tester includes an instruction memory storing addressable instructions (INST) and reading out each instruction when addressed by an address (ADDR) supplied as input thereto. An instruction processor receives each instruction read out of the instruction memory and alters the address input to the instruction memory in accordance with the received instruction so that the instruction memory reads out a next instruction. The instruction processor, which includes a conventional return address stack, is capable of executing conventional address increment, call and return instructions. The instruction processor is also capable of executing a temporary return instruction (TEMP) by incrementing its current address output to produce a new return address, by setting its address output to the value of a return address previously saved in the stack, by popping the saved return address from the stack, and by pushing the new return address onto the stack. Temporary return instructions enable instruction program flow to pass back and forth between a main program and a called subroutine.

Owner:CREDENCE SYSTEMS

Processor and method for recovering global history shift register and return address stack thereof by determining a removal range of a branch recovery table

ActiveUS8078851B2Improve accuracyImprove efficiencyDigital computer detailsNext instruction address formationShift registerReturn address stack

A method for recovering global history shift register (GHSR) and return address stack (RAS) is provided, which is applicable to an instruction pipeline of a processor and includes the following steps. First, provide a branch recovery table (BRT) and a backup stack. Whenever a branch instruction enters a predetermined stage of the instruction pipeline, add a record in the BRT according to the branch instruction. Whenever a return address is popped from the RAS of the instruction pipeline, push the return address into the backup stack. When flushing the instruction pipeline, determine a removal range of the BRT according to the condition which triggers the pipeline flush. Recover the RAS according to the records in the removal range and the backup stack. Remove all records in the removal range. Recover the GHSR of the instruction pipeline according to the removed records.

Owner:FARADAY TECH CORP

A Classified Hybrid Branch Prediction System Based on Sparc V8 Architecture

ActiveCN105718241BExpand coverageOptimal Branch Prediction SchemeNext instruction address formationMemory systemsReturn address stackTransformation algorithm

The invention discloses an SPARC V8 system structure based classified type mixed branch prediction system. Firstly, a branch target buffer is queried according to PC values of instructions at an instruction fetching stage to obtain branch instruction types; the branch instructions are dispatched to respective prediction modules; a return address stack (RAS) with a dynamic configuration counter is used in skip branch prediction; a complementary prediction method is used in indirect branch prediction; a tag recording correctness of previous branch prediction in a conditional branch target buffer (CBTB) adopts a partial skip three-state conversion algorithm in conditional branch prediction; decoding result information of the instructions are recorded in a prediction information table (PIT) at a decoding stage; a judgment is made at an execution stage; if a prediction result of the branch instructions is that the skip occurs, the result judgment is made by using a skip prediction result arbiter Arbiter_T; and if the prediction result of the branch instructions is that the skip does not occur, the result judgment is made by using a non-skip prediction result arbiter Arbiter_N. Therefore, the instruction delay influence of the branch instructions on an assembly line is eliminated and the execution efficiency of a processor is improved.

Owner:BEIJING MXTRONICS CORP +1

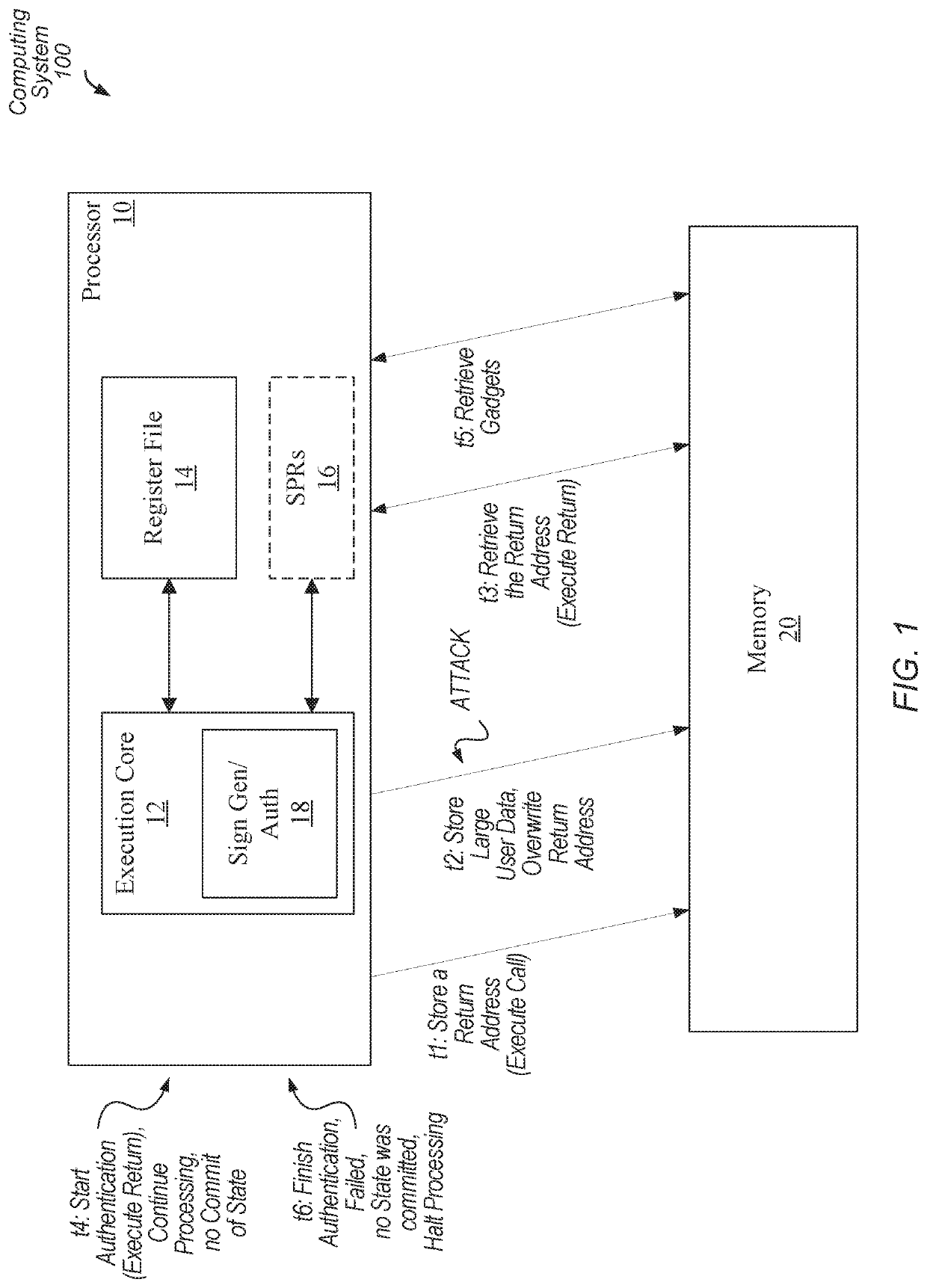

Systems and methods for optimizing authentication branch instructions

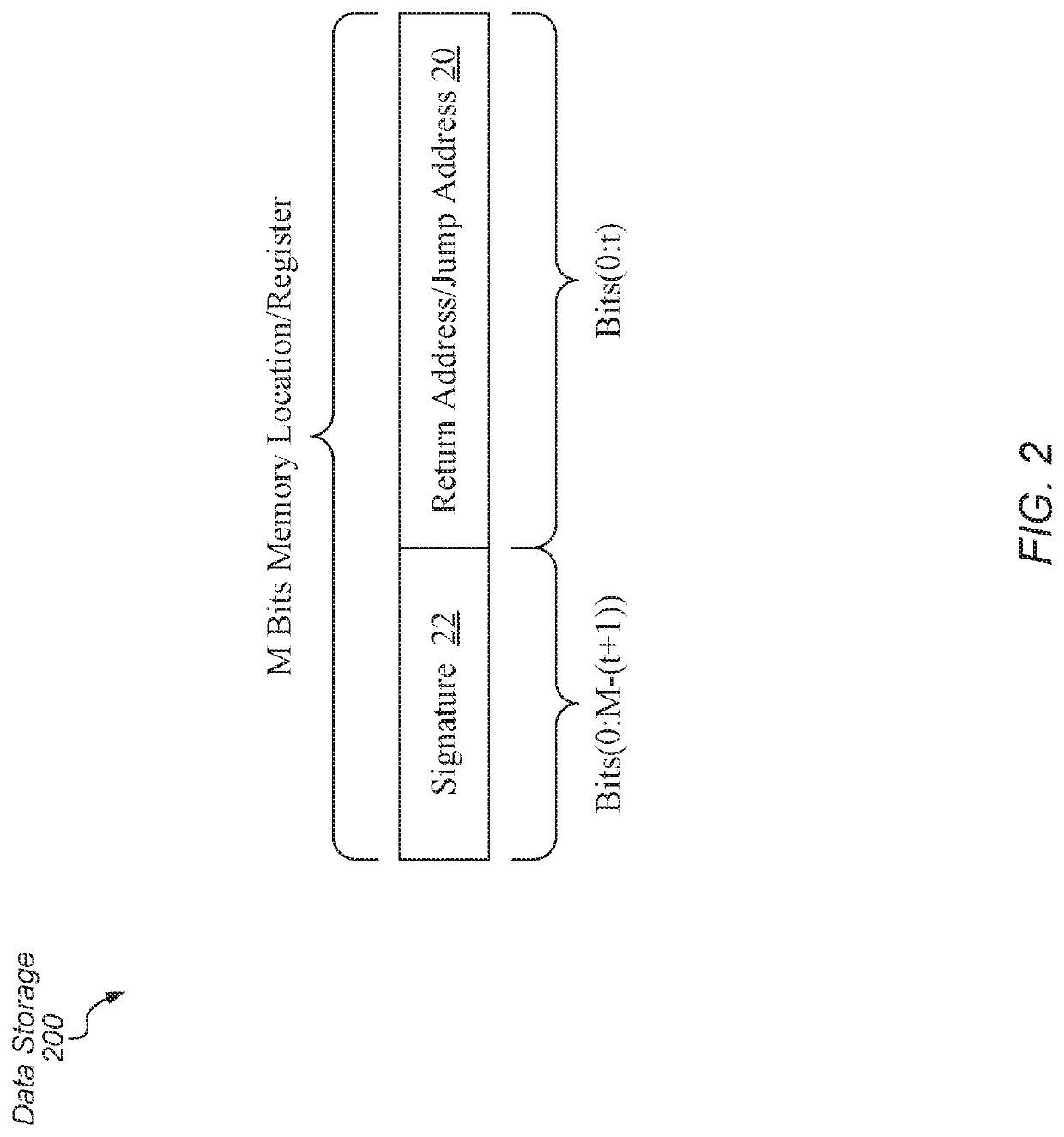

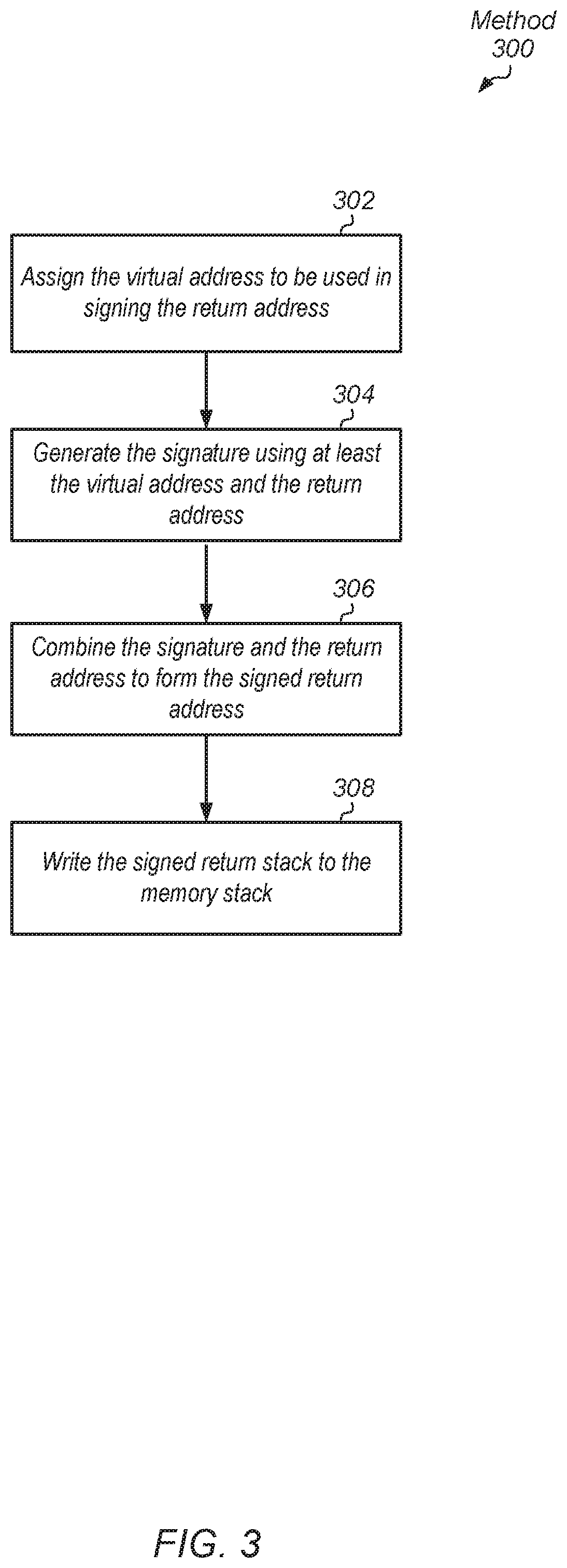

ActiveUS11468168B1Memory architecture accessing/allocationDigital data protectionReturn address stackProcedure calls

Systems, apparatuses, and methods for efficient handling of subroutine epilogues. When an indirect control transfer instruction corresponding to a procedure return for a subroutine is identified, the return address and a signature are retrieved from one or more of a return address stack and the memory stack. An authenticator generates a signature based on at least a portion of the retrieved return address. While the signature is being generated, instruction processing speculatively continues. No instructions are permitted to commit yet. The generated signature is later compared to a copy of the signature generated earlier during the corresponding procedure call. A mismatch causes an exception.

Owner:APPLE INC