Gearbox circuit for reducing data bit width under condition of not changing Baud rate of data transmission and working method

A gearbox circuit and data bit width technology, applied in the direction of digital transmission systems, transmission systems, electrical components, etc., can solve problems affecting the accuracy of data transmission, output data repetition, etc., to reduce additional overhead, reduce data bit width, The effect of improving reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

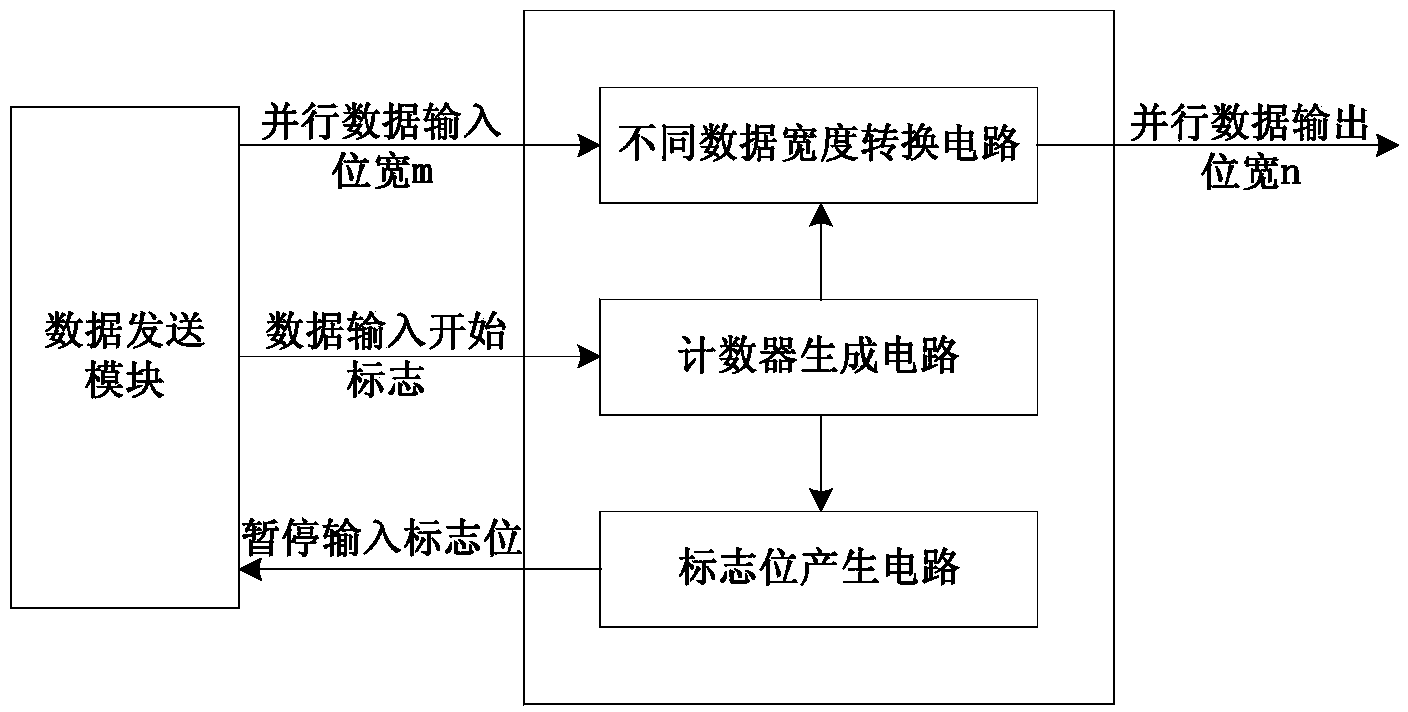

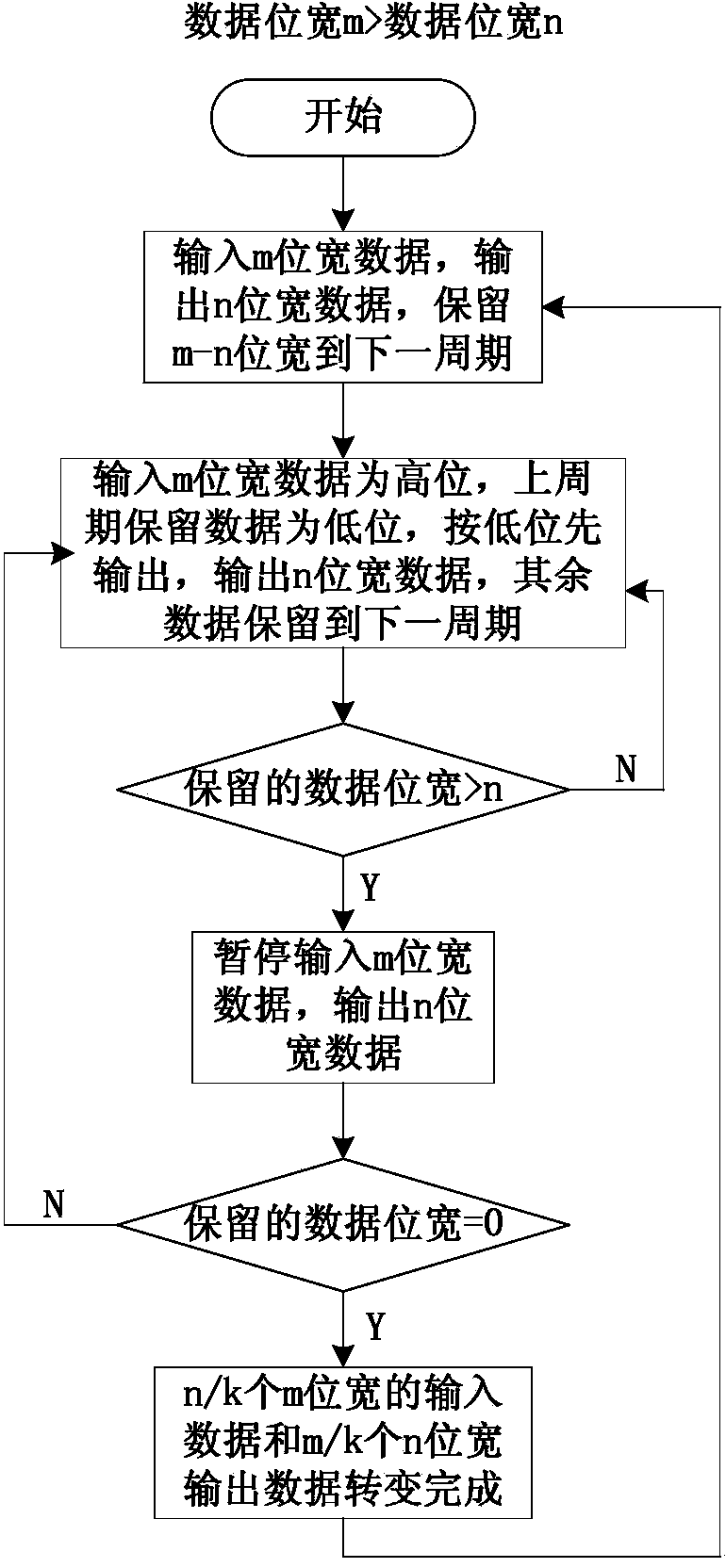

[0032] The invention provides a new gearbox design method and circuit, which can perform conversion of different data bit widths under the same bit rate. The circuit structure of the gearbox is as follows figure 1 As shown, it includes three parts: a data bit width conversion circuit, a counter generation circuit and a flag bit generation circuit, and the output of the counter generation circuit is respectively connected to the data bit width conversion circuit and the flag bit generation circuit.

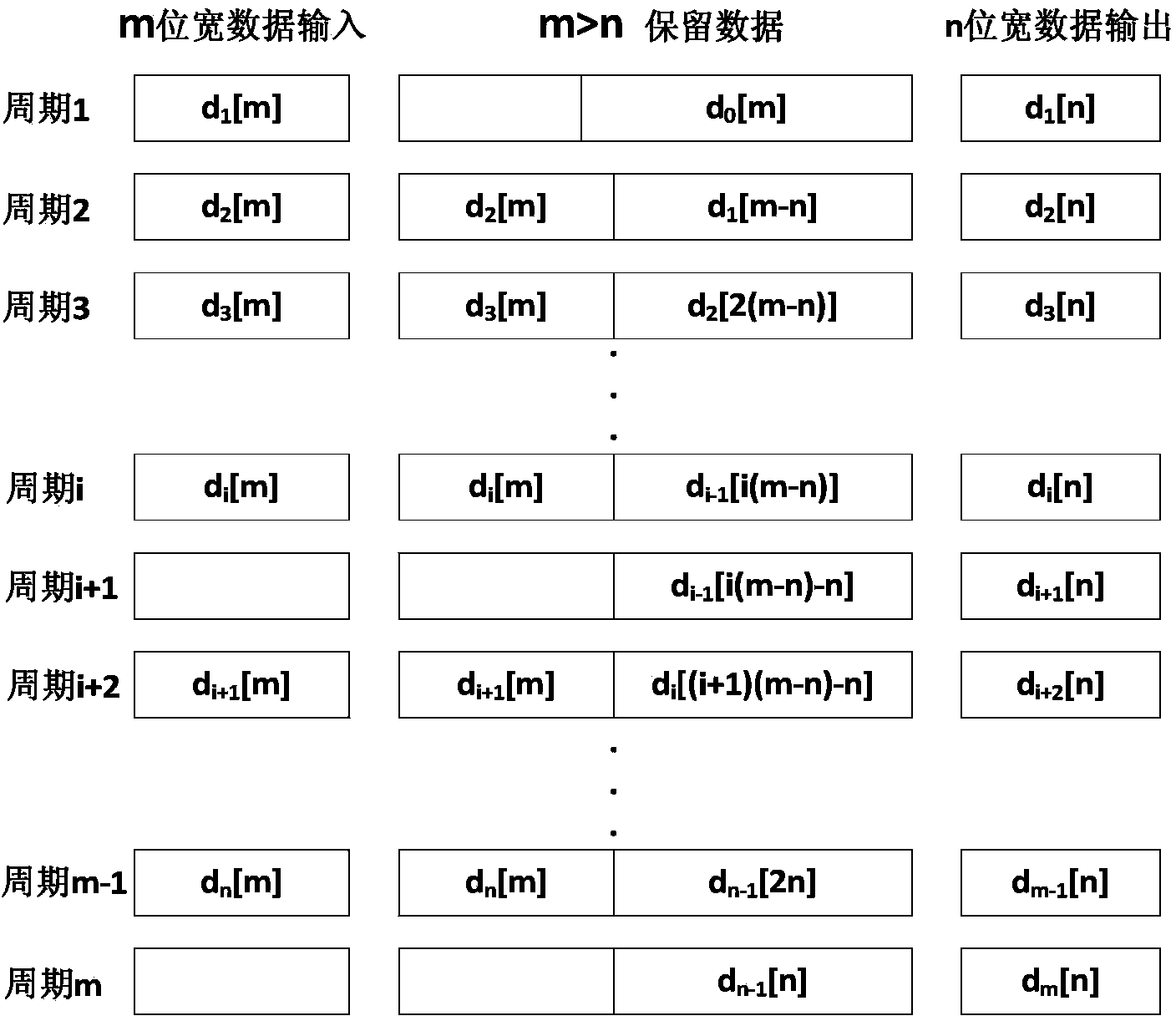

[0033] The clock frequency used for the input data of the gearbox is a, the bit width of the data is m bits, the clock frequency used for the output data of the gearbox is also a, and the data bit width is n bits. In the present invention, it is stipulated that m>n; the input bit width m, the least common divisor of the output bit width n and m-n is k, and the values obtained after dividing by k are respectively m / k, n / k and (m-n) / k .

[0034] The gearbox works as follows:

[0...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com