Manufacturing method of burn-in semiconductor test board

A burn-in and manufacturing method technology, applied in the direction of semiconductor/solid-state device testing/measurement, etc., can solve problems such as difficulty in ensuring alignment requirements, scratched board surface, and substandard board thickness in the gold finger area, so as to improve good quality, Design optimization and the effect of solving the problem of substandard plate thickness

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0025] It should be noted that, in the case of no conflict, the embodiments in the present application and the technical features in the embodiments can be combined with each other. The present invention will be further described in detail below in conjunction with the drawings and specific embodiments.

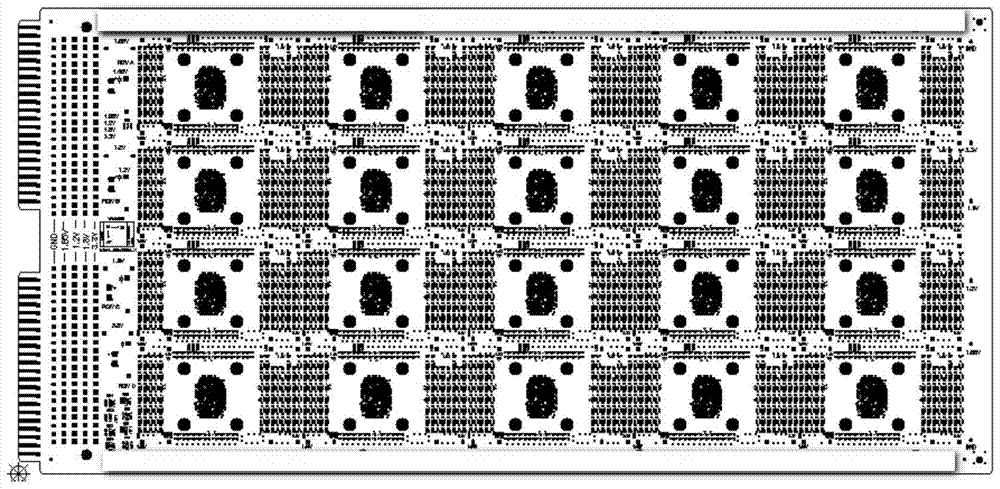

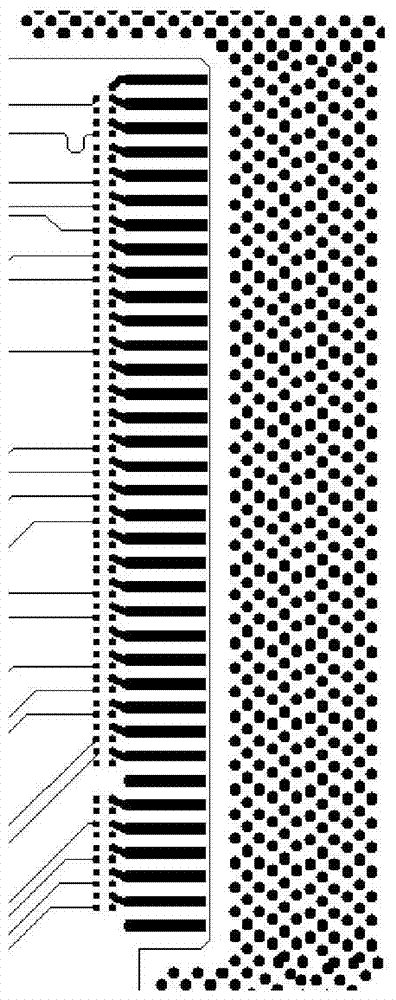

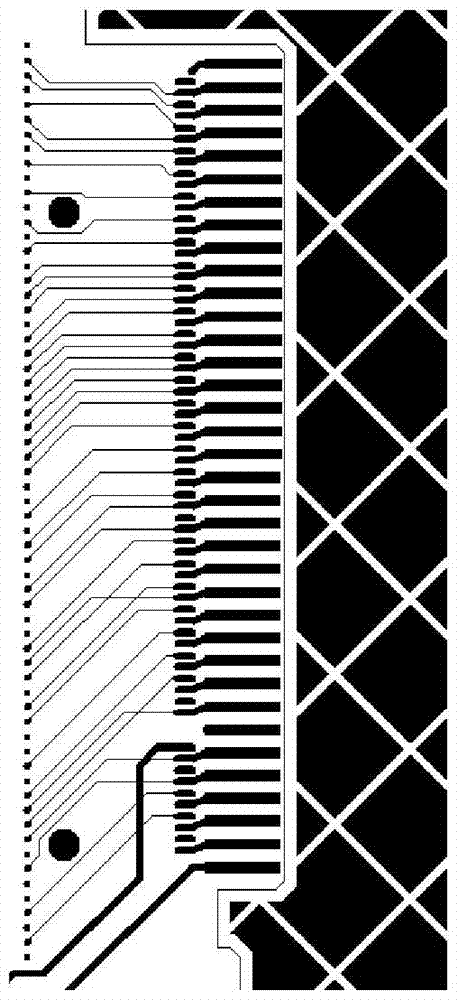

[0026] The present invention is a kind of manufacture method of Burn-in semiconductor test board, refer to Figure 5 to Figure 7 , including the protection step of the BGA area on the test board during the transmission process, the stacking step of the golden finger area on the test board and the manufacturing step of the process edge, and the steps of individually positioning each BGA to measure expansion and contraction and drilling.

[0027] The Burn-in semiconductor test board has an ultra-long board size. The protection steps of the BGA area on the test board include: after the surface treatment of the board body, select a transparent micro-mucosa with the same size as th...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com