Multi-interface mode realization method of 1553B bus protocol IP (Internet Protocol) core

A technology of bus protocol and implementation method, which is applied in the direction of instruments, electrical digital data processing, etc., can solve the problems of poor scalability and single interface form, and achieve the effect of improving scalability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

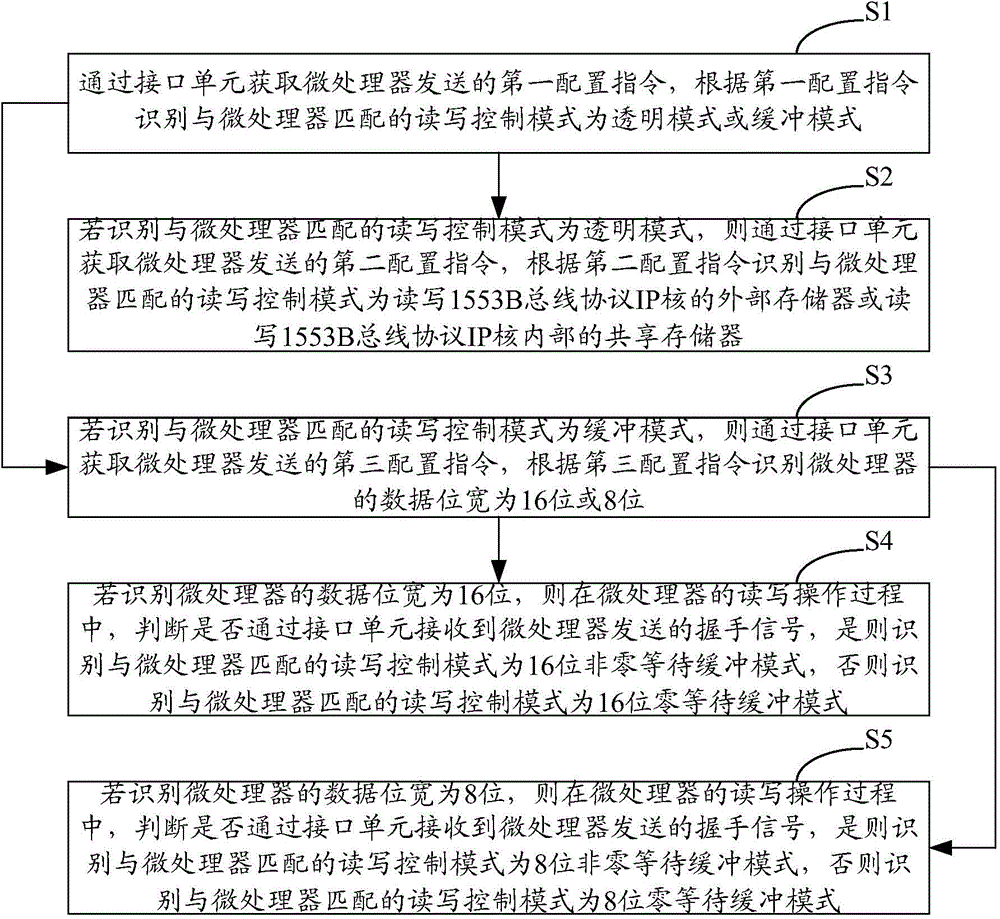

[0031] Embodiment 1 of the present invention proposes a method for implementing a multi-interface mode of a 1553B bus protocol IP core, such as figure 2 shown, including:

[0032] Step S1: Obtain the first configuration instruction sent by the microprocessor through the interface unit, and identify the read / write control mode matching the microprocessor as transparent mode or buffer mode according to the first configuration instruction.

[0033] In Embodiment 1 of the present invention, the identification of the transparent mode or the buffer mode can be realized according to whether the first configuration command is at a high level or a low level. For example, if the first configuration command trans_buf is high level, that is, trans_buf=1, the read-write control mode can be recognized as transparent mode; if the first configuration command trans_buf is low level, that is, trans_buf=0, the read-write control mode can be recognized for buffer mode.

[0034] Step S2: If it ...

Embodiment 2

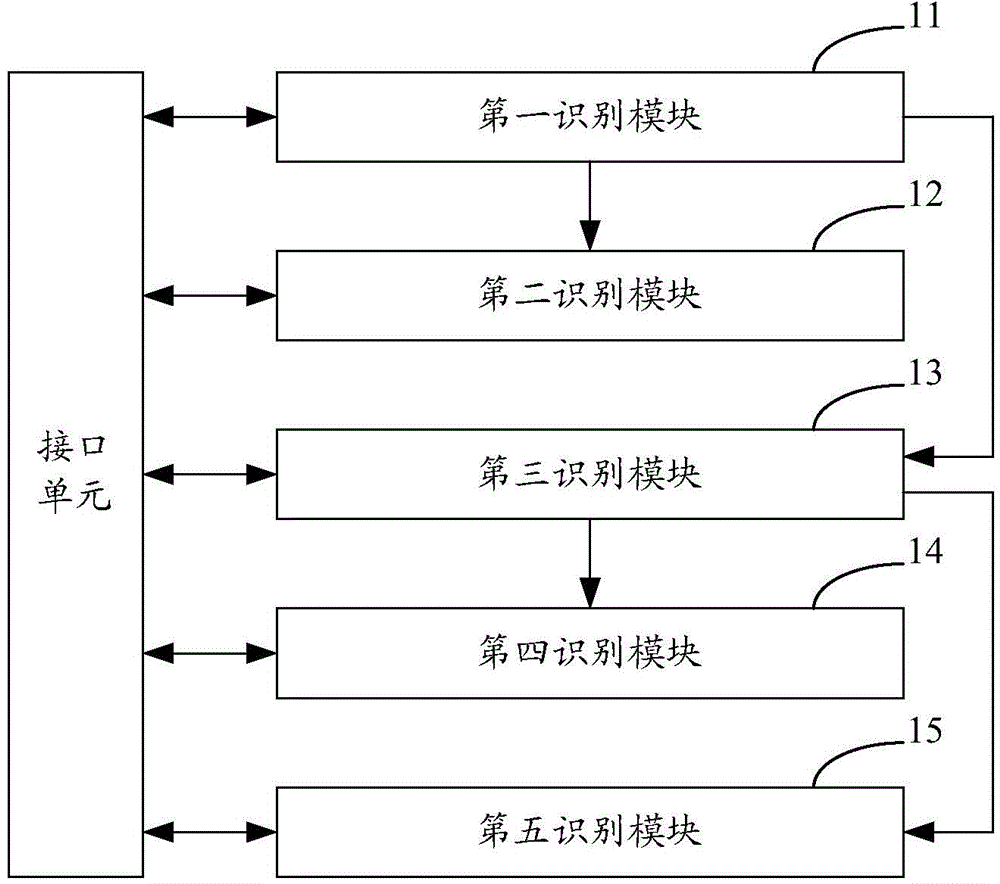

[0045] Embodiment 2 of the present invention proposes a multi-interface management system, such as image 3 As shown, for ease of description, only the part related to Embodiment 2 of the present invention is shown.

[0046] In detail, the multi-interface management system provided by Embodiment 2 of the present invention includes: a first identification module 11, configured to obtain the first configuration instruction sent by the microprocessor through the interface unit, and identify the interface that matches the microprocessor according to the first configuration instruction. The read-write control mode is a transparent mode or a buffer mode; the second identification module 12 is used to obtain the information sent by the microprocessor through the interface unit when the first identification module 11 identifies that the read-write control mode matched with the microprocessor is a transparent mode. According to the second configuration instruction, the read-write contr...

Embodiment 3

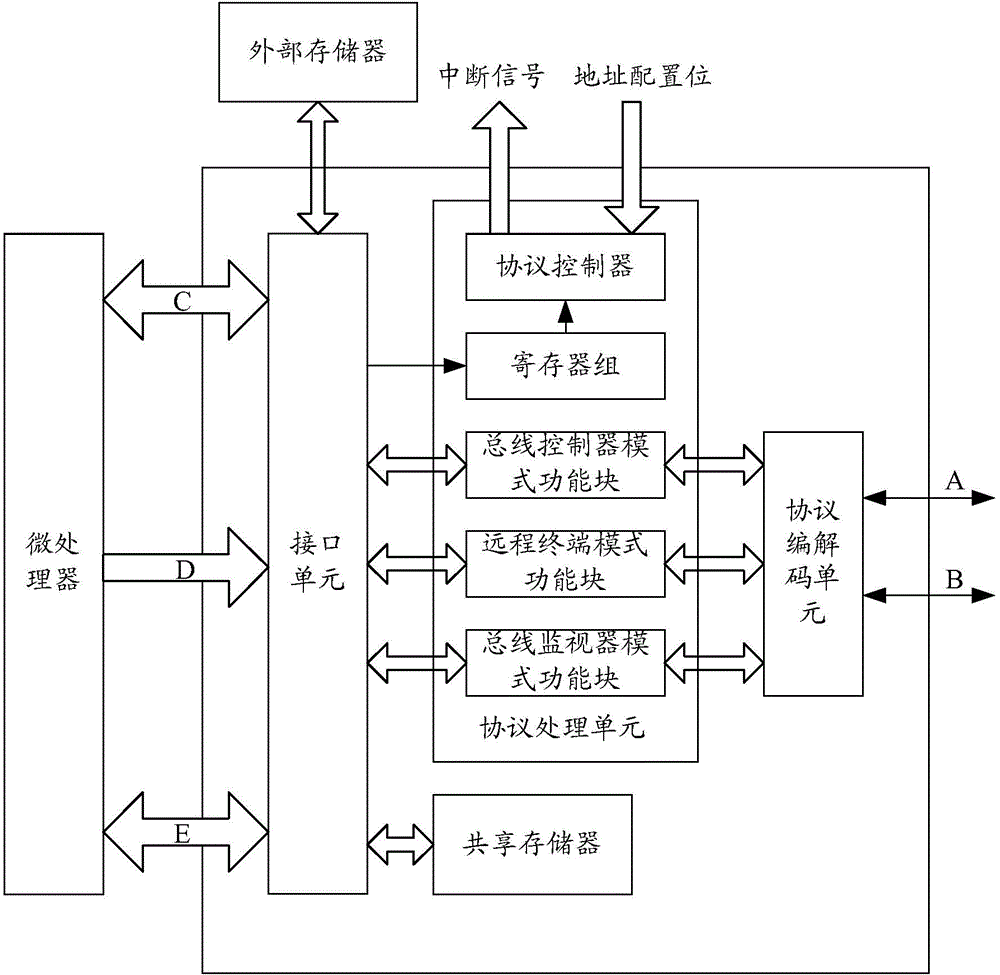

[0051] The third embodiment of the present invention proposes a 1553B bus protocol IP core, such as Figure 4 As shown, for ease of description, only the part related to Embodiment 3 of the present invention is shown.

[0052] In detail, the 1553B bus protocol IP core includes: an interface unit 22, the interface unit 22 is connected to the microprocessor through the data line C, the address line D, and the control line E, and can also be connected to an external memory according to actual needs; A shared memory 23 of 22; a protocol processing unit 24 connecting the interface unit 22 and the microprocessor; a protocol codec unit 25 connecting the protocol processing unit 24. Wherein, the internal structure and function of the protocol processing unit 24 are as follows: figure 1 shown, and will not be described here.

[0053] Different from the existing 1553B bus protocol IP core, the 1553B bus protocol IP core also includes a multi-interface management system 21 connected to...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com