A kind of thin film transistor and its preparation method, array substrate, display device

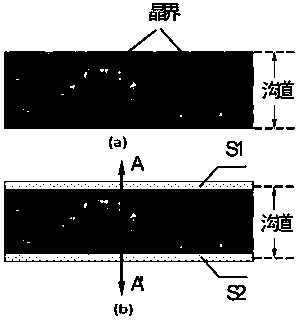

A technology of thin film transistors and substrate substrates, which is applied in the direction of transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., and can solve the problems of reducing the stability of TFT electrical properties, large roughness at grain boundaries, and increased leakage current.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

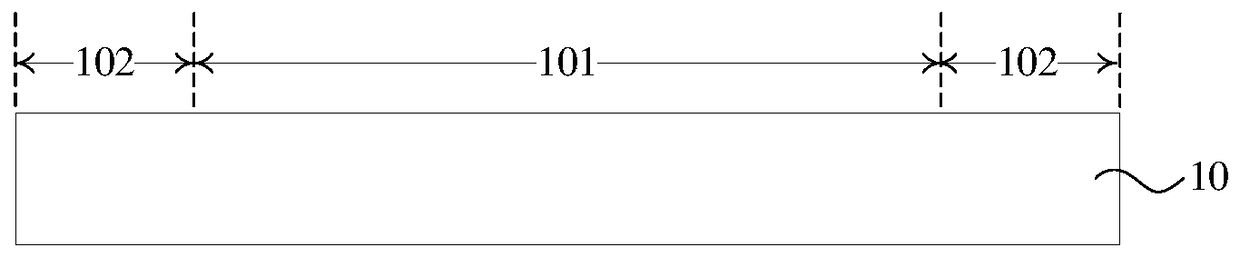

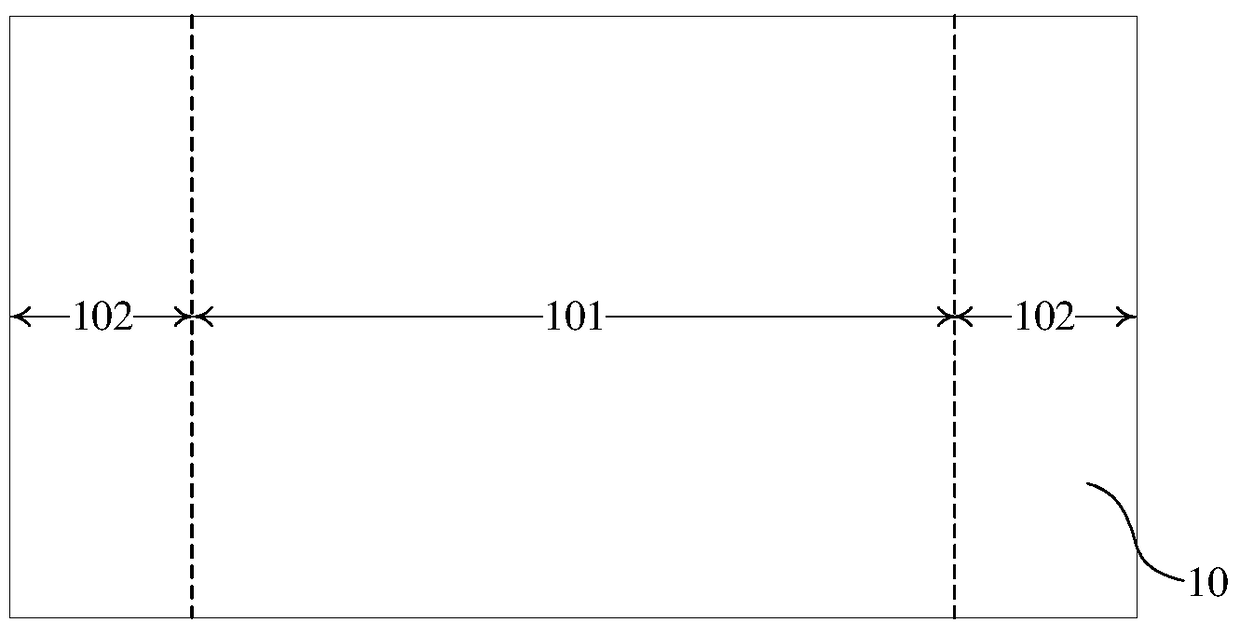

[0044] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

[0045] It should be noted that, unless otherwise defined, all terms (including technical and scientific terms) used in the embodiments of the present invention have the same meaning as commonly understood by those of ordinary skill in the art to which the present invention belongs. It should also be understood that terms such as those defined in common dictionaries should be interpreted as having meanings consistent with their meanings in the context of the rel...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More