Test method of parallel quadrilateral LED chip

A LED chip and parallelogram technology, which is applied in the testing field of parallelogram LED chips, can solve the problems of inability to have one-to-one correspondence of photoelectric characteristics test data, cumbersome testing process of parallelogram LED chips, etc., so as to avoid failure to correspond one by one and solve production difficulties , The effect of simplifying the production process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

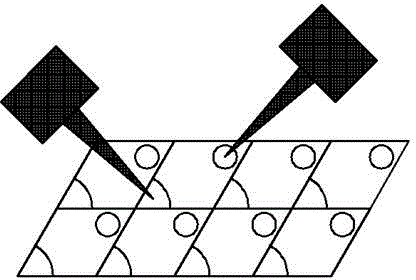

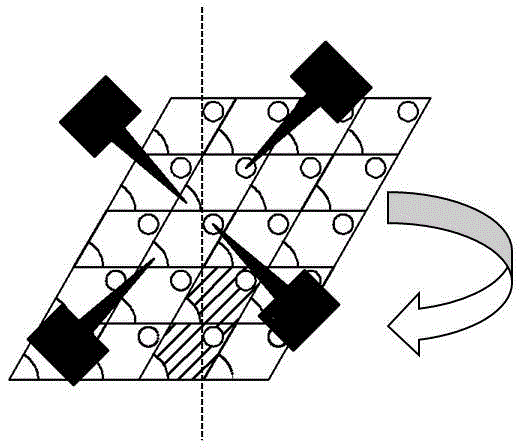

[0021] like figure 2 As shown, this embodiment provides a 4-pin point measurement method for a parallelogram LED chip, that is, a testing machine with 2 sets of probe modules is used to test the photoelectric characteristics of 2 chip units to be tested, and the probe modules simultaneously test 2 For adjacent chip units in the same row, the inner angles of the chip units are 60° and 120°. The test sequence and direction of the chip are shown by the arrows, first from left to right, then from top to bottom. When the next two rows of core particles (shaded slashes) are tested, a rectangular coordinate system is just formed, that is, the current spot measurement The two core particles and the two core particles of the lower oblique line are orthogonally translated, and the abscissas of the center points of the upper and lower adjacent chip units to be tested are consistent. At this time, the photoelectric characteristic parameters of the chip and the coordinate position of the...

Embodiment 2

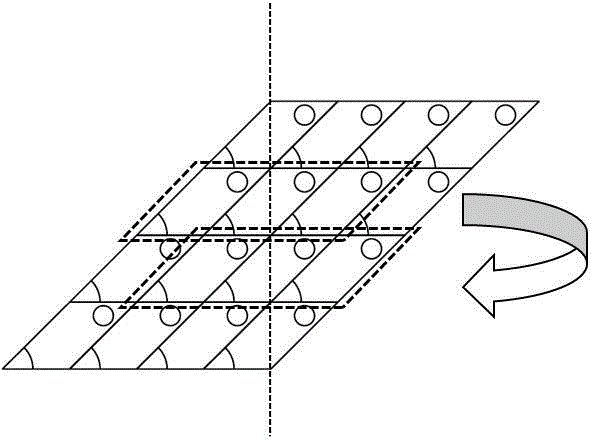

[0023] like image 3 As shown, this embodiment provides a 6-pin spot test method for a parallelogram LED chip, that is, a testing machine with 3 sets of probe modules is used to test the photoelectric characteristics of 3 chip units to be tested, and the probe modules simultaneously test 3 Adjacent chip units in the same line (the position where the probe module contacts the electrodes, not shown in the figure), the inner angles of the chip units are 45° and 135°. The test sequence and direction of the chip are shown by the arrows, first from left to right along the X axis, and then from top to bottom along the Y axis. The core grain and the two core grains with the oblique line below are orthogonally translated, and the abscissas of the center points of the upper and lower adjacent chip units to be tested (located in the dotted line box) are consistent. At this time, the photoelectric characteristic parameters of the chip and the coordinate position of the center point of th...

Embodiment 3

[0025] like Figure 4 As shown, different from Embodiment 2, this embodiment provides an 8-pin point measurement method for a parallelogram LED chip, that is, a testing machine with 4 sets of probe modules is used to test the photoelectric characteristics of 4 chip units to be tested. Its probe module tests 4 adjacent chip units (located in the dotted line box) at the same time, and the chip units to be tested are combined in 2×2 rows and columns, and the test time is shortened to 1 / 4.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More