Grid electrode protection circuit for field effect transistors connected in series

A field effect tube and protection circuit technology, which is applied in the field of field effect tube series gate protection circuit, can solve the problems of gate voltage overrun, field effect tube breakdown, etc., and achieve the effect of improving the high voltage resistance range

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

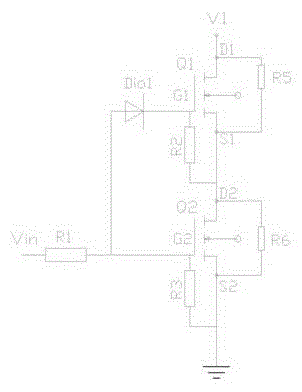

[0011] like figure 1 As shown, a field effect transistor series gate protection circuit, the field effect transistor control voltage Vin is connected in series with the gate G1 of the field effect transistor Q1 through the diode Dio1.

[0012] When the FET control voltage Vin is at a high level greater than the Vth of the FET, the FET Q1 and the FET Q2 are turned on, and the voltage V1 between the drain D1 of the FET Q1 and the S2 source of Q2 is close to at zero.

[0013] When the FET control voltage Vin is zero, the FET Q1 and the FET Q2 are turned off, and the voltage between the drain D1 of the FET Q1 and the S2 source of the FET Q2 is V1. R5 and R6 are equalizing resistors, VR5=VR6, VR5+VR6= V1. When V1 is high, if the diode Dio1 is not connected, VS1G1 may exceed the gate voltage limit of the field effect transistor Q1, and the field effect transistor Q1 will be broken down. After the diode Dio1 is connected, due to the blocking function of the diode, VS1G1 is zero, a...

Embodiment 2

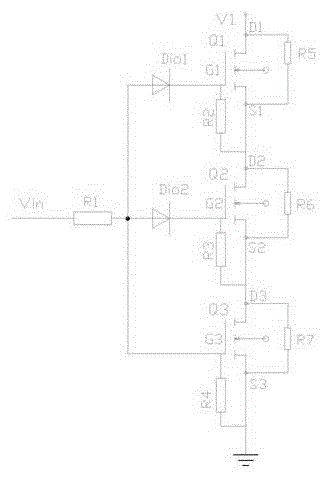

[0016] like figure 2 As shown, the field effect transistor control voltage Vin is connected in series to the gate G1 of the field effect transistor Q1 and the gate G2 of the field effect transistor Q2 through the diode Dio1 and the diode Dio2 respectively.

[0017] When the FET control voltage Vin is at a high level greater than the Vth of the FET, the FET Q1, the FET Q2, and the FET Q3 are turned on, and the connection between the drain D1 and the source S1 of the FET Q1 is The voltage, the voltage between the drain D2 and the source S2 of the field effect transistor Q2, and the voltage between the drain D3 and the source S3 of the field effect transistor Q3 are all close to zero.

[0018] When the FET control voltage Vin is zero, the FET Q1, FET Q2, and FET Q3 are turned off, and the voltage between the drain D1 of the FET Q1 and the S3 source of the FET Q3 is VD1S3= V1. R5, R6, R7 are voltage equalizing resistors, VR5=VR6= VR7, VR5+VR6+ VR7= V1, when V1 is high, if diode...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More