Patents

Literature

1752 results about "Voltage limit" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Voltage limit 1 simply means you have hit the max power draw for the card settings.

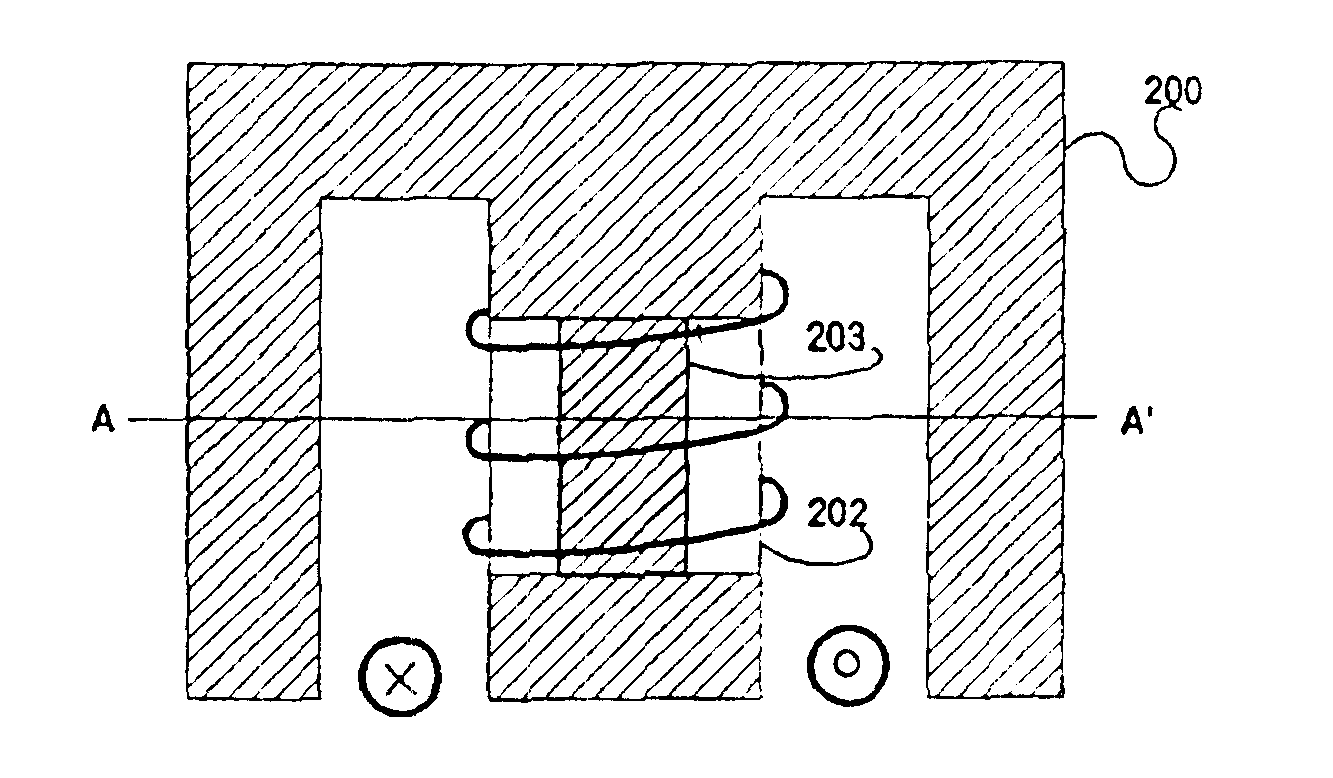

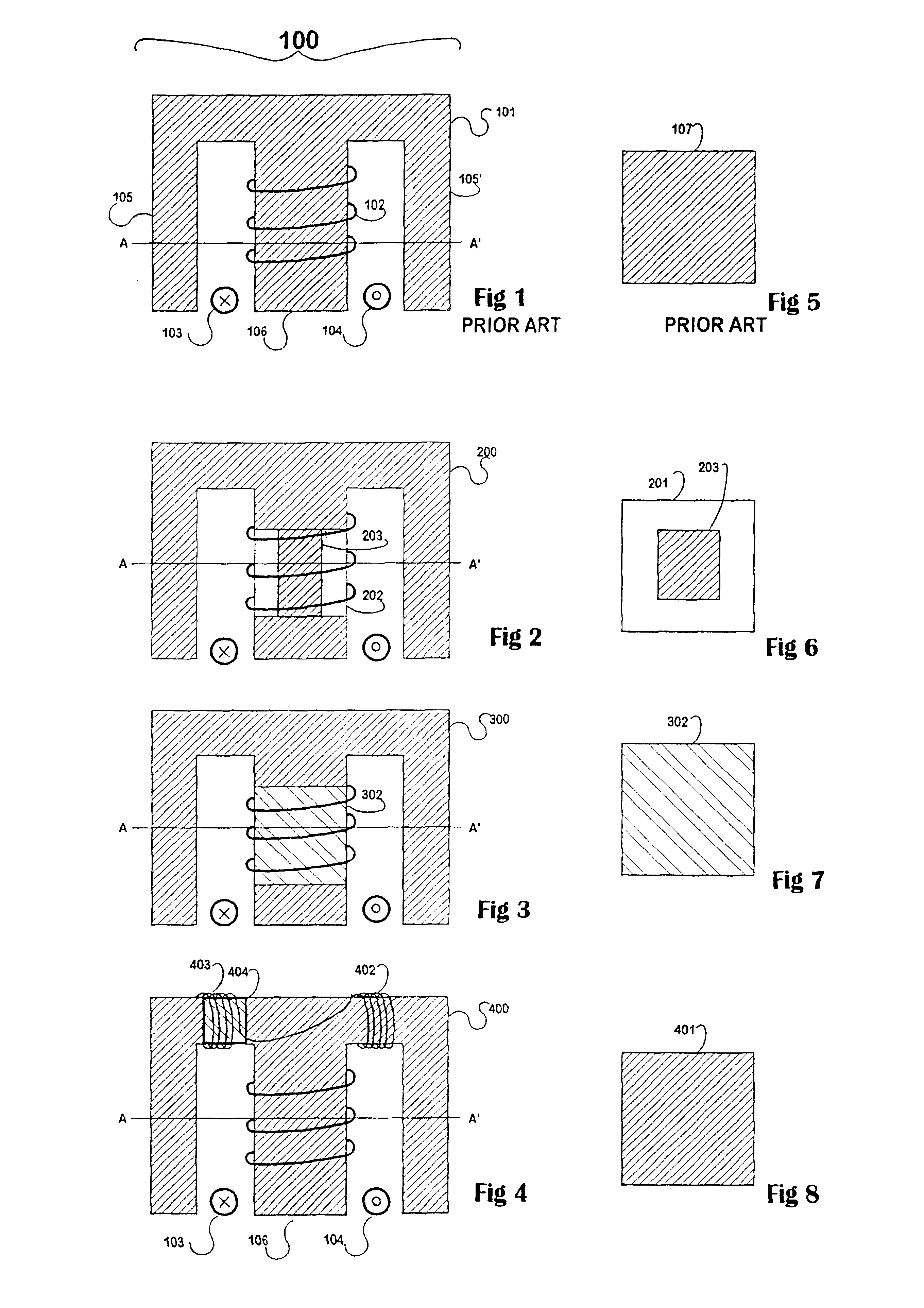

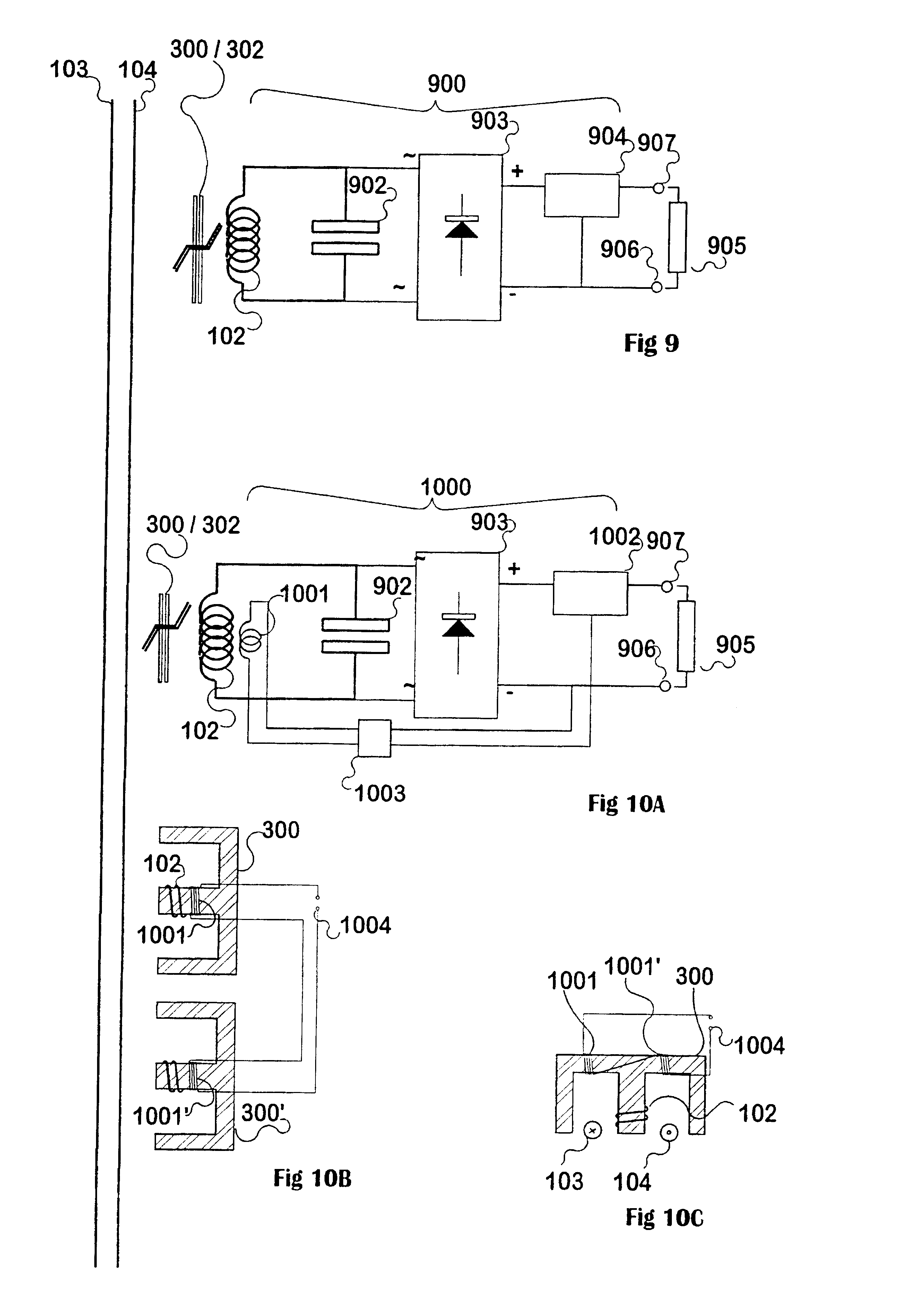

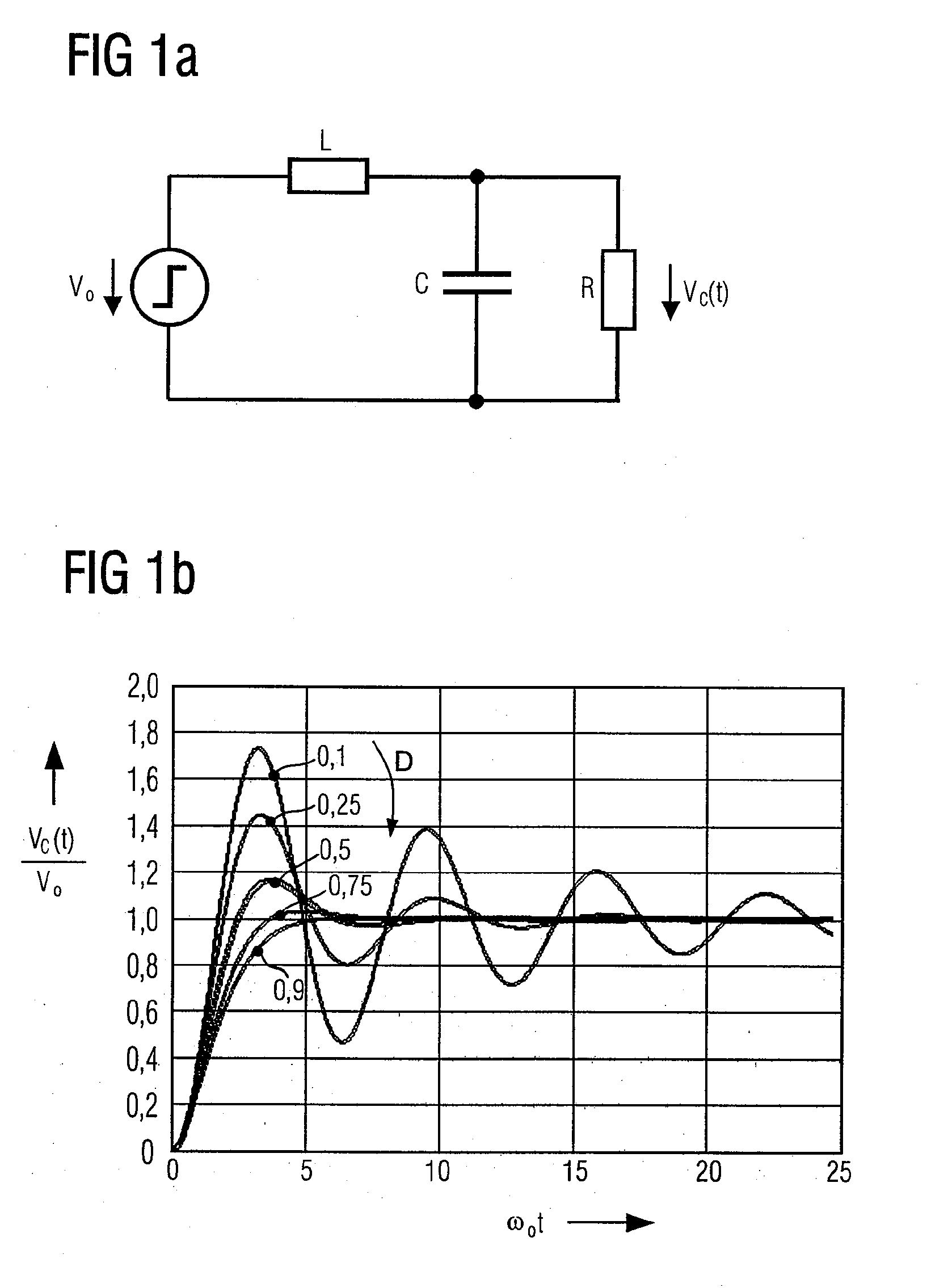

Control of inductive power transfer pickups

InactiveUS6483202B1Reliable fail-safe control featureDecrease in saturation capacityRail devicesElectromagnetic wave systemDc currentEngineering

Secondary resonant pickup coils (102) used in loosely coupled inductive power transfer systems, with resonating capacitors (902) have high Q and could support large circulating currents which may destroy components. A current limit or "safety valve" uses an inductor designed to enter saturation at predetermined resonating currents somewhat above normal working levels. Saturation is immediate and passive. The constant-current characteristic of a loosely coupled, controlled pickup means that if the saturable section is shared by coupling flux and by leakage flux, then on saturation the current source is terminated in the saturated inductor, and little detuning from resonance occurs. Alternatively an external saturable inductor (1101, 1102) may be introduced within the resonant circuit (102 and 902), to detune the circuit away from the system frequency. Alternatively DC current may be passed through a winding to increase saturation of a saturable part of a core. As a result, a fail-safe pickup offering a voltage-limited constant-current output is provided.

Owner:AUCKLAND UNISERVICES LTD

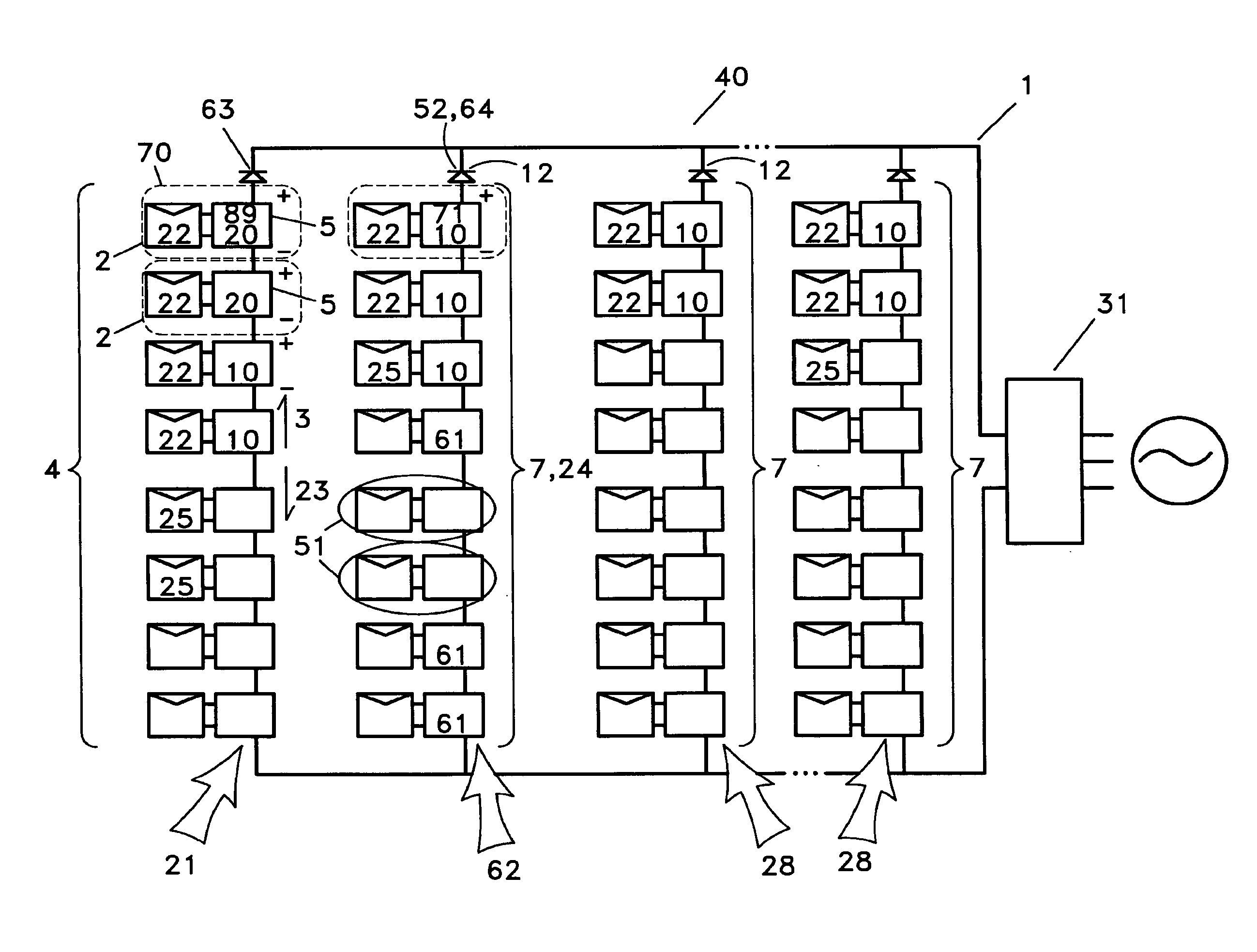

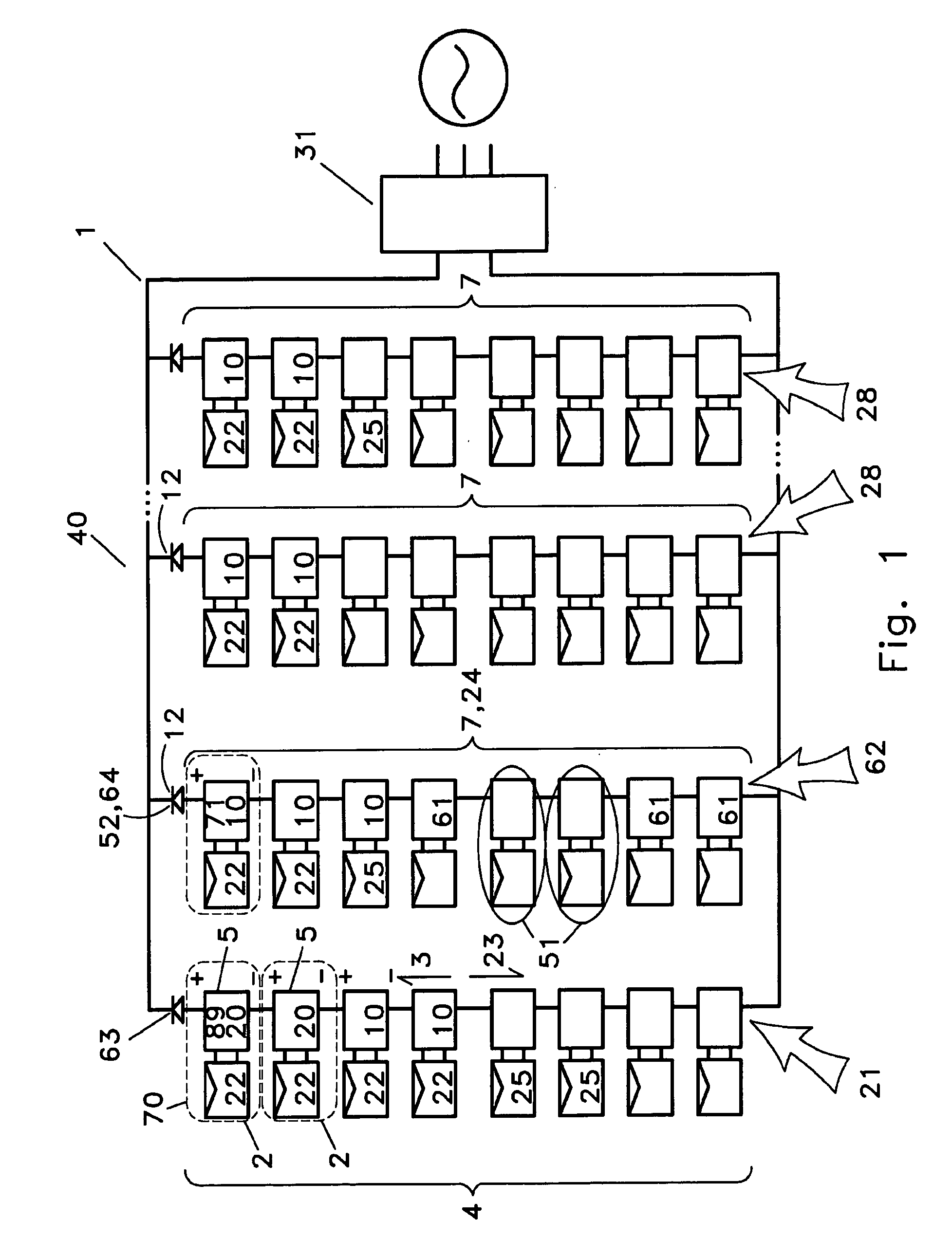

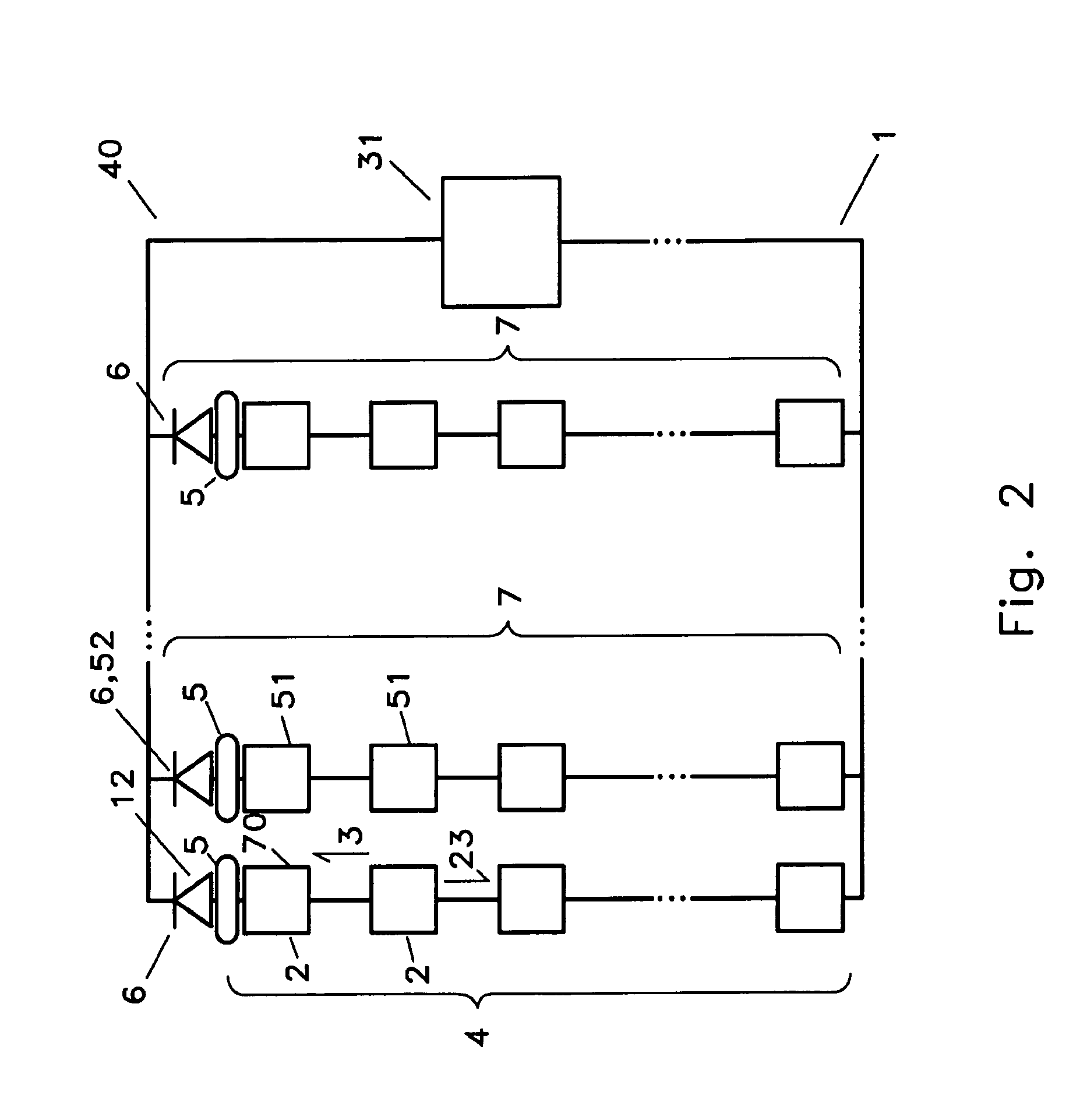

Novel Solar Power Circuits

InactiveUS20110210611A1Reducing eliminating riskAvoid flowDc source parallel operationPhotovoltaic energy generationPower flowReverse current

Particular embodiments of the inventive technology disclosed herein seek to reduce or eliminate the risk of damage to components of photovoltaic power circuits such as solar arrays. Aspects of the inventive technology, in embodiments, utilize diode to prevent reverse current flow in the event of application of a voltage to a power supply string which would otherwise effect such flow. Prevention of such reverse current flow may preclude voltages that would otherwise damage reverse current sensitive devices such as switches that may form part of a voltage limiting DC to DC converter.

Owner:AMPT

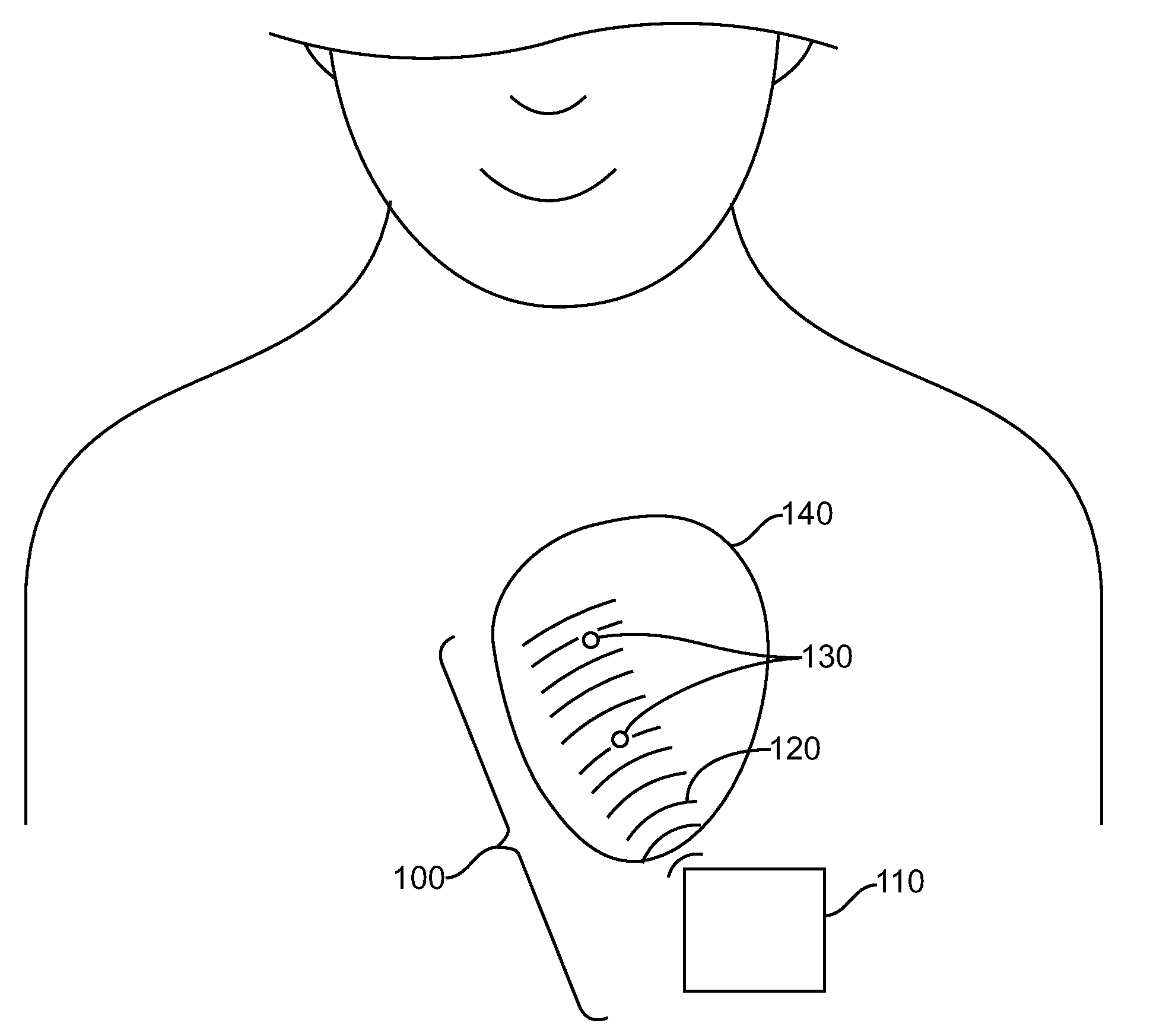

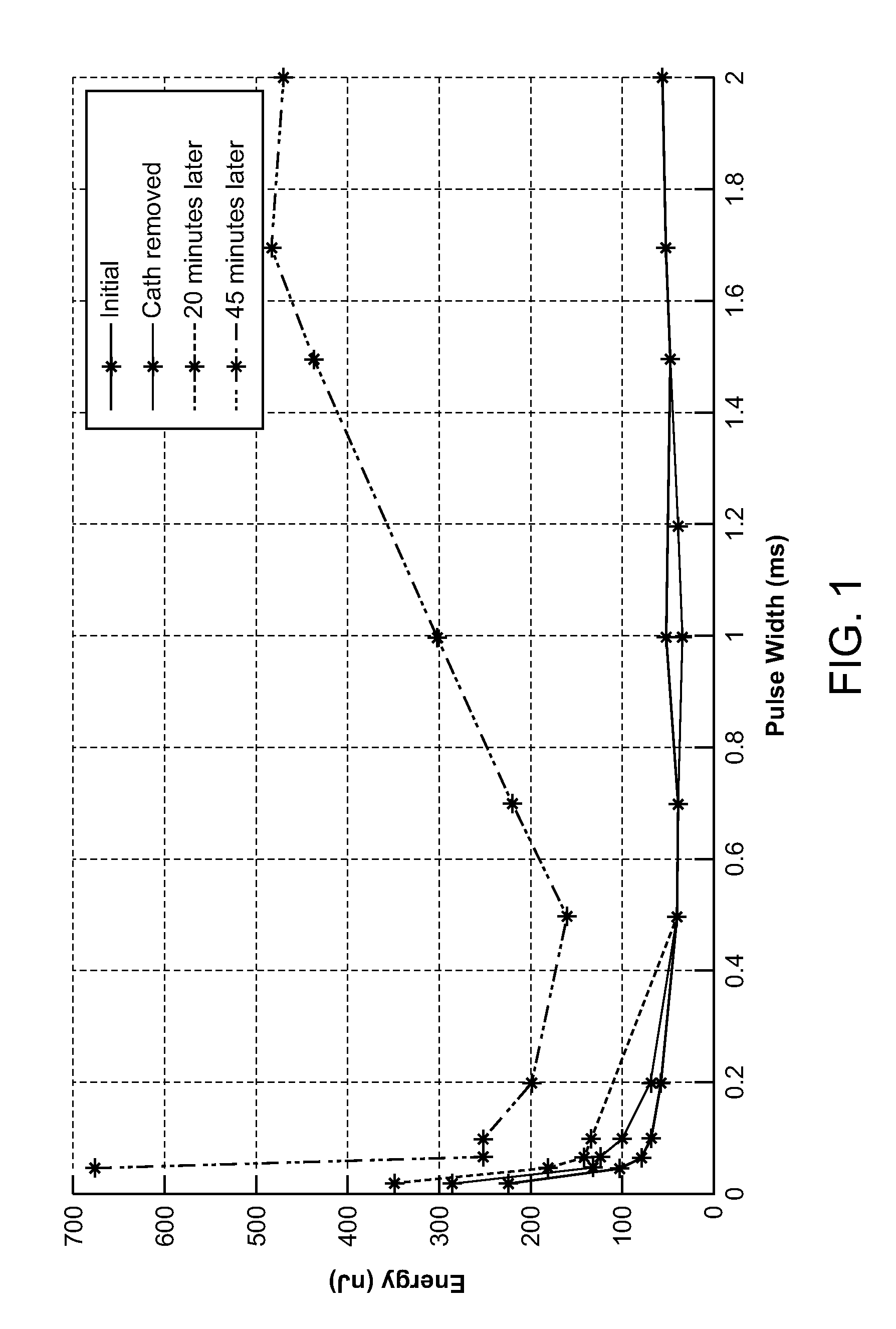

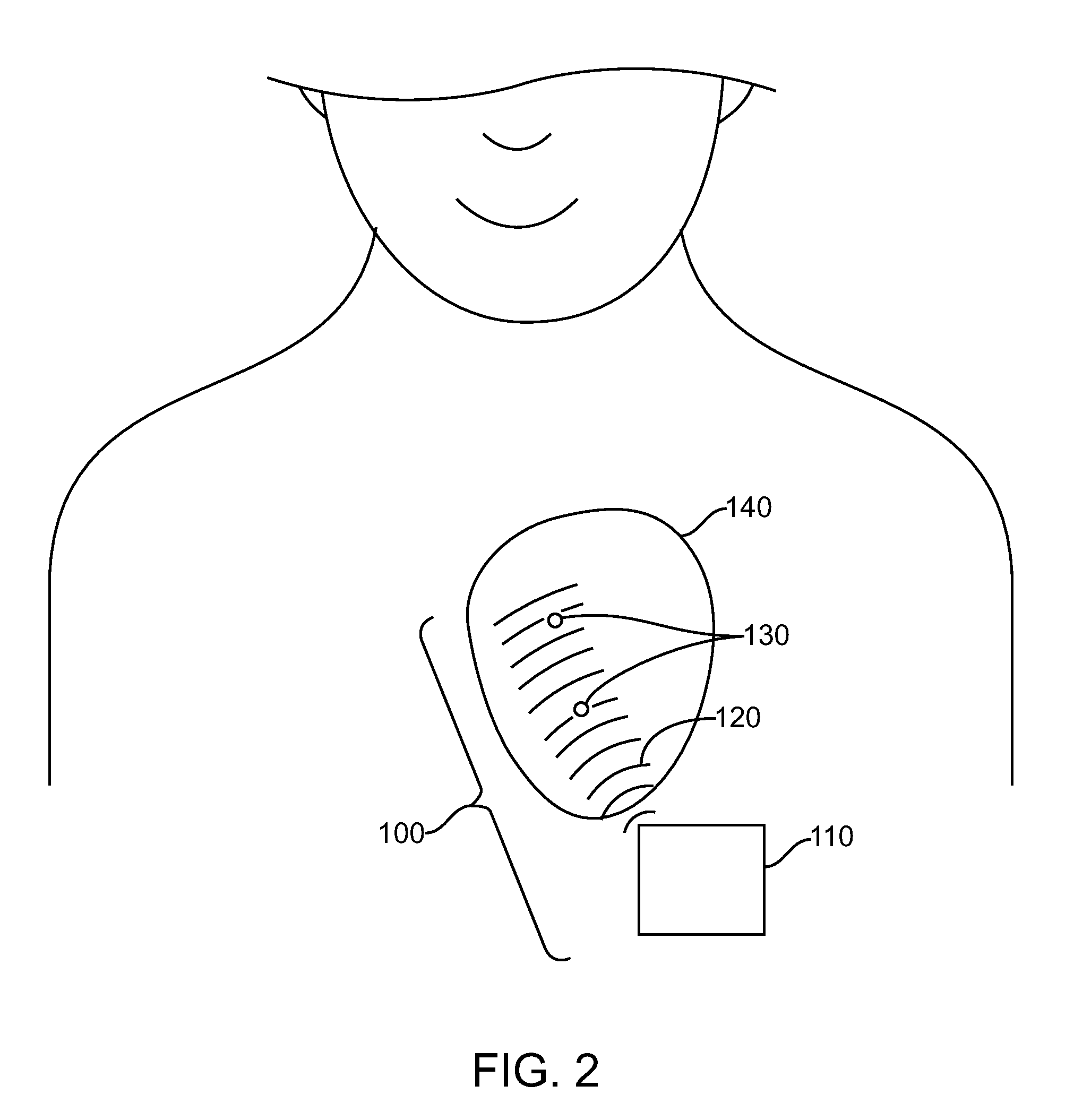

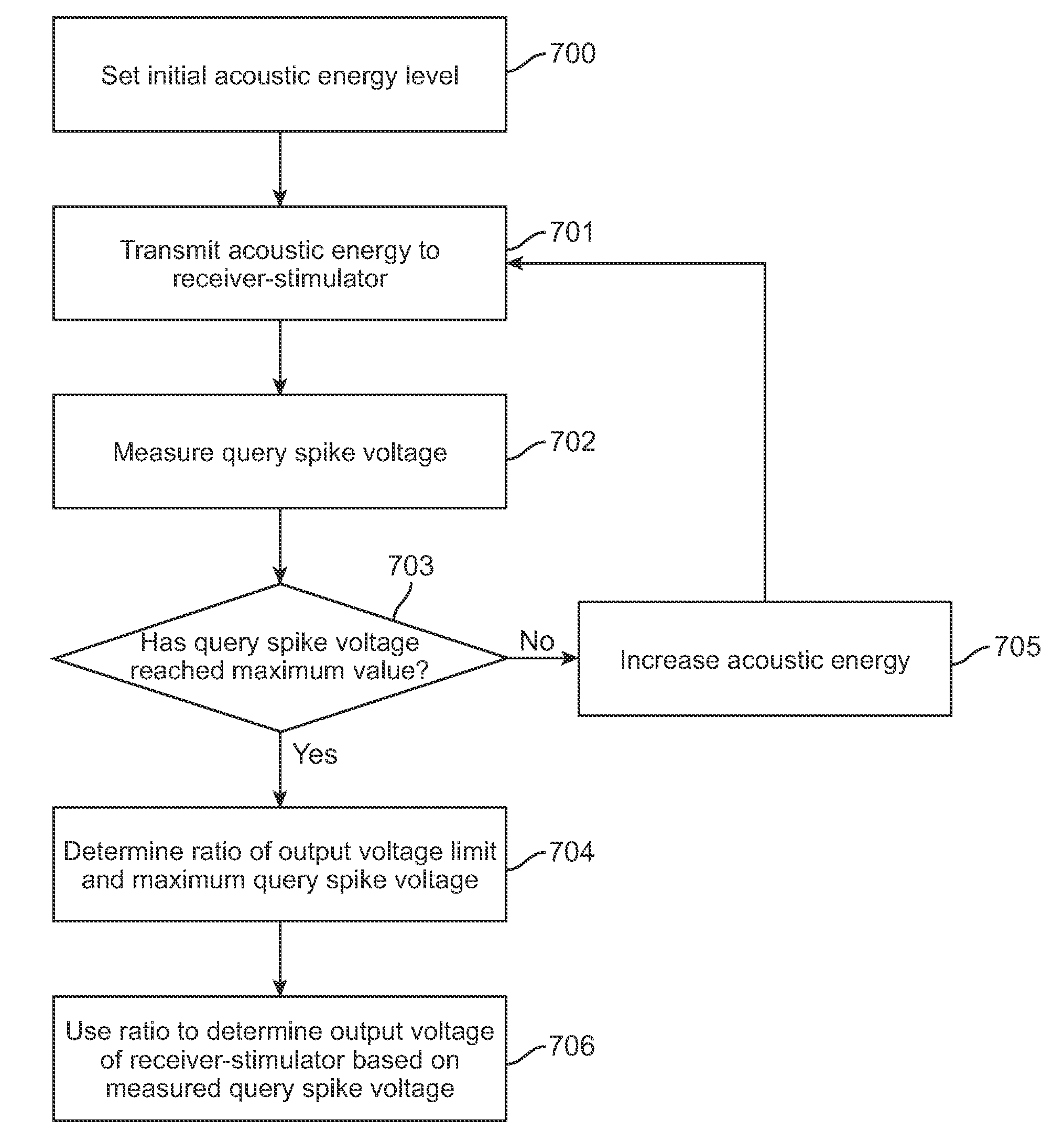

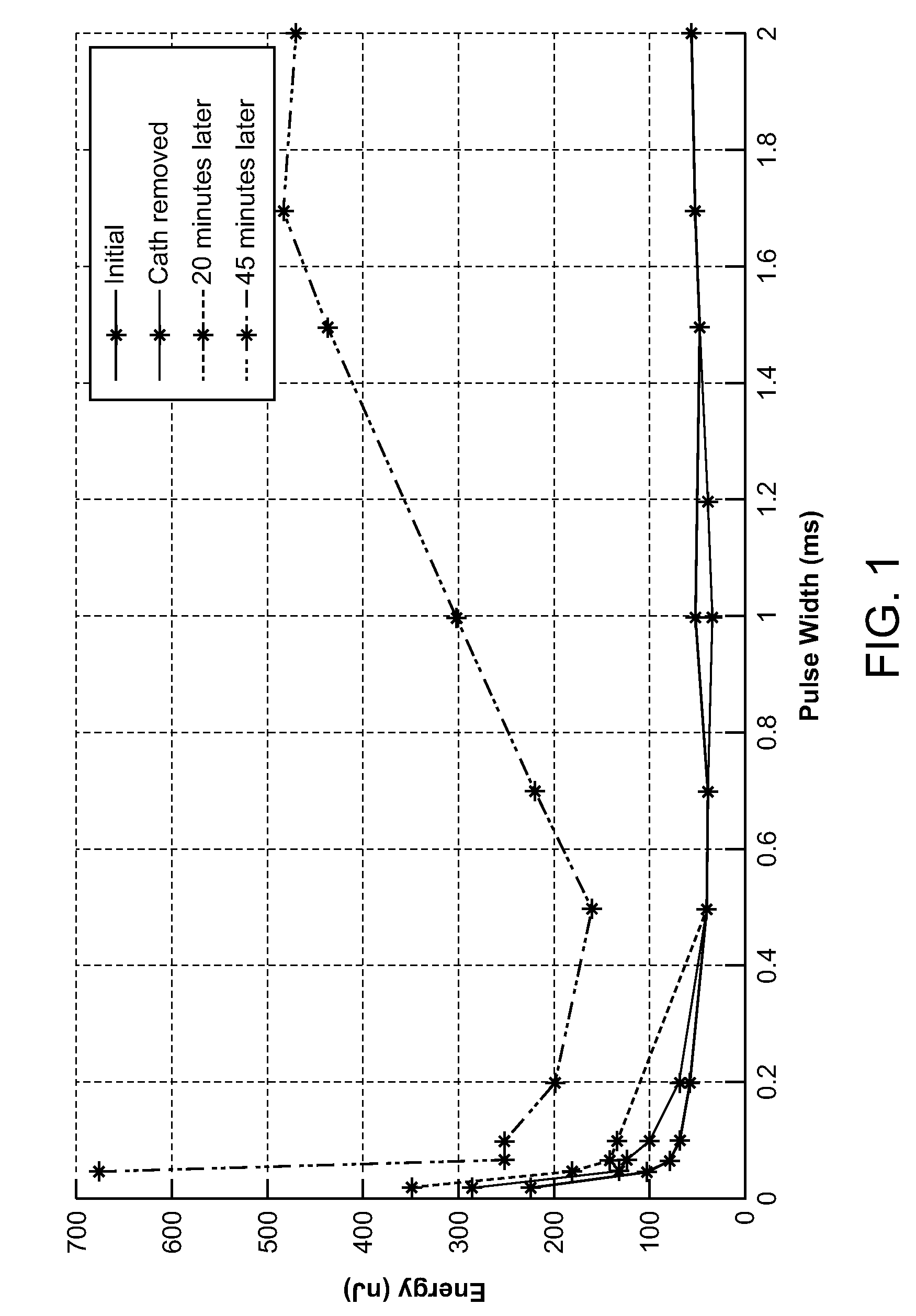

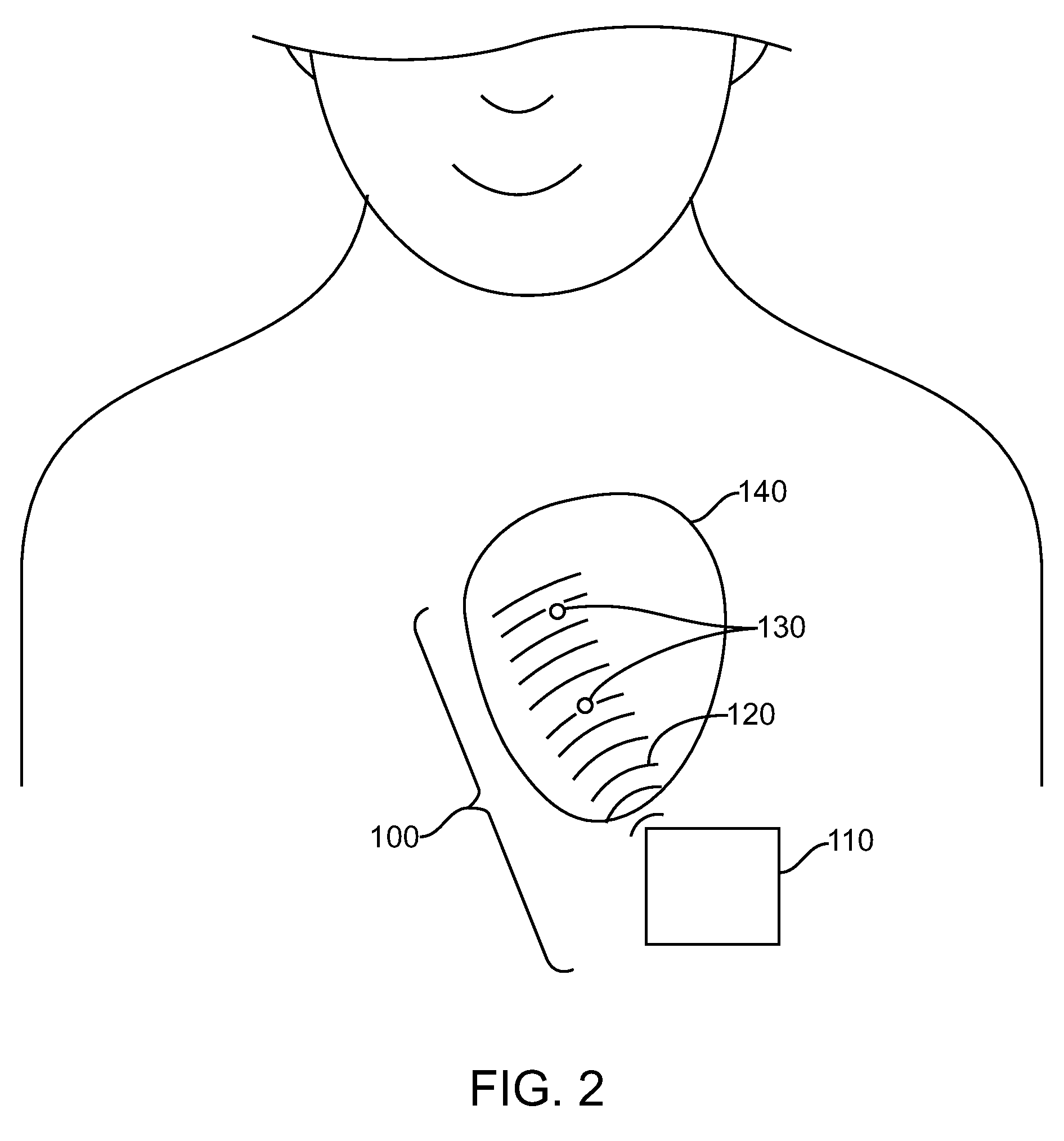

Operation and estimation of output voltage of wireless stimulators

A controller-transmitter transmits acoustic energy through the body to an implanted acoustic receiver-stimulator. The receiver-stimulator converts the acoustic energy into electrical energy and delivers the electrical energy to tissue using an electrode assembly. The receiver-stimulator limits the output voltage delivered to the tissue to a predetermined maximum output voltage. In the presence of interfering acoustic energy sources output voltages are thereby limited prior to being delivered to the tissue.Furthermore, the controller-transmitter estimates the output voltage that is delivered to the tissue by the implanted receiver-stimulator. The controller-transmitter measures a query spike voltage resulting from the electrical energy delivered to the tissue by the receiver-stimulator, and computes a ratio of the predetermined maximum output voltage and a maximum query spike voltage. The maximum query spike voltage is computed by detecting a query spike voltage plateau. Based on this ratio, the controller-transmitter uses a measured query spike voltage to estimate the output voltage delivered by the receiver-stimulator to tissue.

Owner:EBR SYST

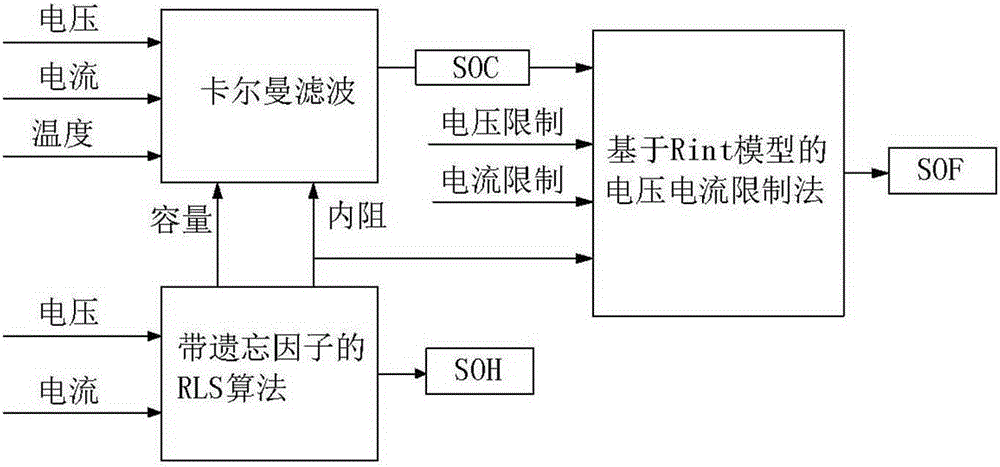

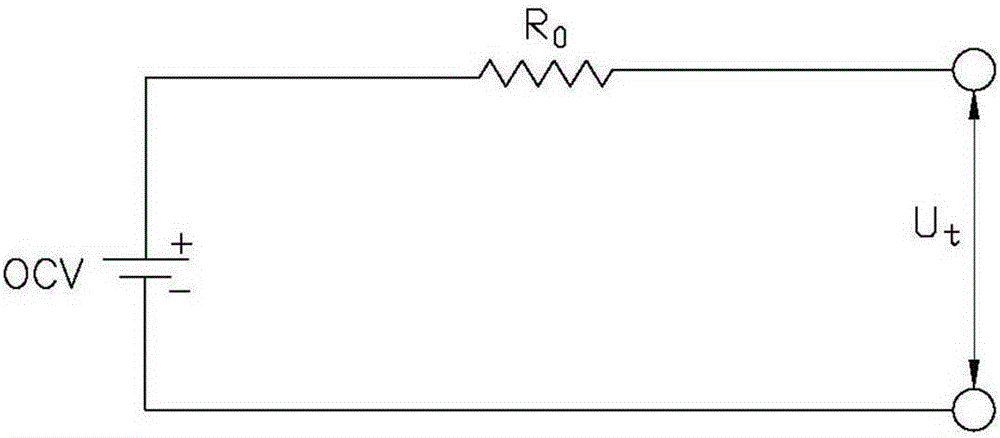

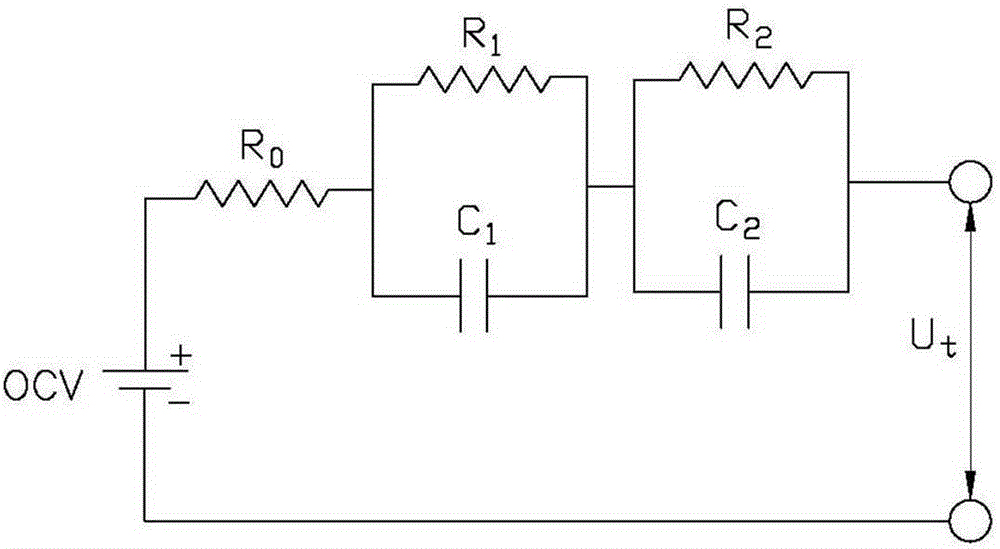

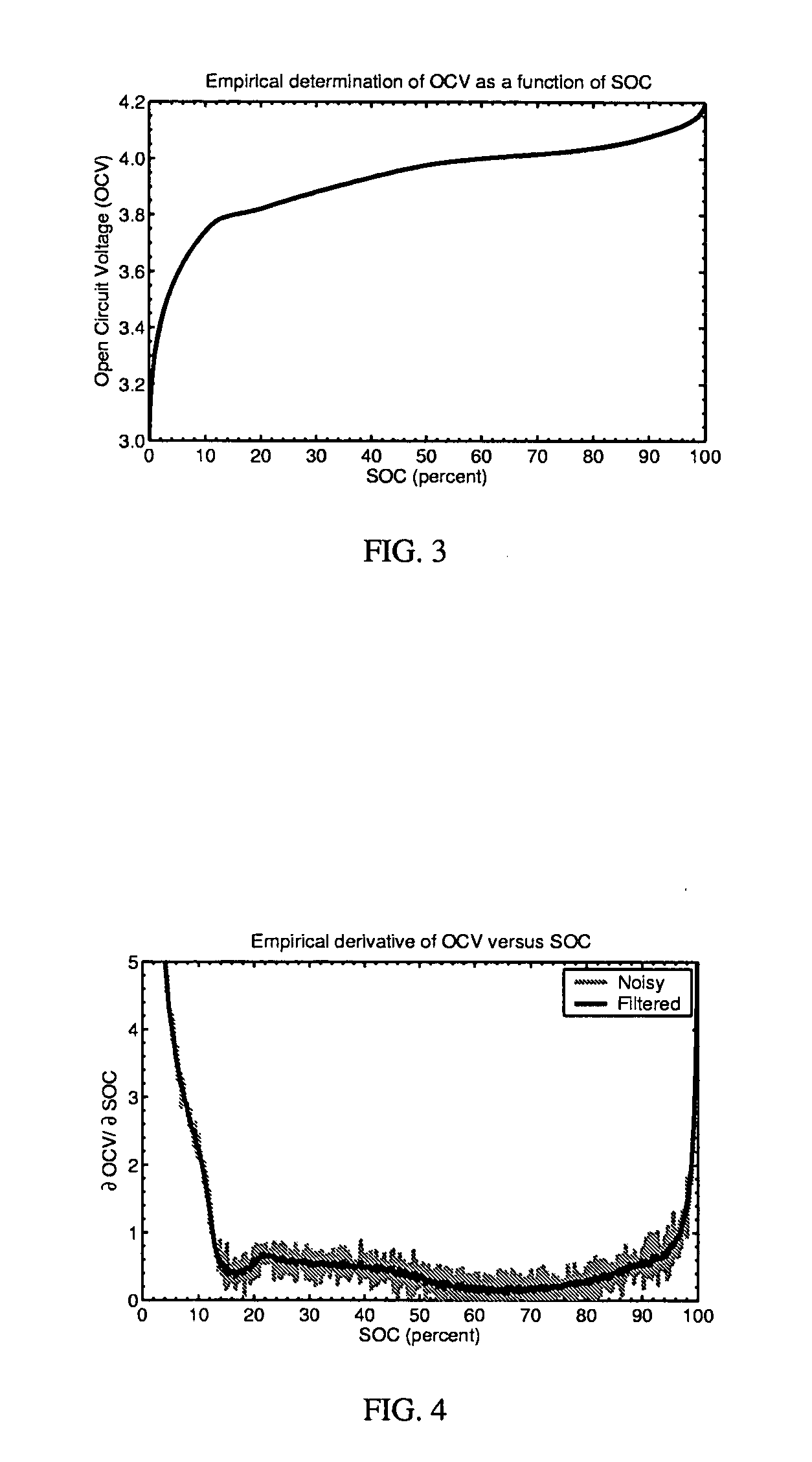

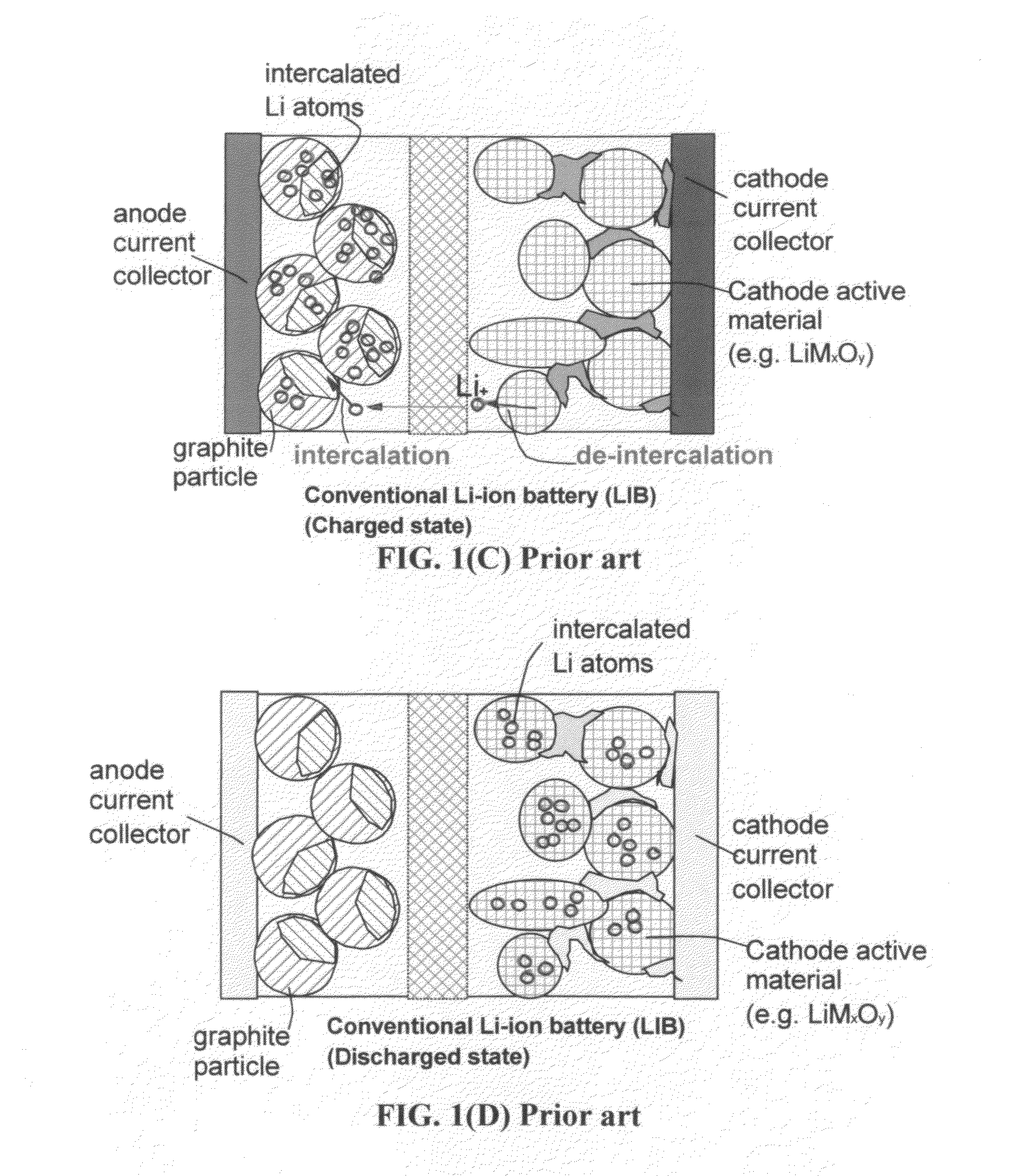

Combined estimation method for lithium ion battery state of charge, state of health and state of function

ActiveCN105301509AGuaranteed estimation accuracyImprove state estimation performanceElectrical testingInternal resistanceState of health

The invention provides a combined estimation method for lithium ion battery state of charge, state of health and state of function. The combined estimation method comprises the steps that the state of he---alth of a battery is estimated online: open circuit voltage and internal resistance are identified online by adopting a recursive least square method with a forgetting factor, the state of charge is indirectly acquired according to a pre-established OCV-SOC corresponding relation, and then the size of battery capacity is estimated according to cumulative charge and discharge electric charge between two SOC points; the state of charge of the battery is estimated online: the state of charge of the battery is estimated by adopting the Kalman filter algorithm based on a two-order RC equivalent circuit model, and the battery capacity parameter in the Kalman filter algorithm is updated according to the estimation result of battery capacity; and the state of function of the battery is estimated online: the maximum chargeable and dischargeable current is calculated based on the voltage limit and the current limit of the battery according to internal resistance obtained by online identification, and then the maximum chargeable and dischargeable function can be obtained through further calculation.

Owner:TSINGHUA UNIV

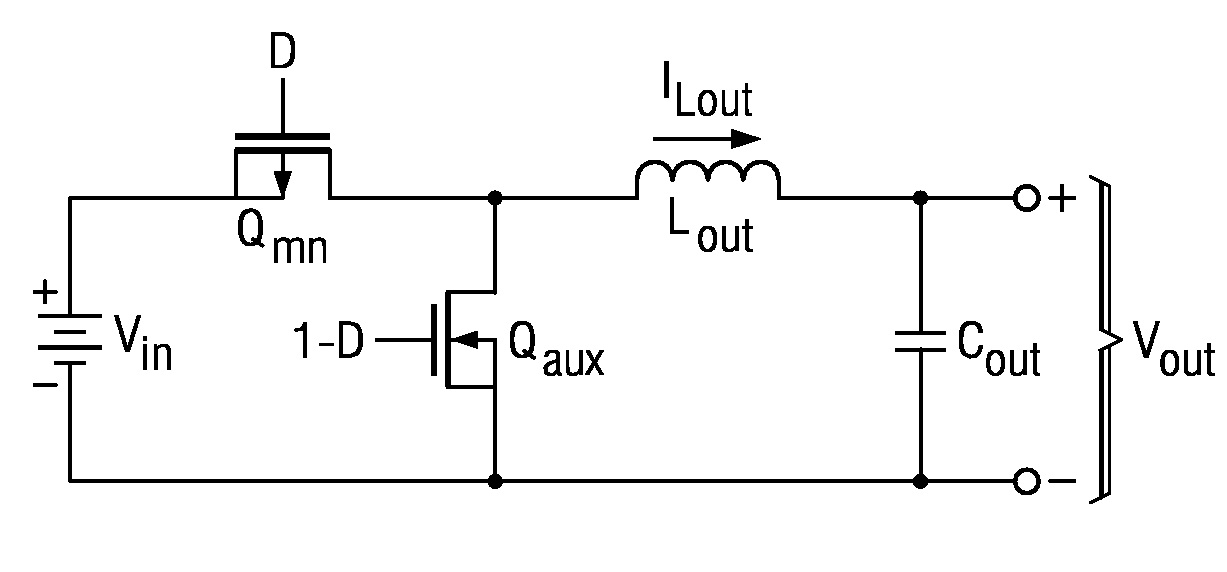

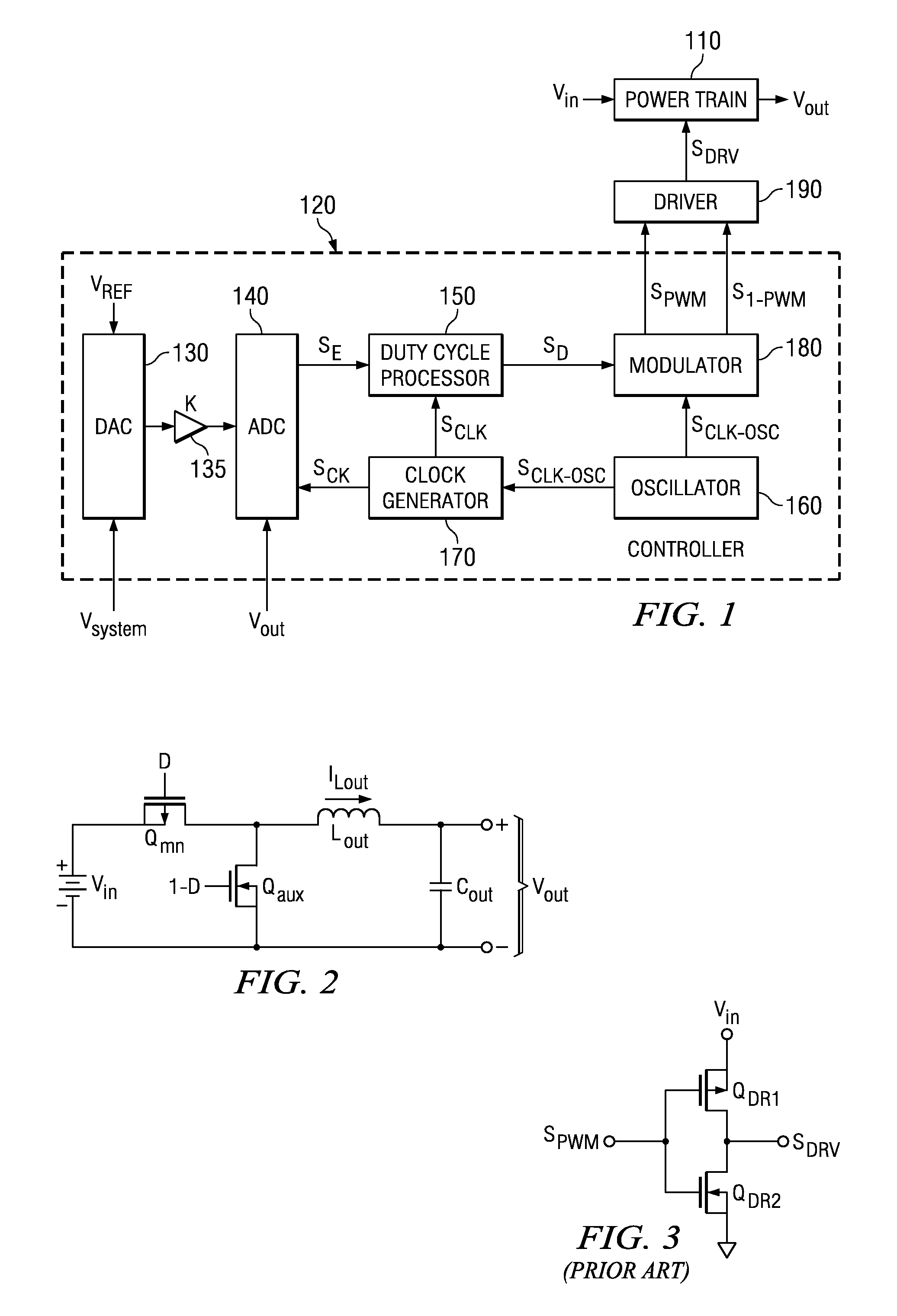

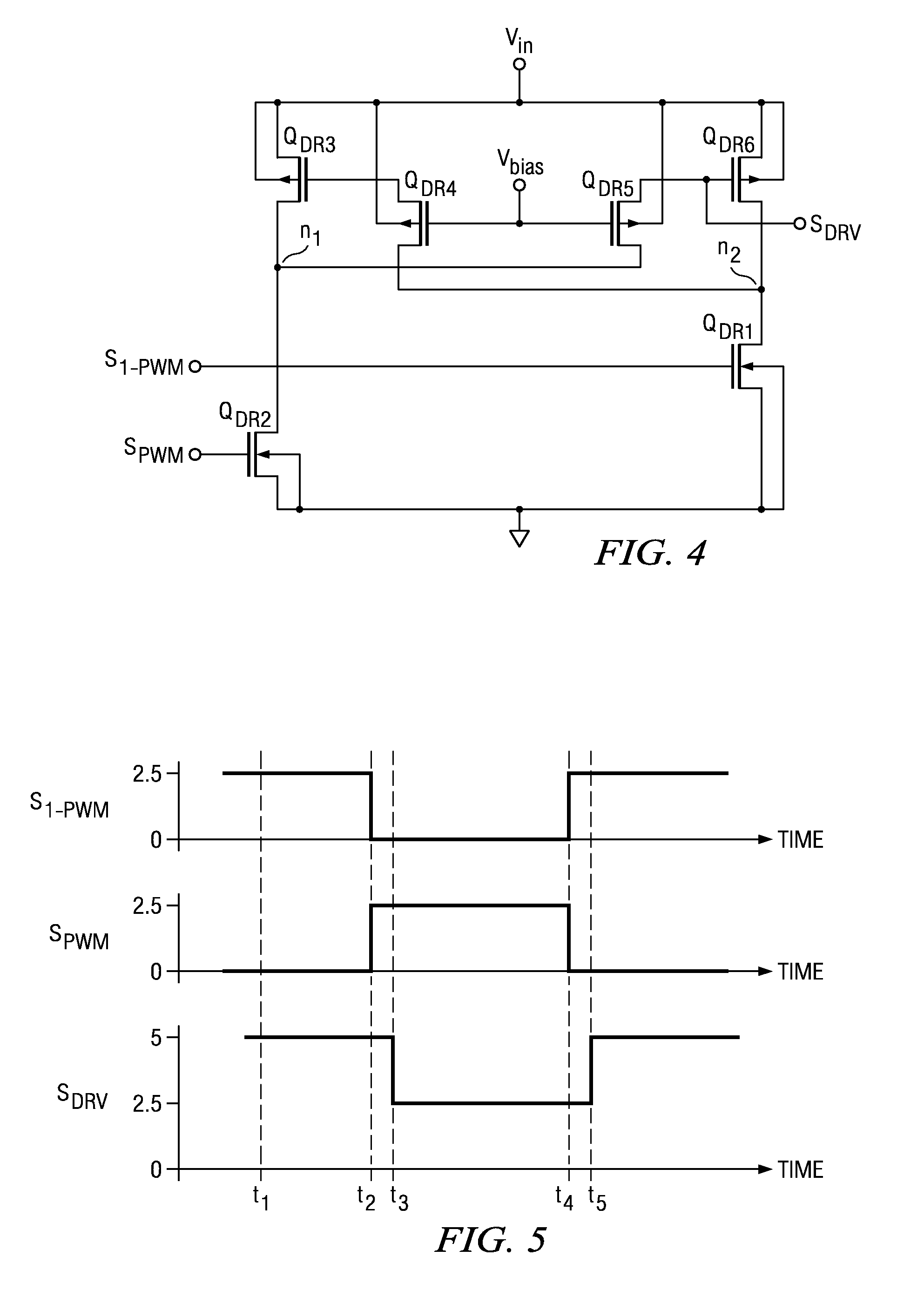

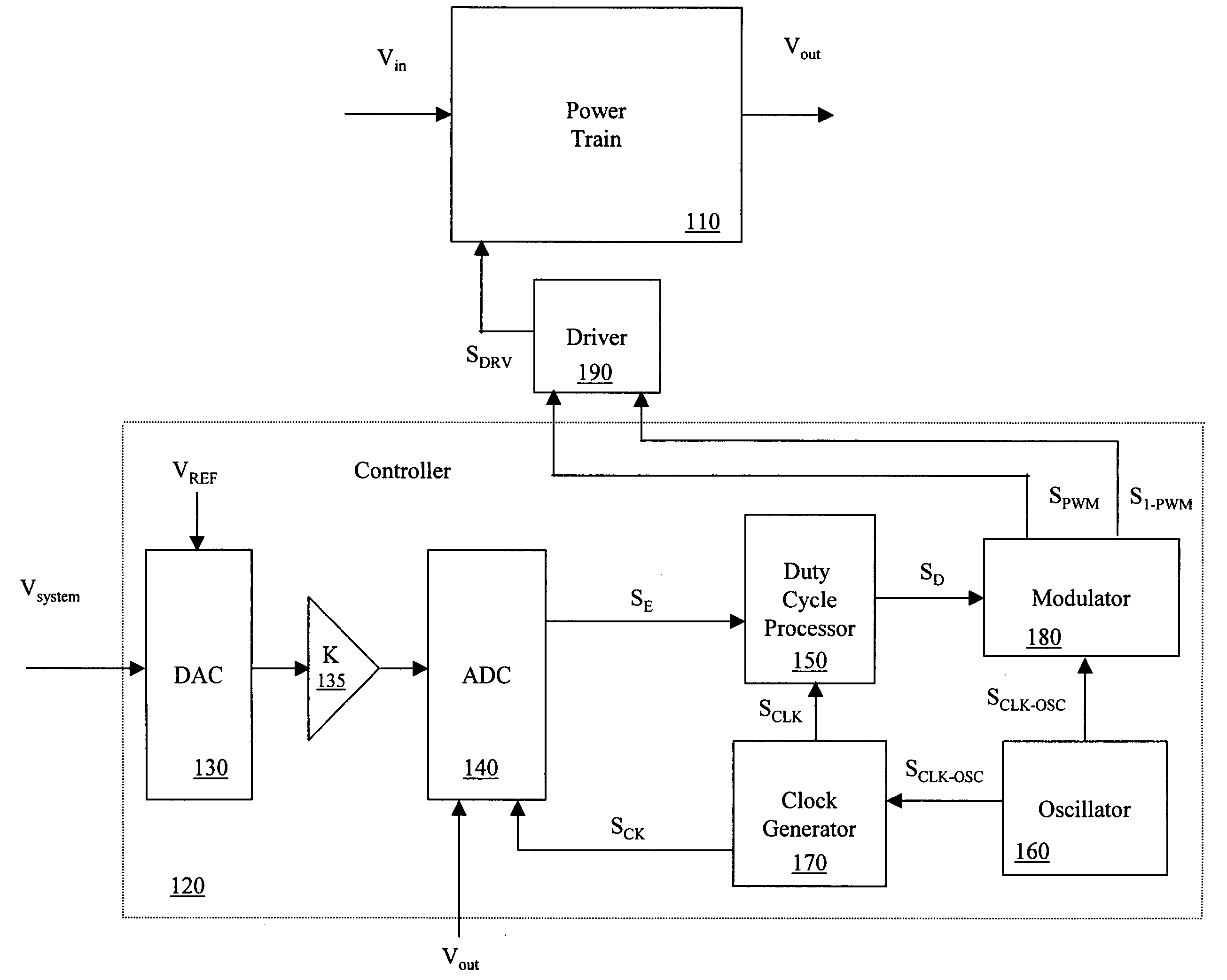

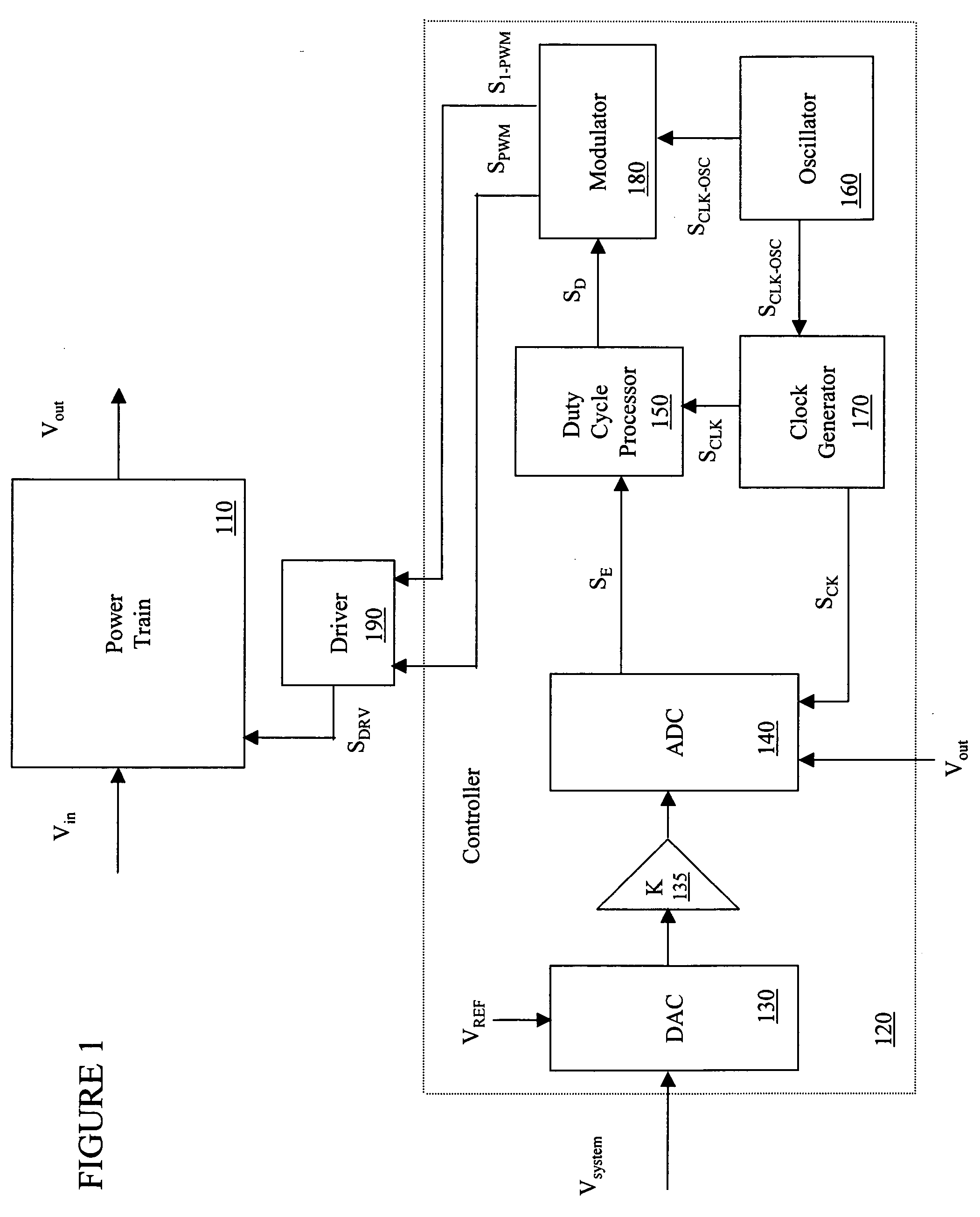

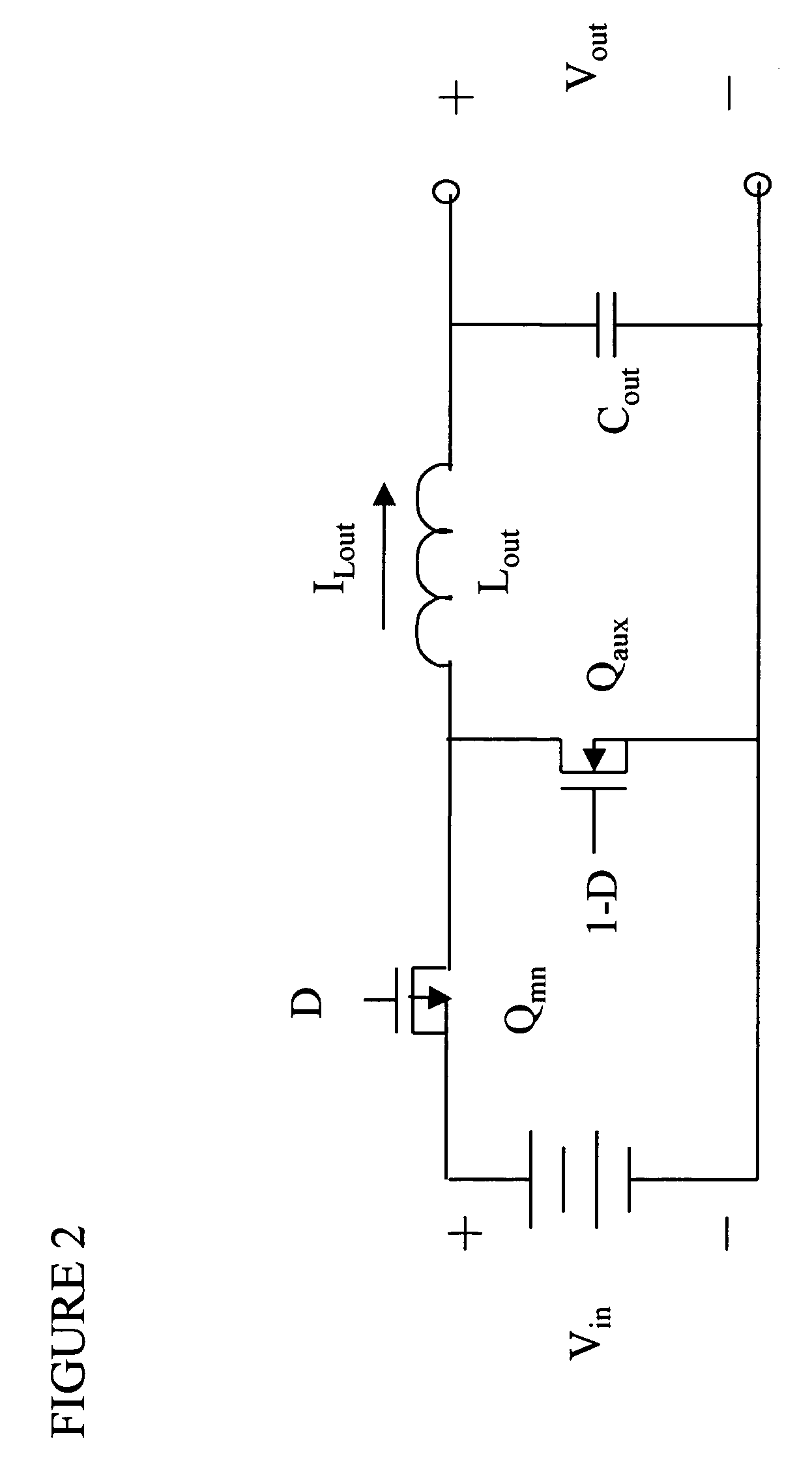

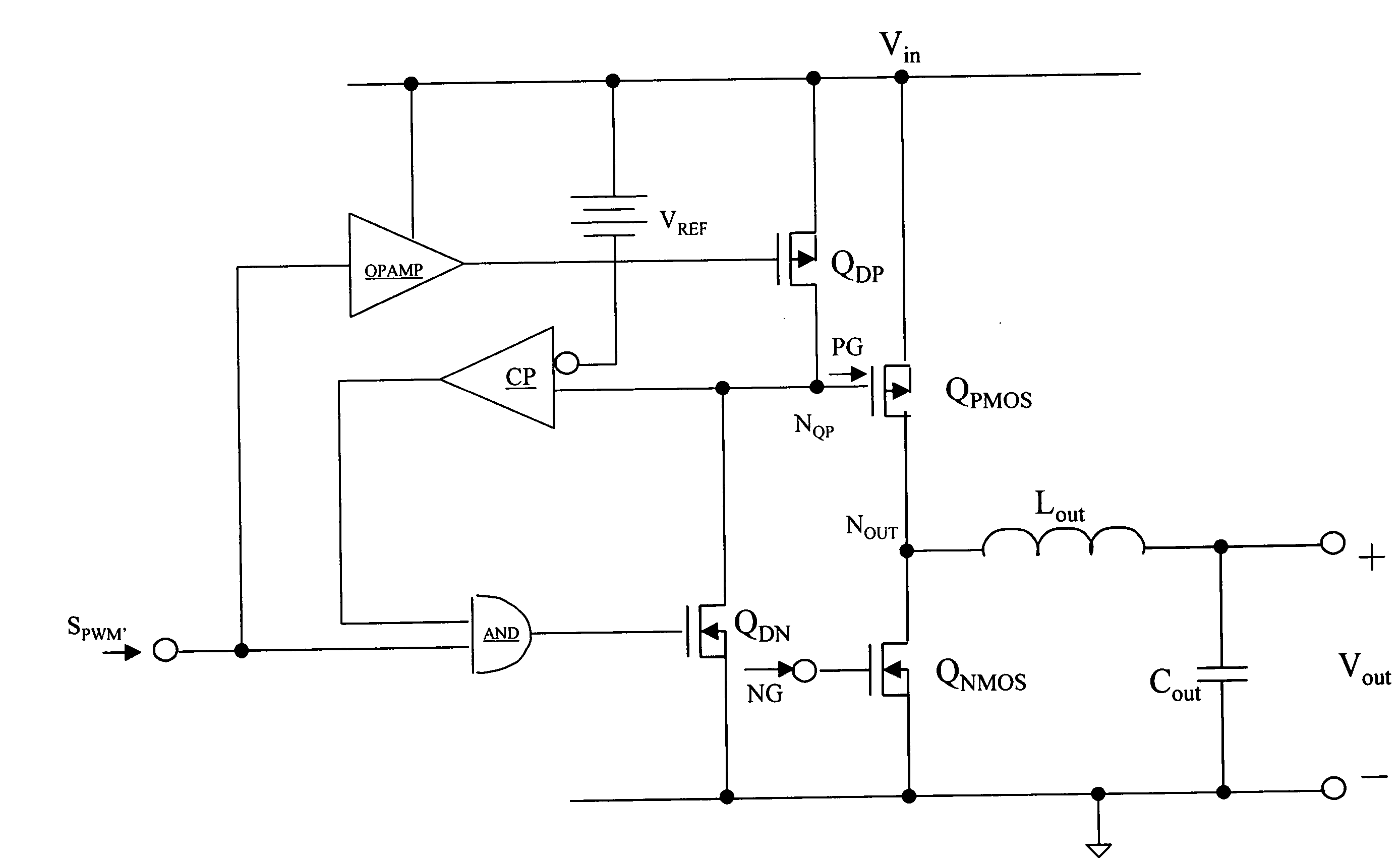

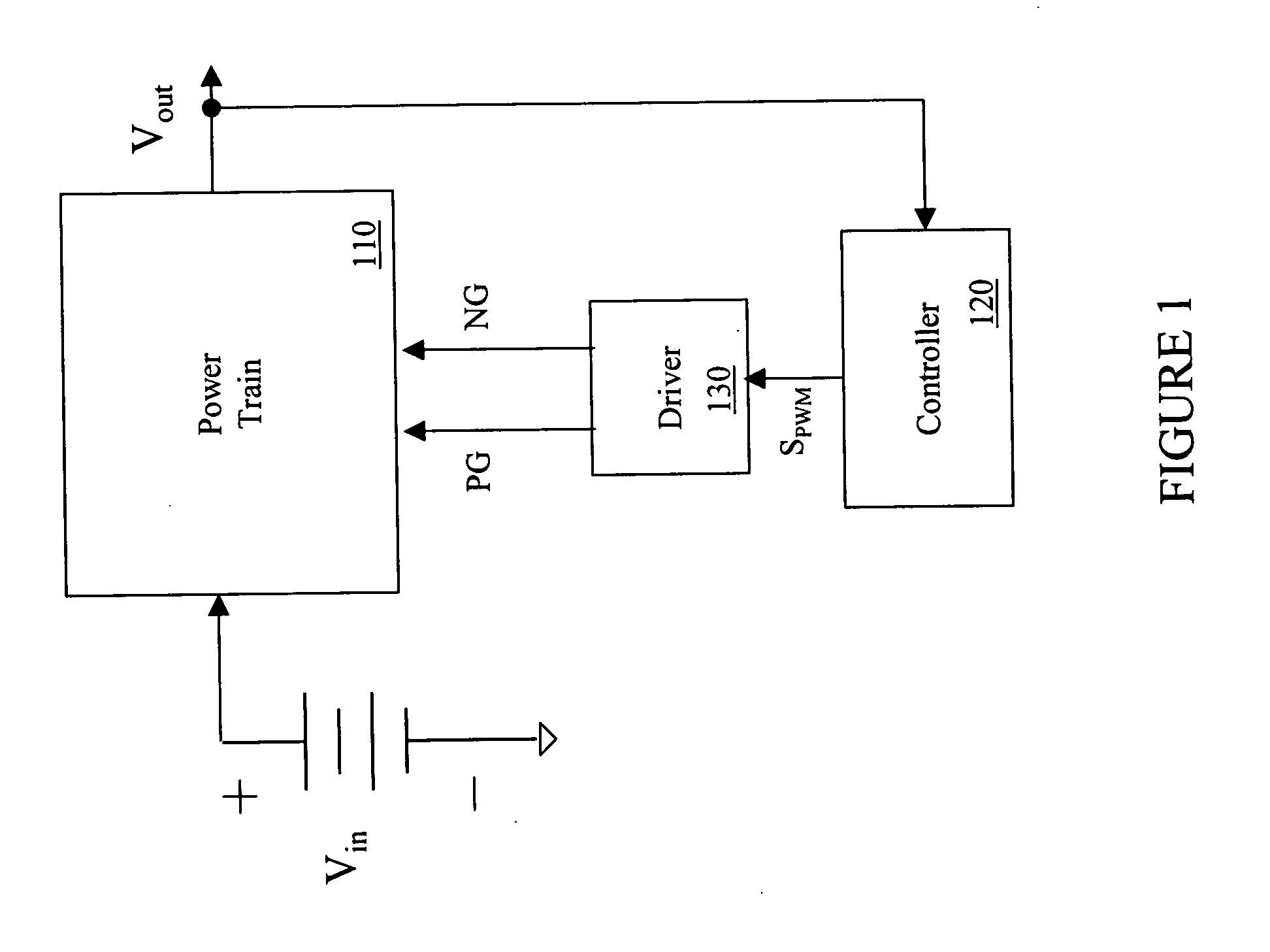

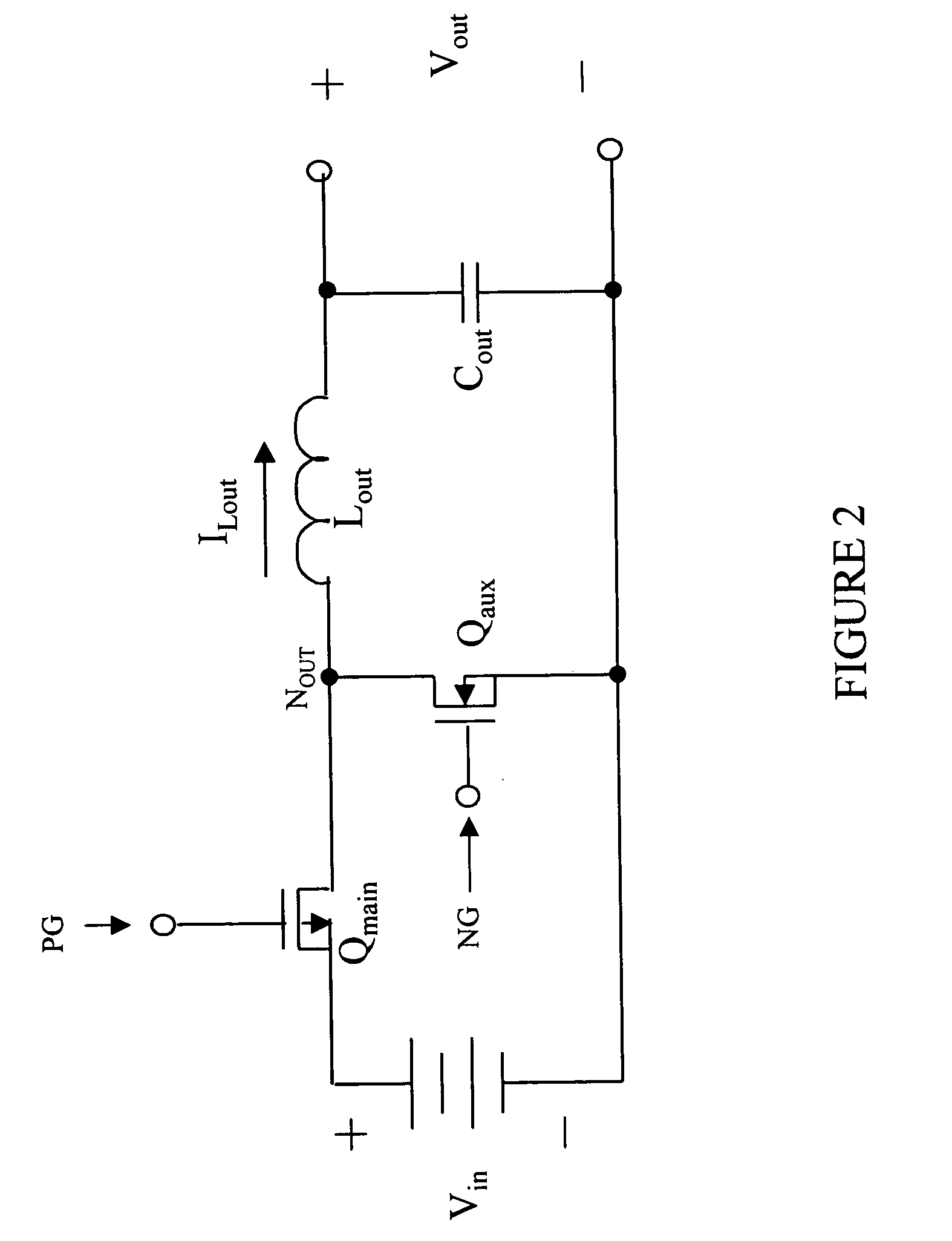

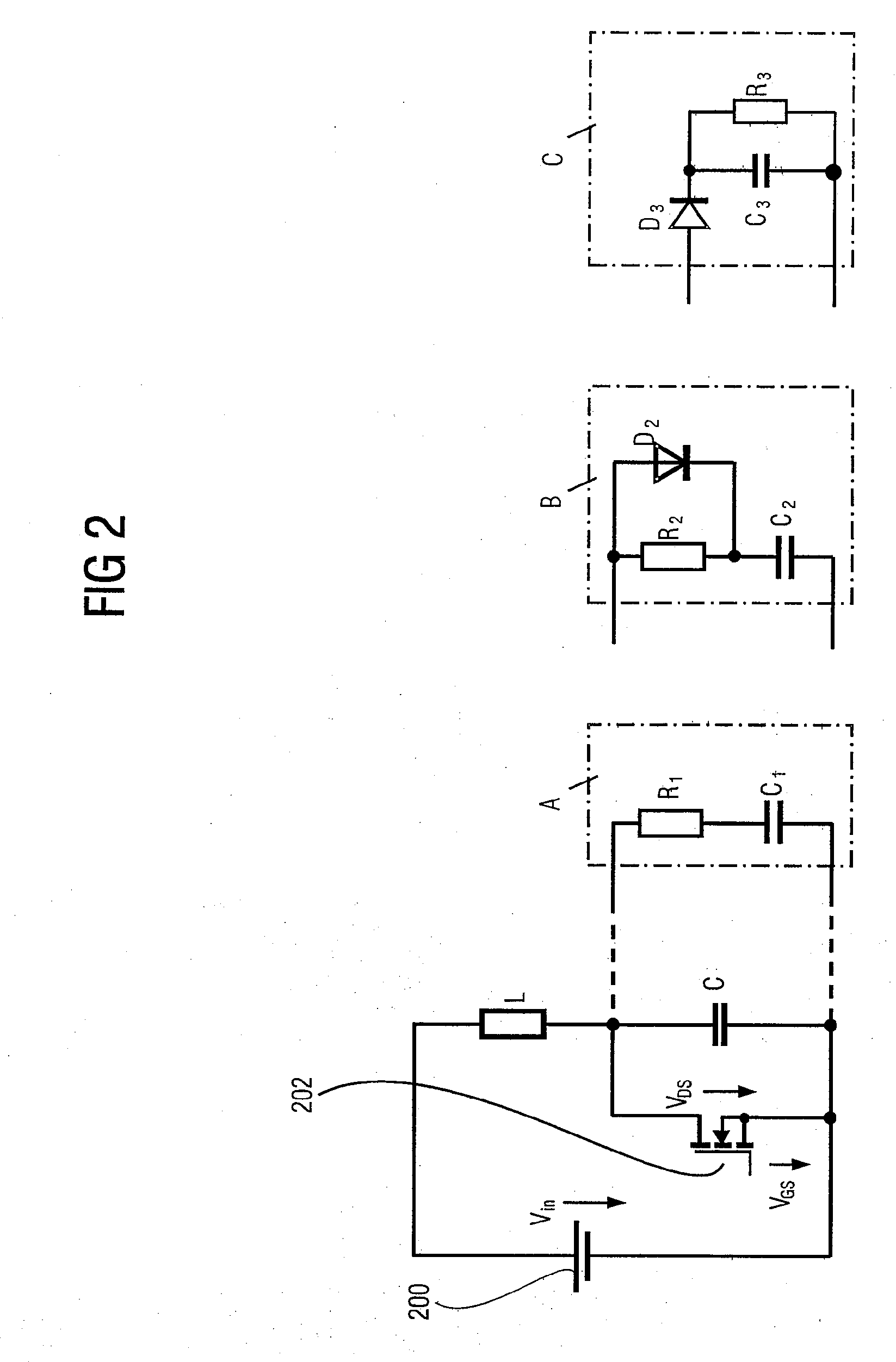

Driver for a power converter and a method of driving a switch thereof

A driver for a power converter, method of driving a switch thereof, and a power converter employing the same. In one embodiment, the driver includes switching circuitry referenced to a voltage level and configured to provide a drive signal for a switch referenced to another voltage level and subject to a control voltage limit. In a related, but alternative embodiment, the driver is employable with a power converter couplable to a source of electrical power adapted to provide an input voltage thereto. The power converter includes a power train having a switch referenced to the input voltage and subject to a control voltage limit. The driver includes switching circuitry referenced to a voltage level different from the input voltage and configured to provide a drive signal for the switch within the control voltage limit of the switch.

Owner:INTEL CORP

Driver for a power converter and a method of driving a switch thereof

A driver for a power converter, method of driving a switch thereof, and a power converter employing the same. In one embodiment, the driver includes switching circuitry referenced to a voltage level and configured to provide a drive signal for a switch referenced to another voltage level and subject to a control voltage limit. In a related, but alternative embodiment, the driver is employable with a power converter couplable to a source of electrical power adapted to provide an input voltage thereto. The power converter includes a power train having a switch referenced to the input voltage and subject to a control voltage limit. The driver includes switching circuitry referenced to a voltage level different from the input voltage and configured to provide a drive signal for the switch within the control voltage limit of the switch.

Owner:INTEL CORP

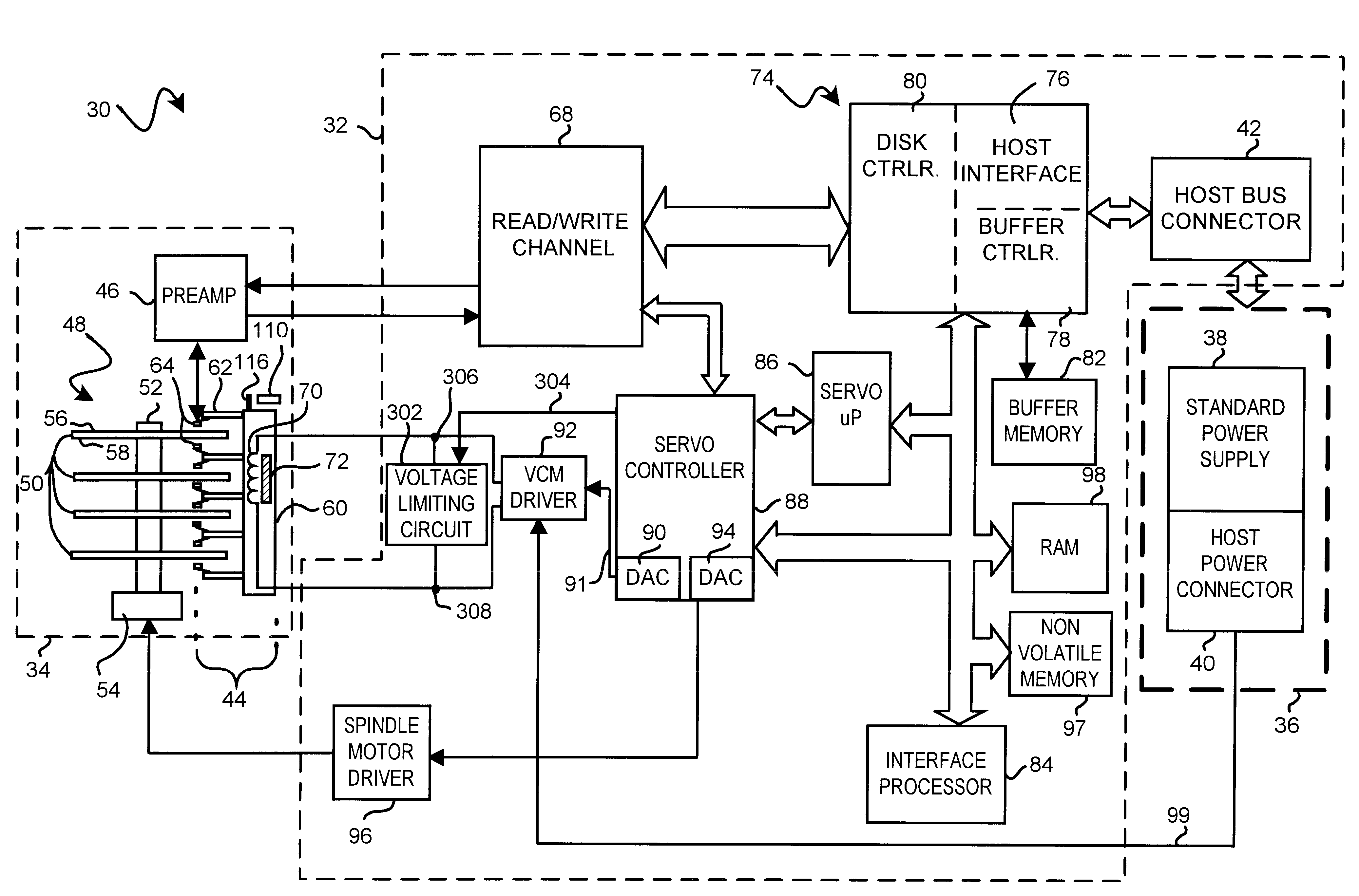

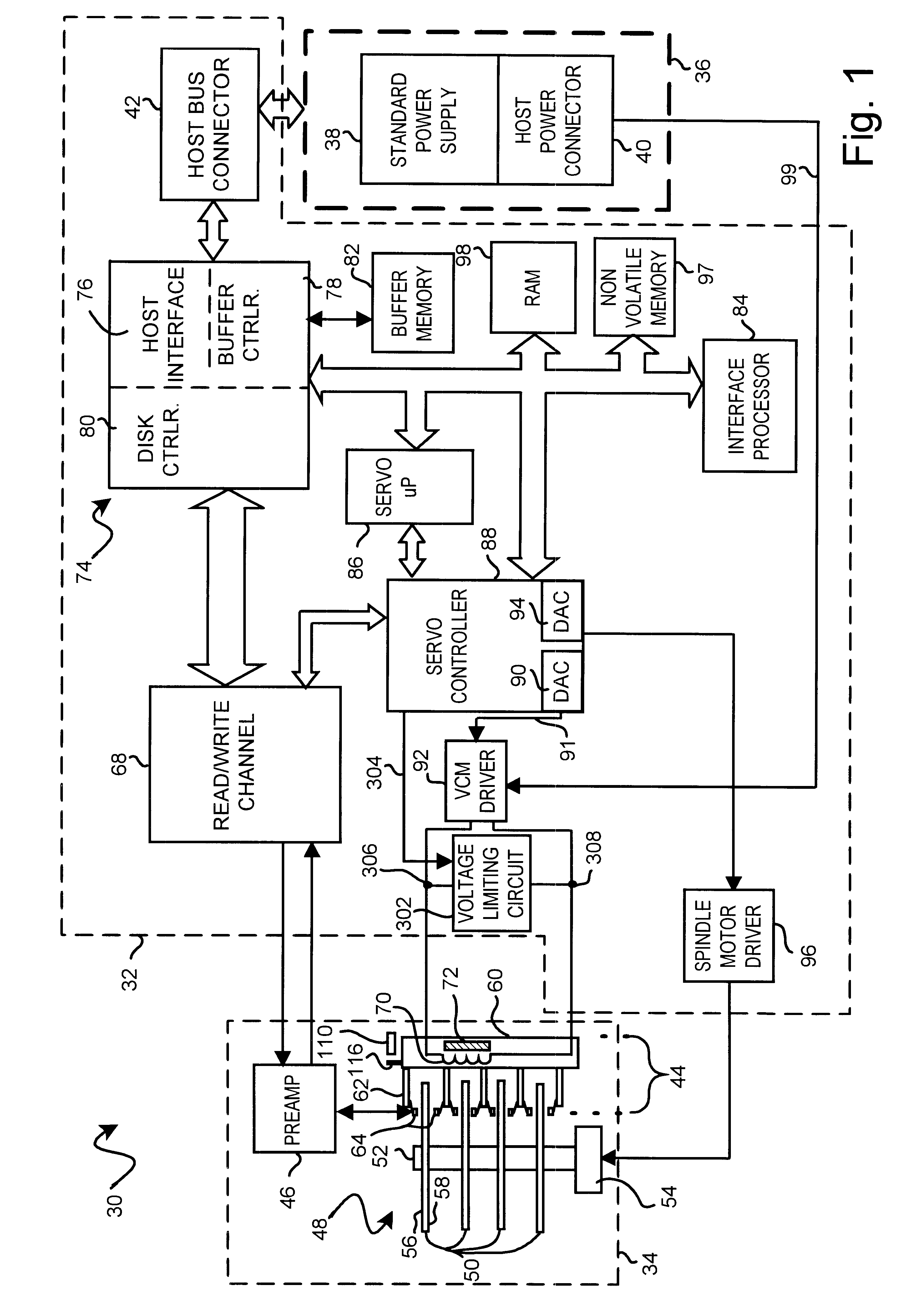

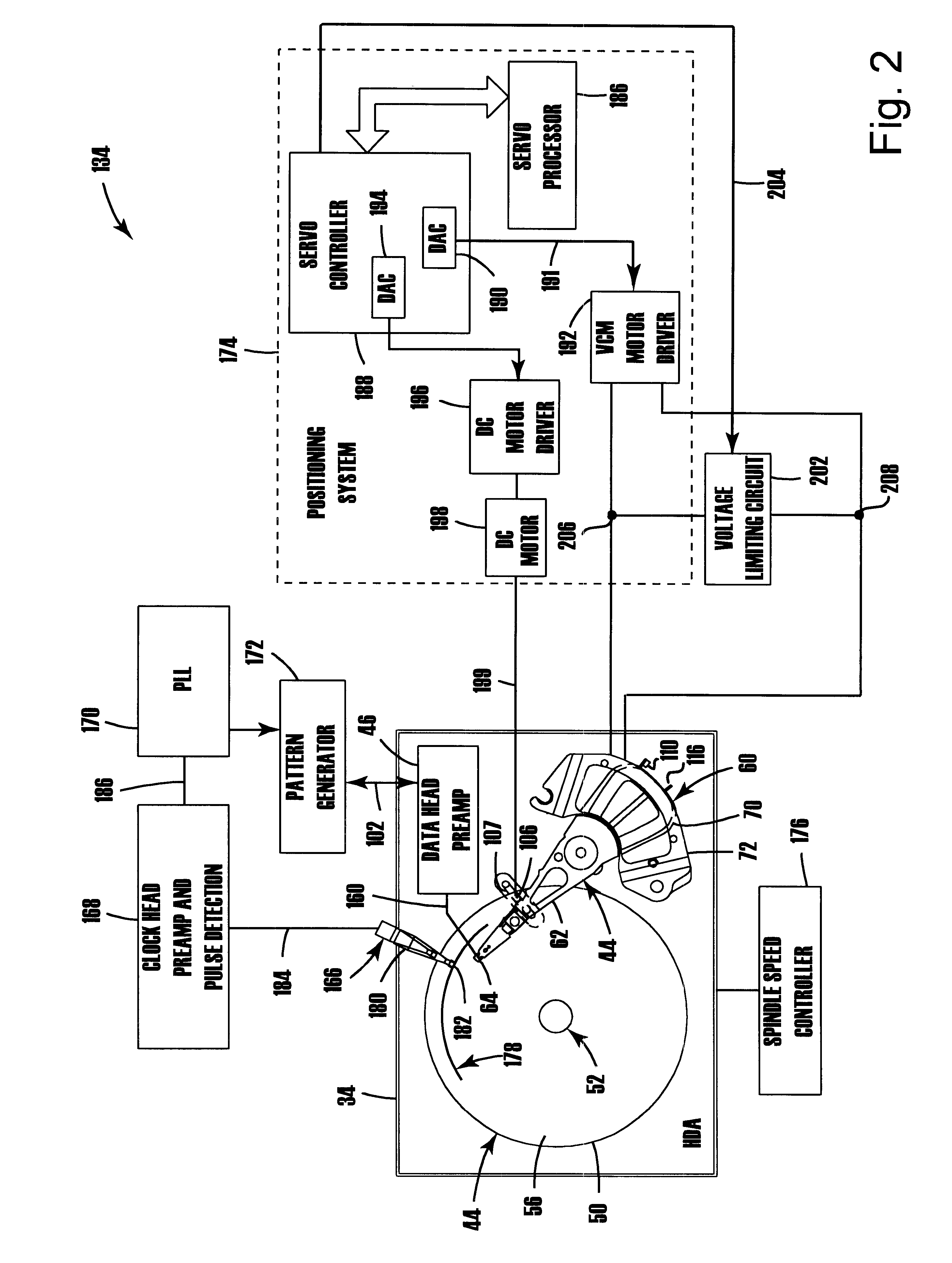

Disk drive employing method of unlatching actuator arm using VCM voltage limiting circuit to limit actuator arm velocity

InactiveUS6496324B1Driving/moving recording headsRecord information storageControl signalElectric machine

A disk drive employs a method of unlatching an actuator arm from a latch restraining the actuator arm in a disk drive. The disk drive includes a first node, a second node, and a voice coil motor (VCM) coupled to the actuator arm. The VCM includes a coil connected between the first node and the second node. The method includes applying a voltage between the first node and the second node to cause current to flow through the coil in order to move the actuator arm away from the latch at a variable actuator arm velocity. The method includes temporarily activating a VCM velocity control signal to enable a VCM voltage limiting circuit connected in parallel with the coil between the first node and the second node. The method further includes limiting the voltage applied across the coil to a predetermined VCM voltage level with the enabled VCM voltage limiting circuit in order to limit the actuator arm velocity.

Owner:WESTERN DIGITAL TECH INC

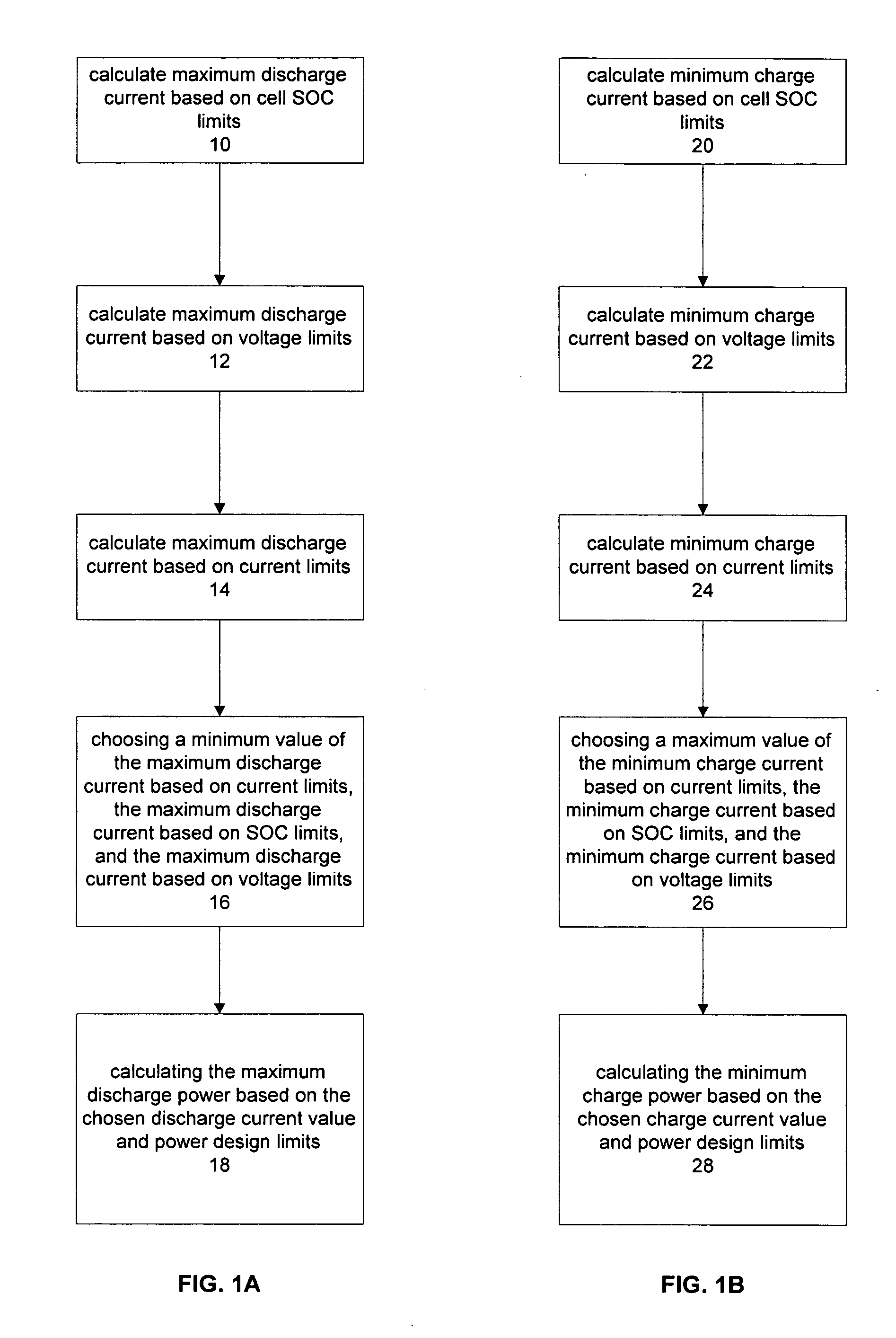

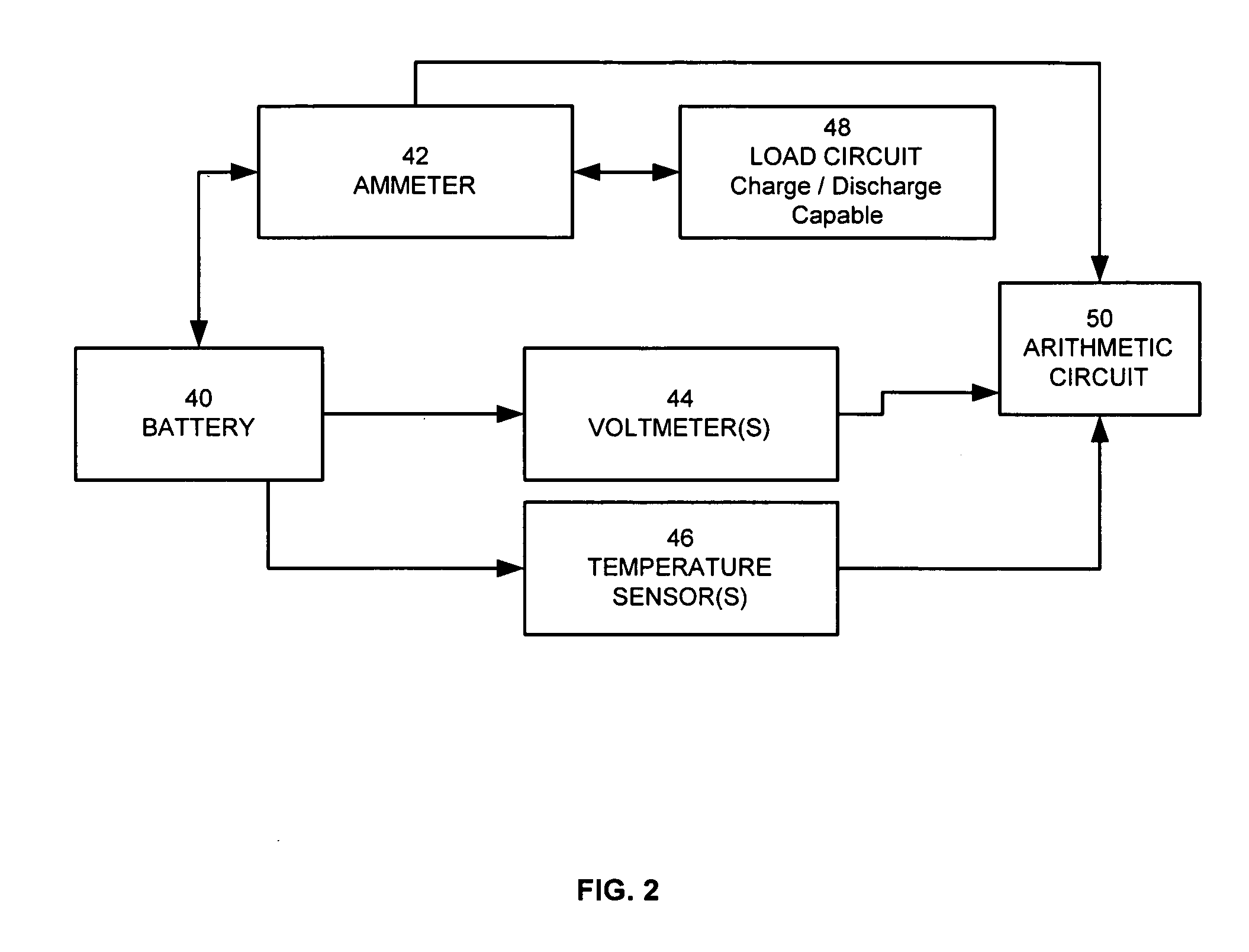

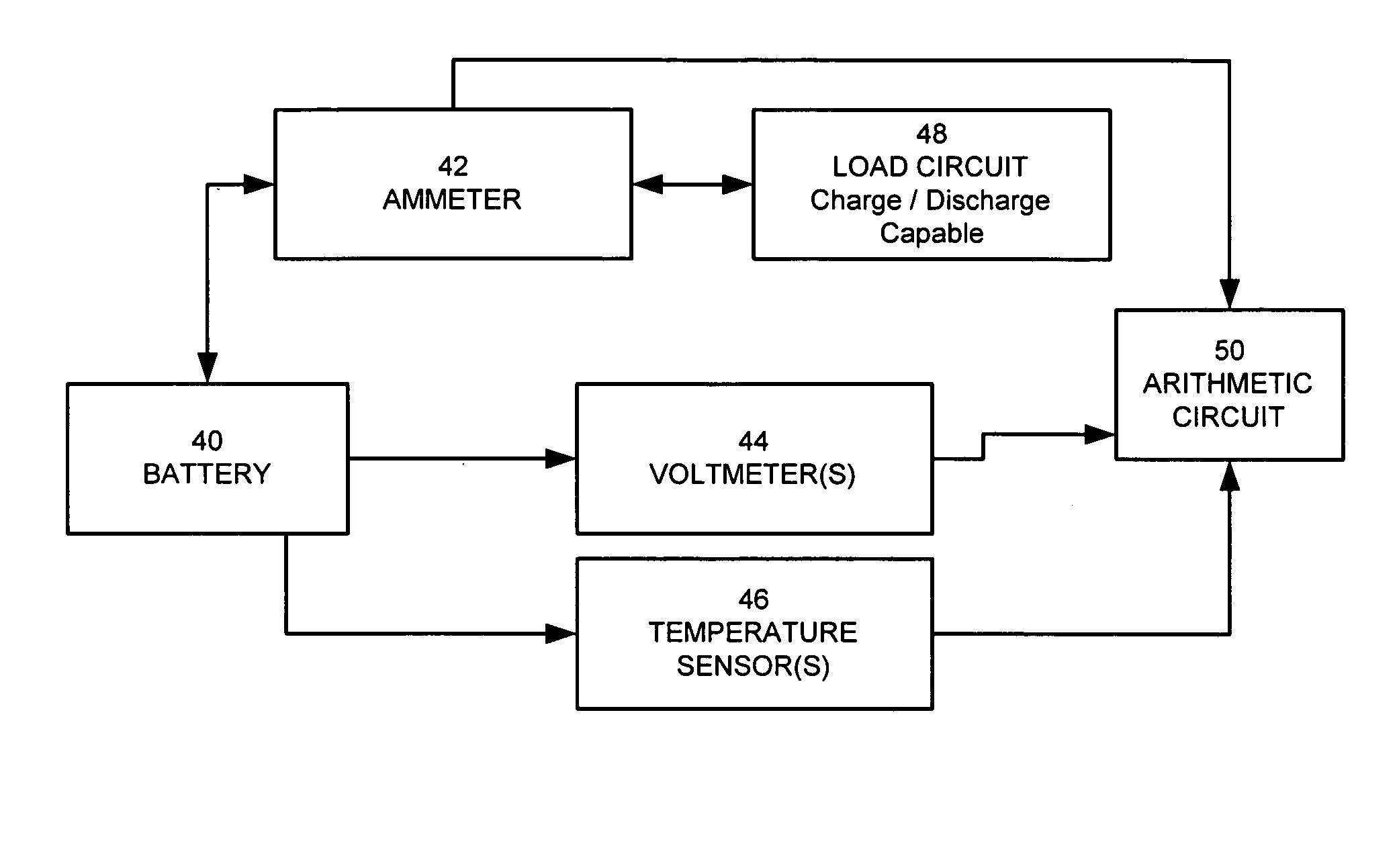

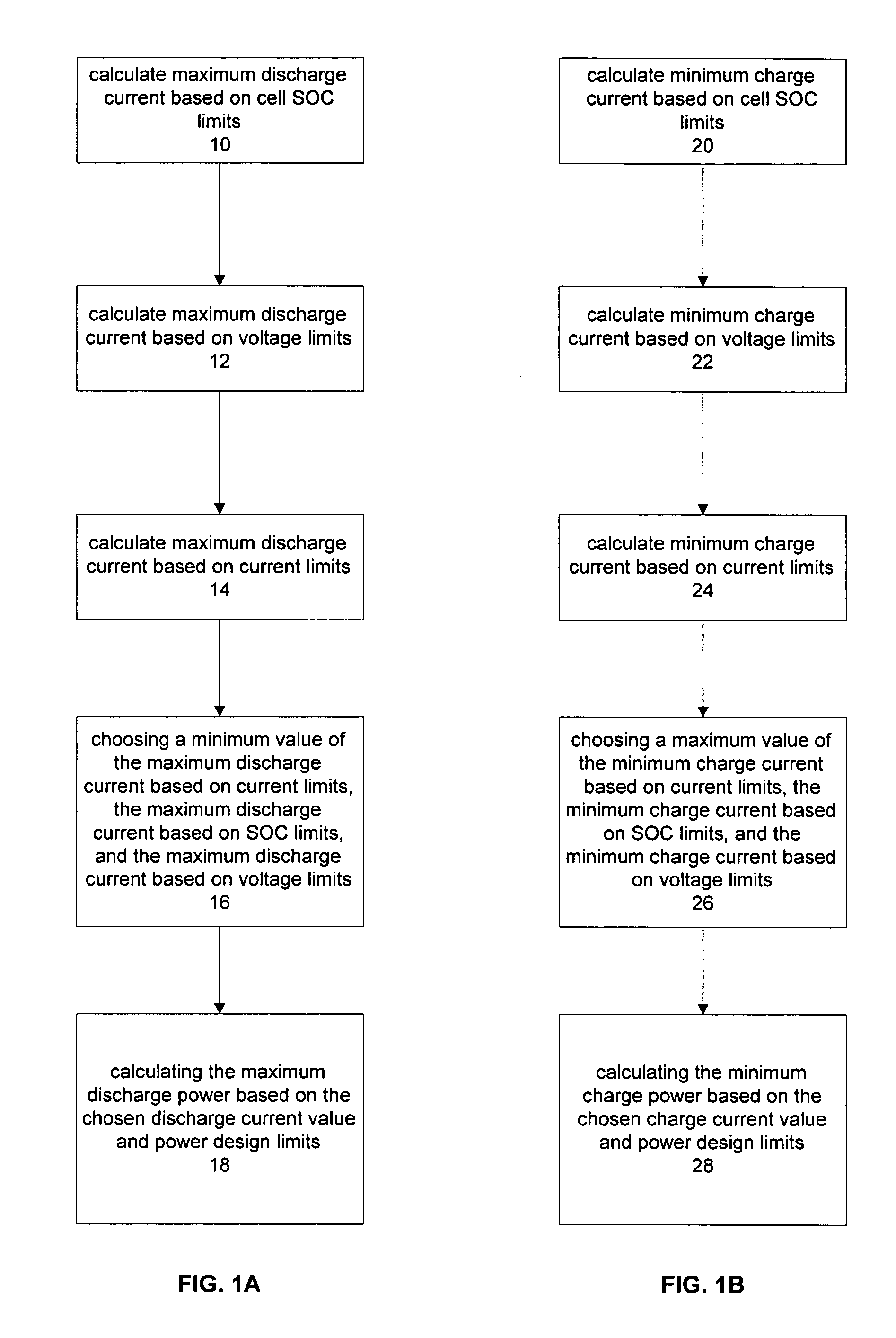

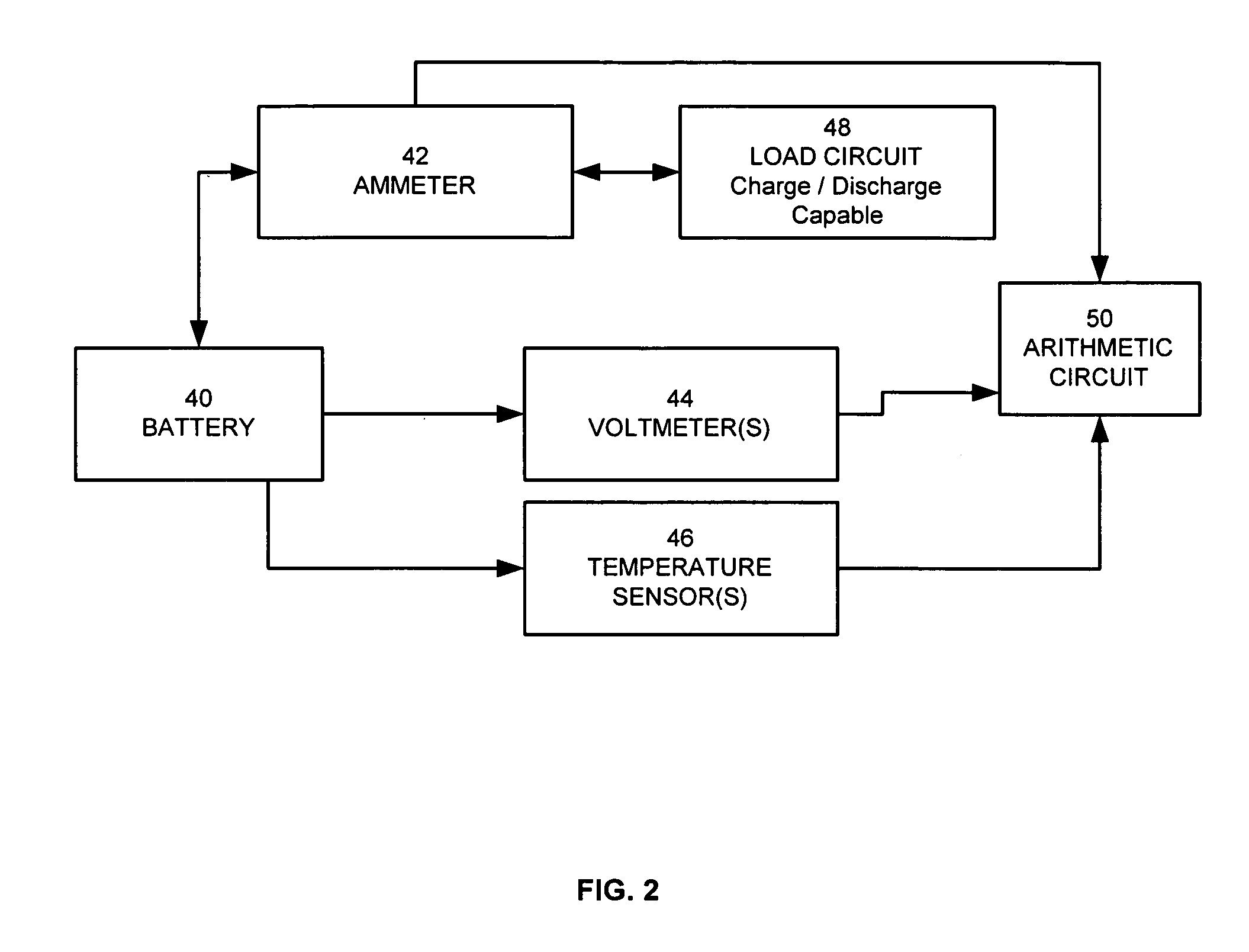

Method for calculating power capability of battery packs using advanced cell model predictive techniques

ActiveUS20050110498A1Batteries circuit arrangementsMaterial analysis by electric/magnetic meansPower capabilityElectrical battery

The present invention relates to a method and an apparatus for estimating discharge and charge power of battery applications, including battery packs used in Hybrid Electric Vehicles (HEV) and Electric Vehicles (EV). One charge / discharge power estimating method incorporates voltage, state-of-charge (SOC), power, and current design constraints and works for a user-specified prediction time horizon Δt. At least two cell models are used in calculating maximum charge / discharge power based on voltage limits. The first is a simple cell model that uses a Taylor-series expansion to linearize the equation involved. The second is a more complex and accurate model that models cell dynamics in discrete-time state-space form. The cell model can incorporate a inputs such as temperature, resistance, capacity, etc. One advantage of using model-based approach is that the same model may be used in both Kalman-filtering to produce the SOC and the estimation of maximum charge / discharge current based on voltage limits.

Owner:LG ENERGY SOLUTION LTD

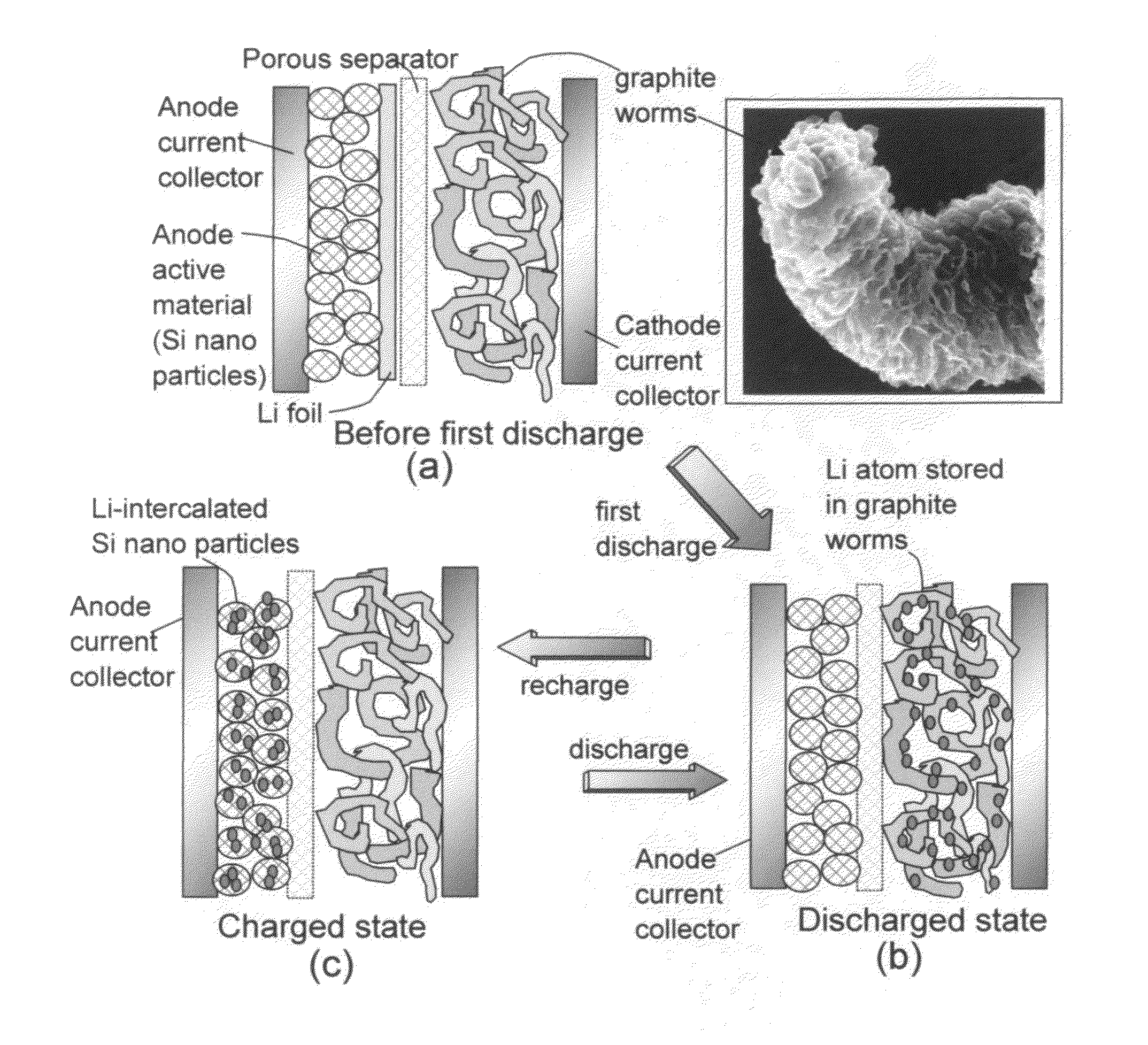

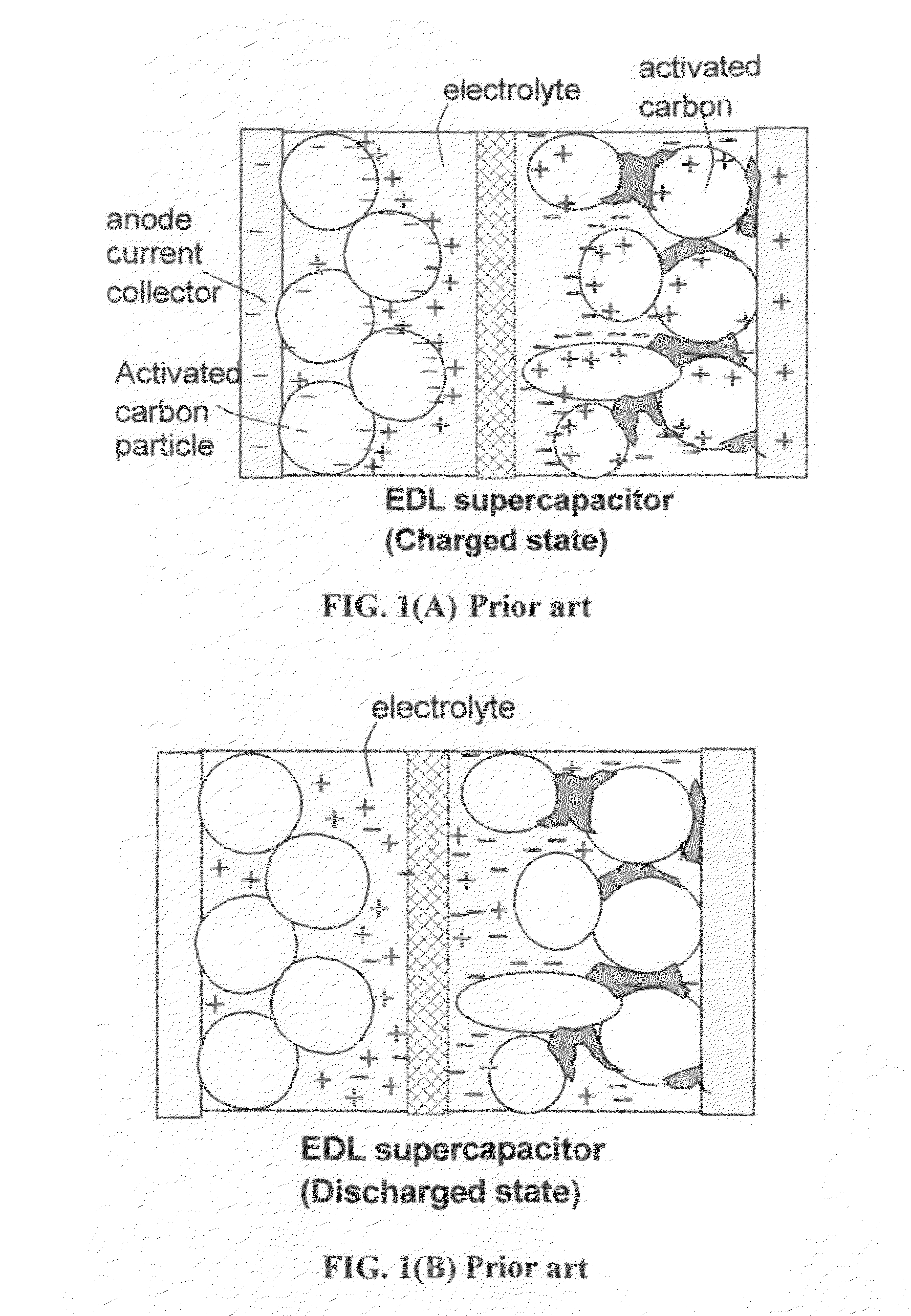

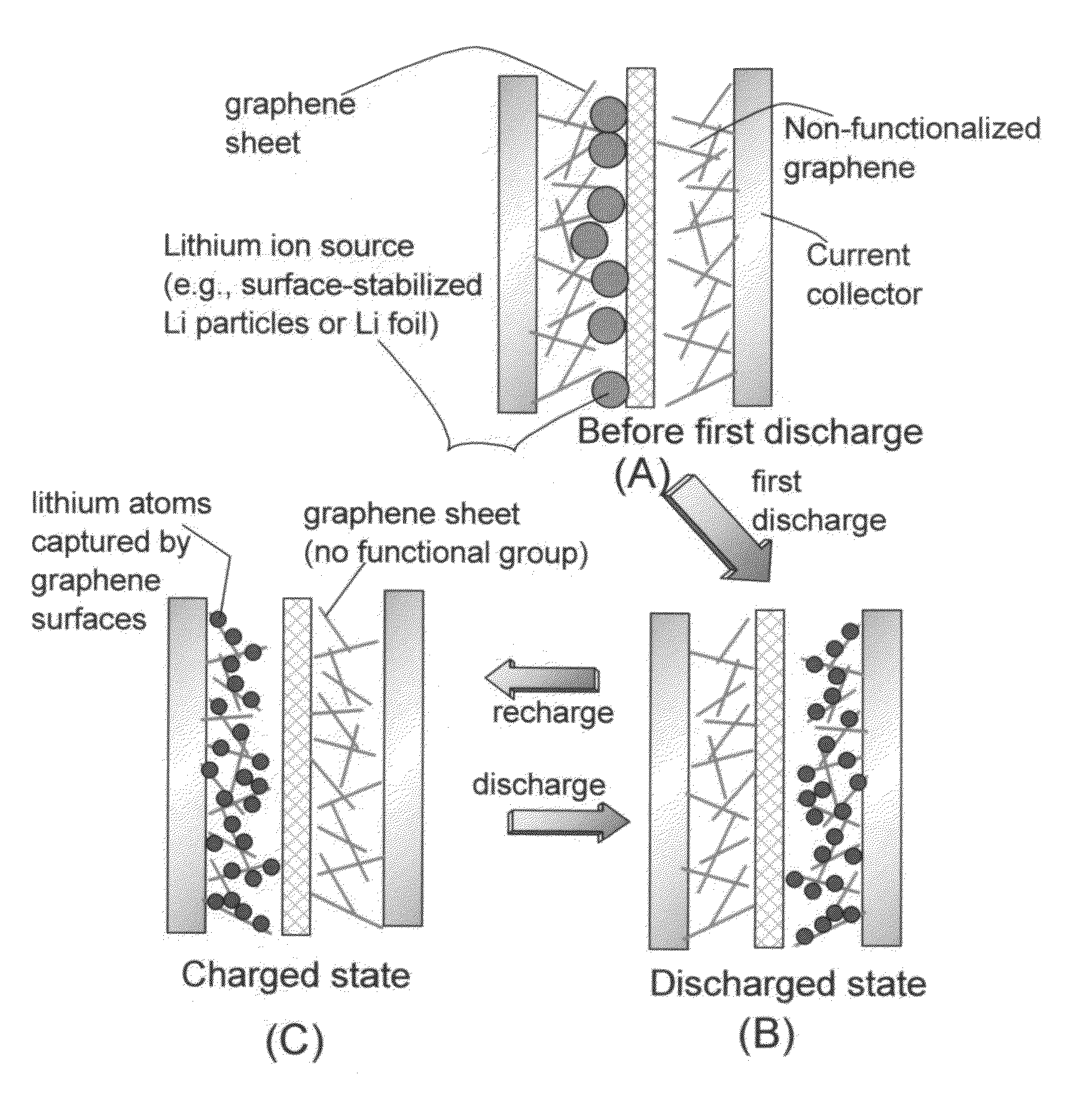

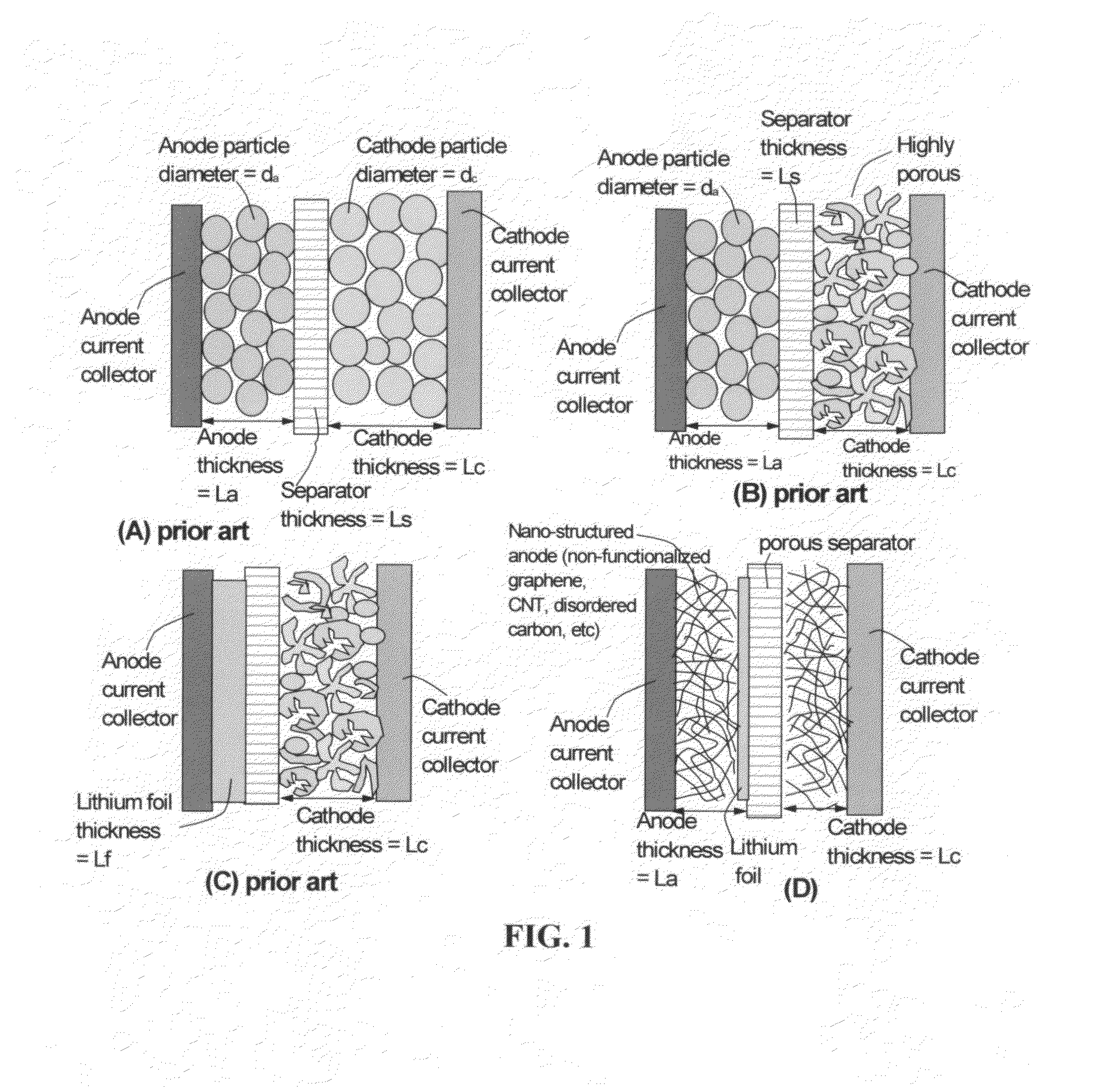

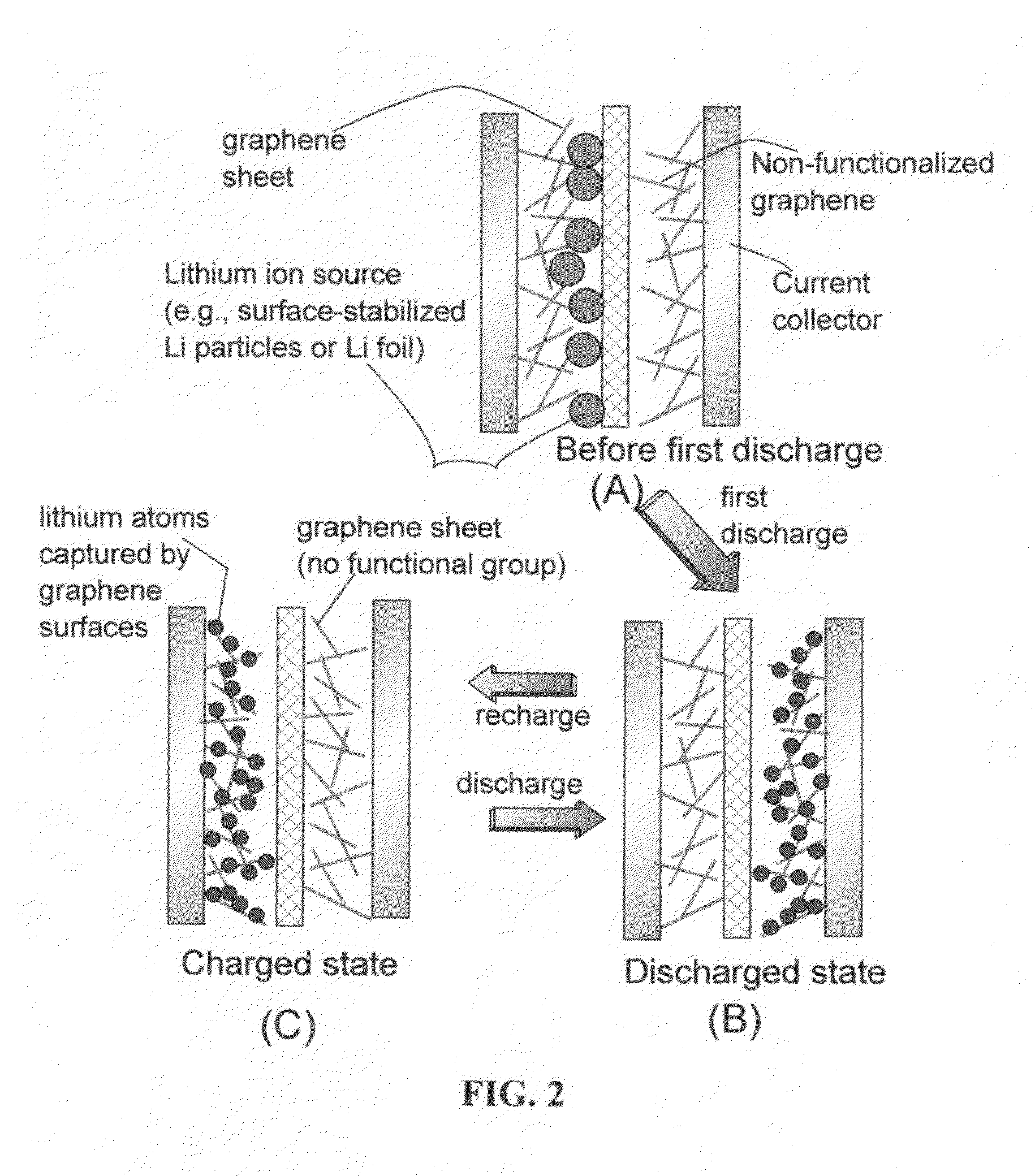

Method of operating a lithium-ion cell having a high-capacity cathode

ActiveUS20130271085A1Improvement factorImprove diffusivityMaterial nanotechnologyBatteries circuit arrangementsLithiumLow voltage

A method of operating a lithium-ion cell comprising (a) a cathode comprising a carbon or graphitic material having a surface area to capture and store lithium thereon; (b) an anode comprising an anode active material; (c) a porous separator disposed between the two electrodes; (d) an electrolyte in ionic contact with the two electrodes; and (e) a lithium source disposed in at least one of the two electrodes to obtain an open circuit voltage (OCV) from 0.5 volts to 2.8 volts when the cell is made; wherein the method comprises: (A) electrochemically forming the cell from the OCV to either a first lower voltage limit (LVL) or a first upper voltage limit (UVL), wherein the first LVL is no lower than 0.1 volts and the first UVL is no higher than 4.6 volts; and (B) cycling the cell between a second LVL and a second UVL.

Owner:GLOBAL GRAPHENE GRP INC

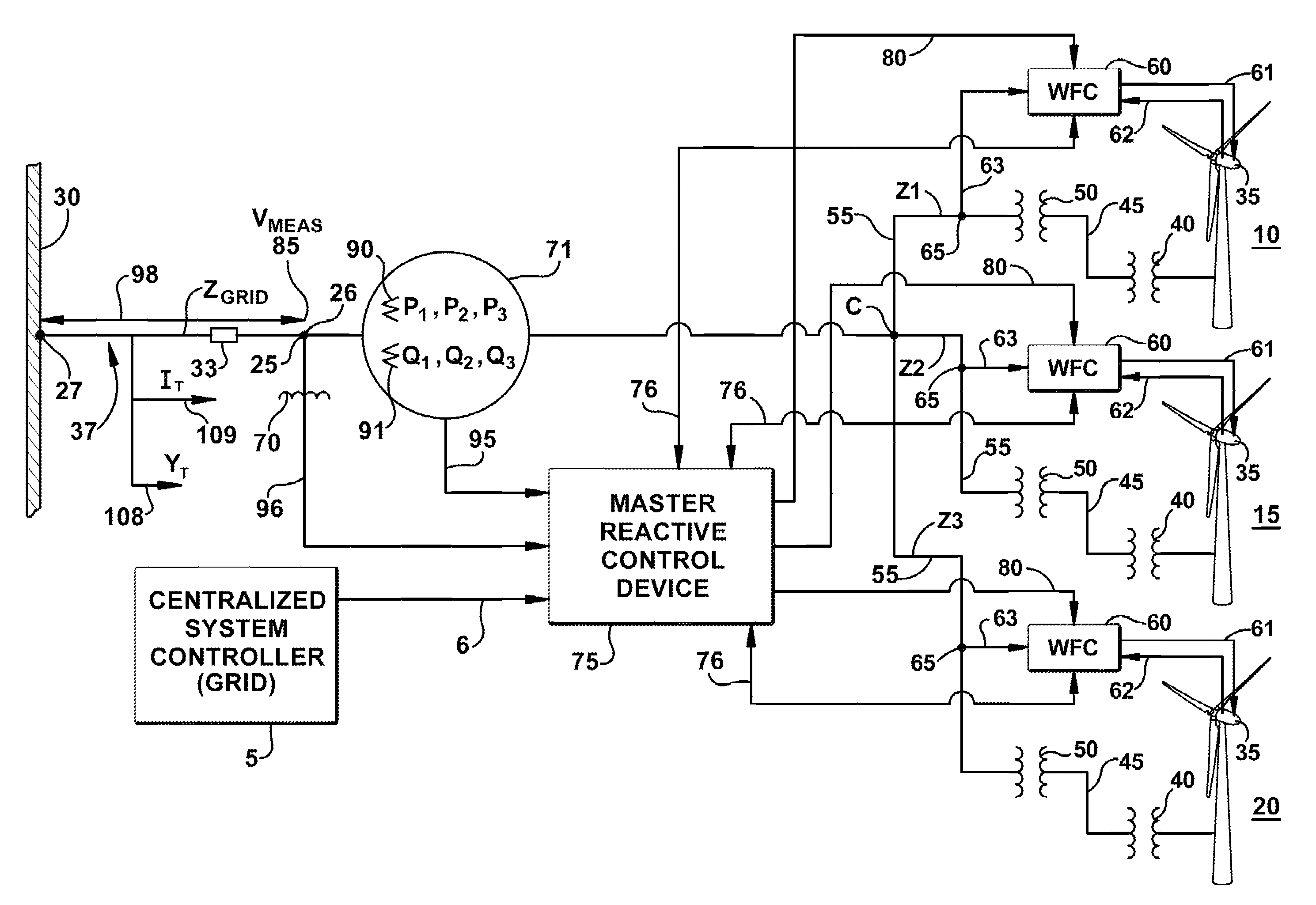

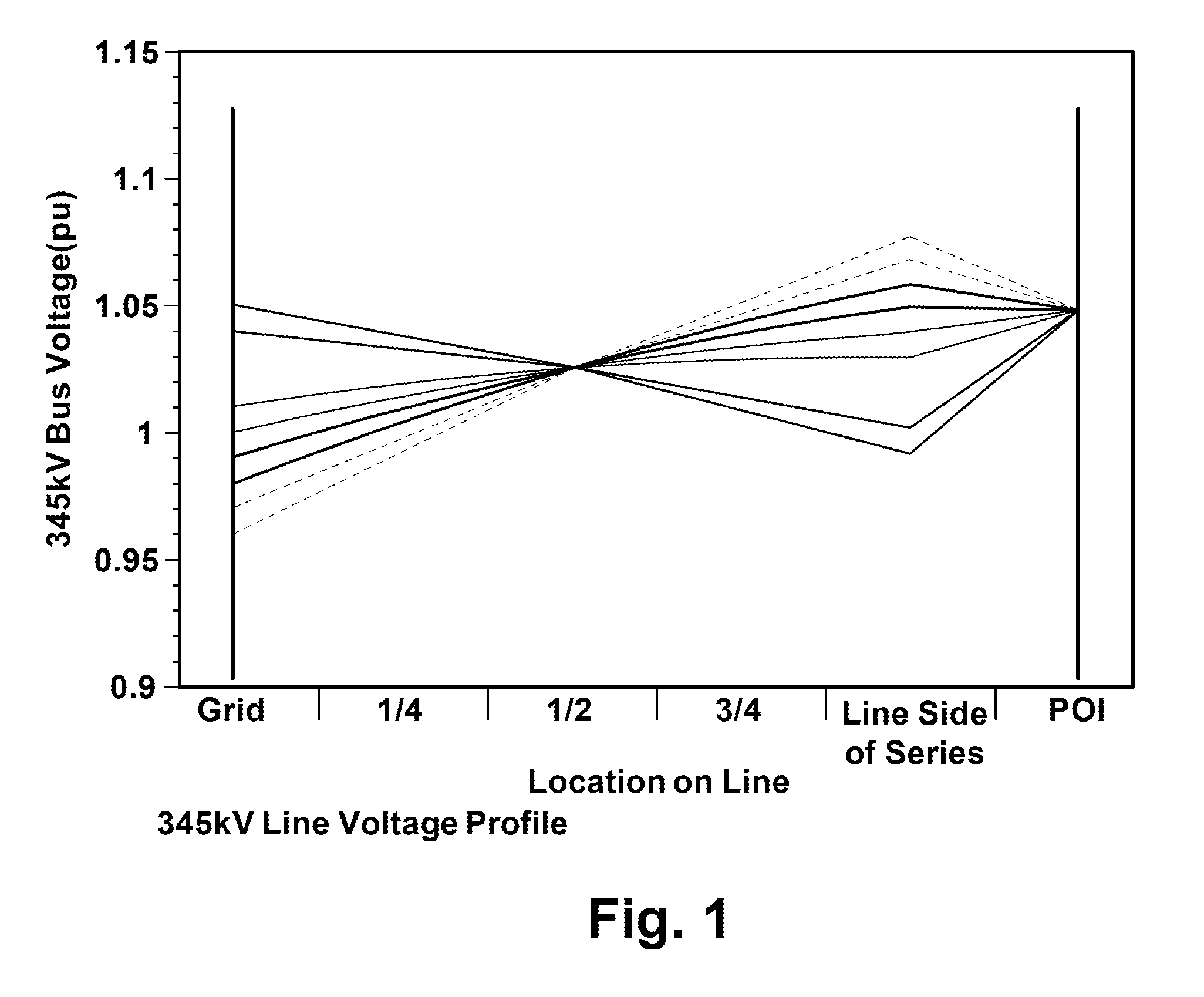

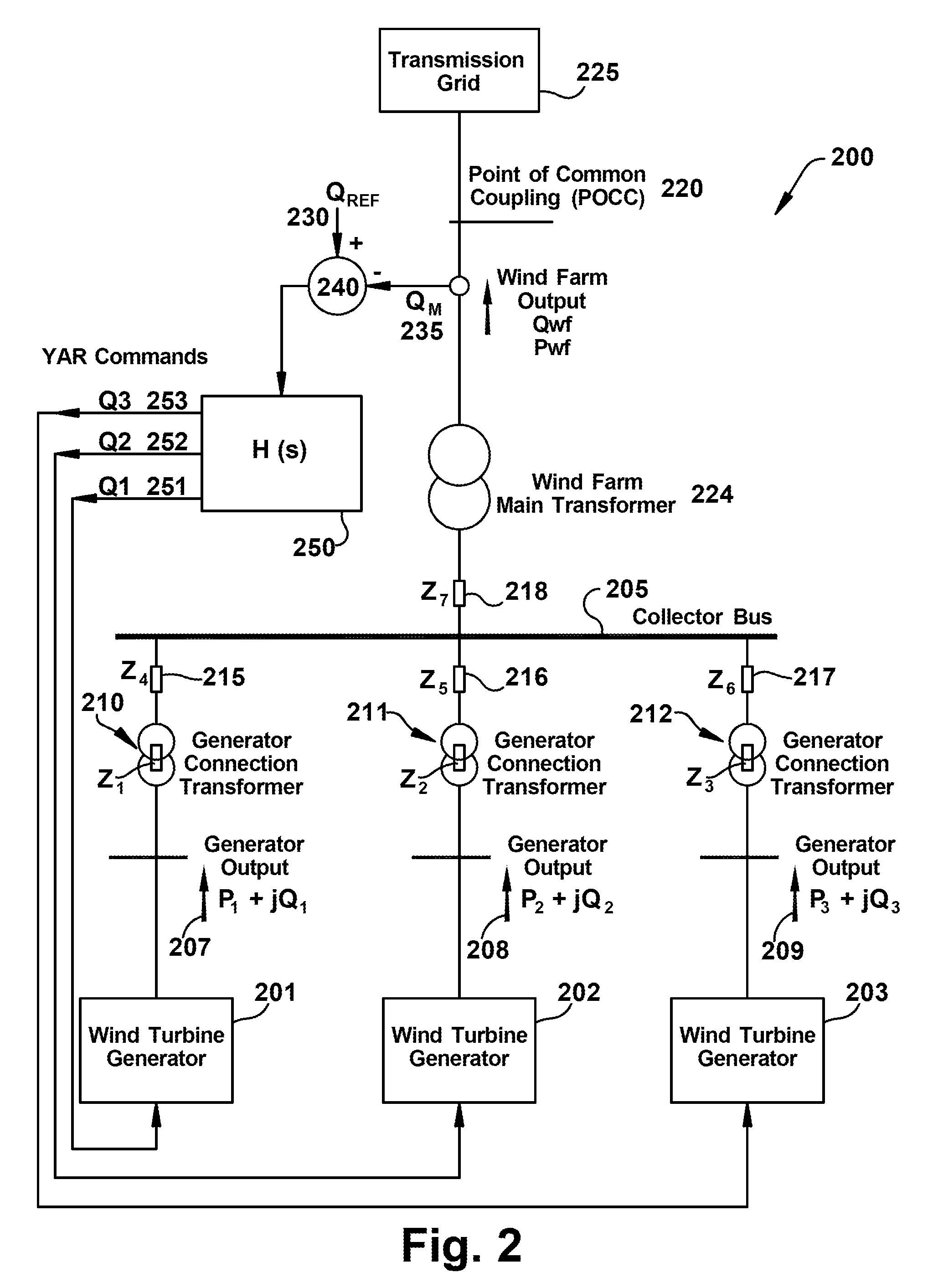

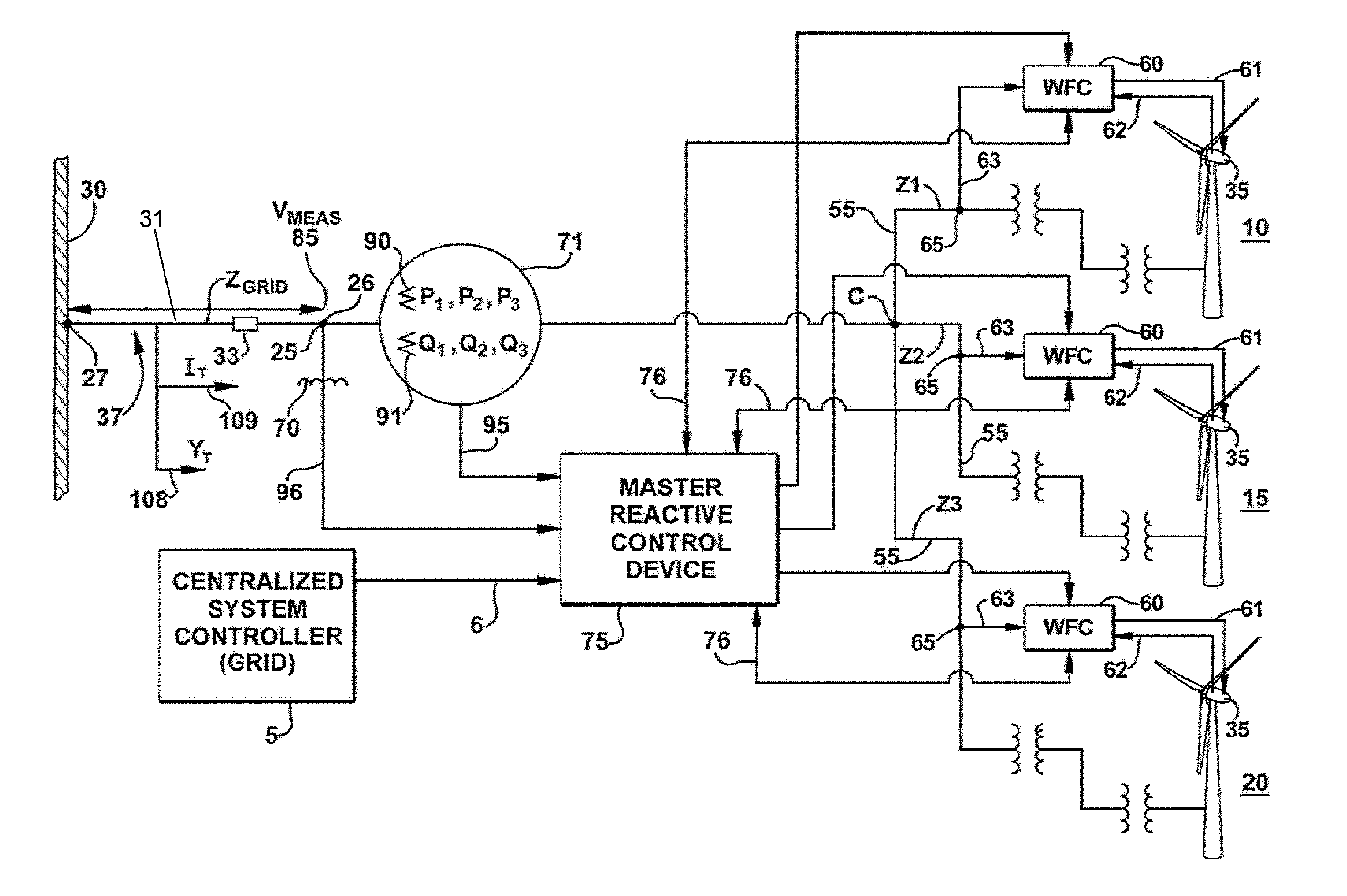

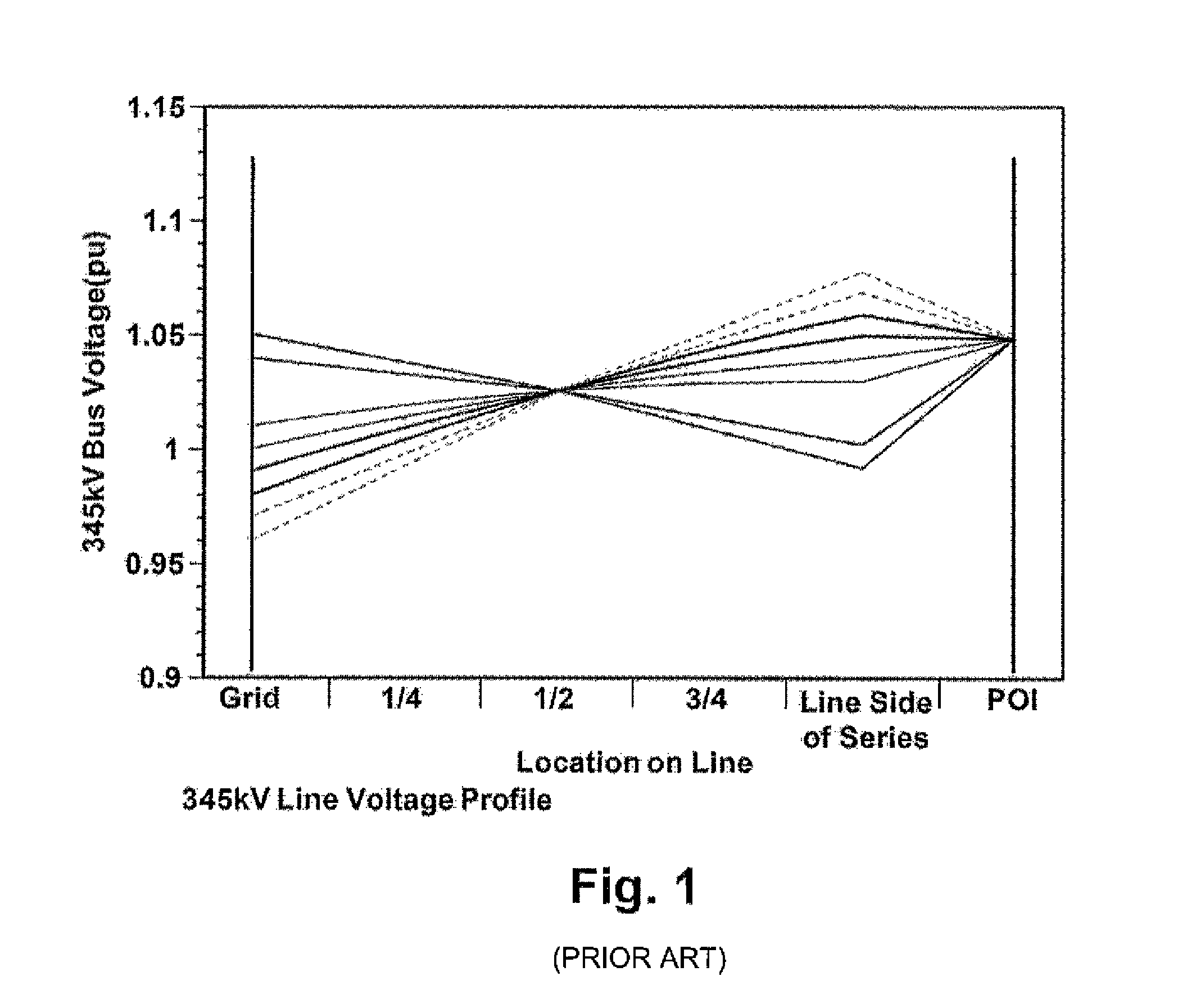

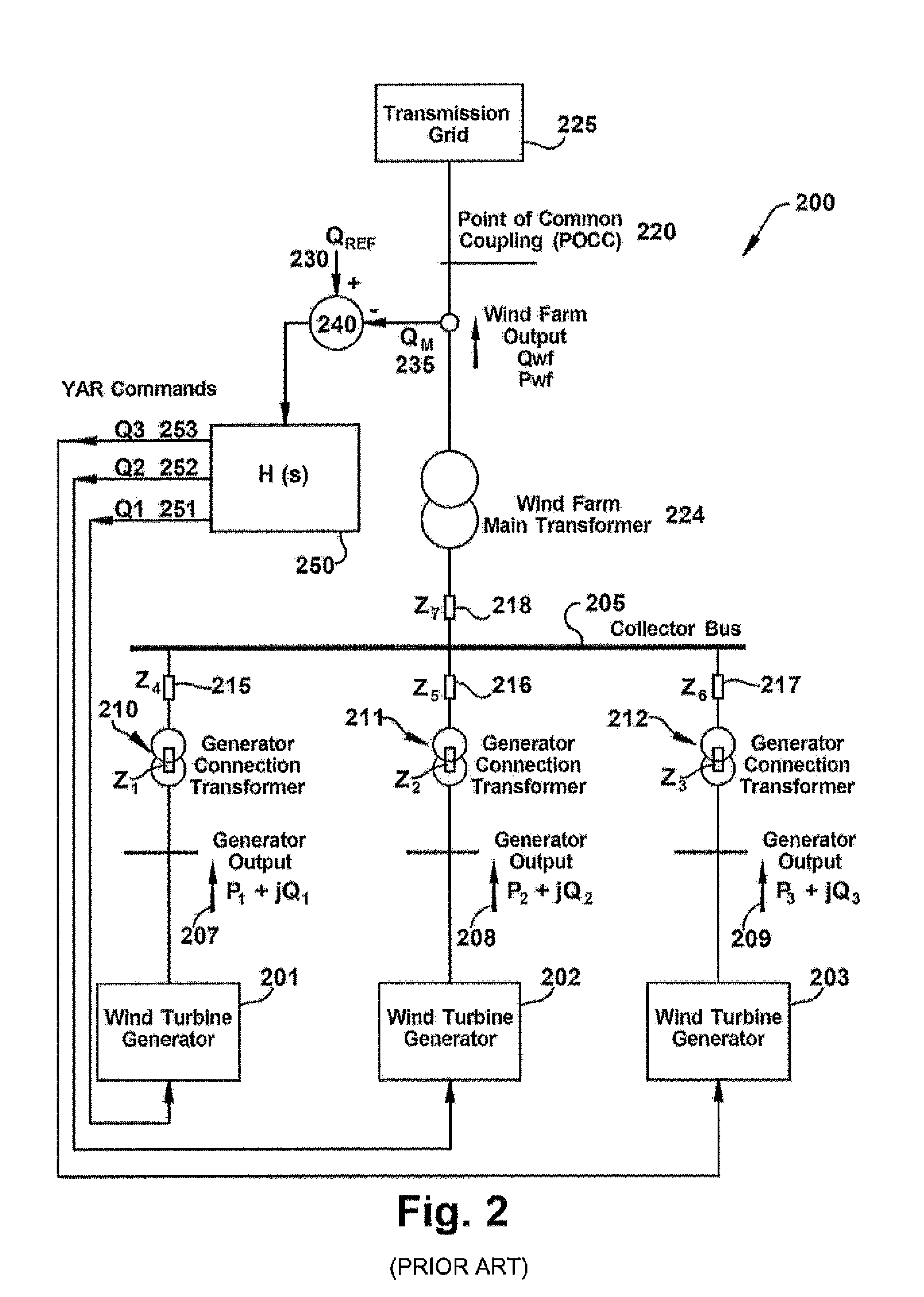

Voltage control at windfarms

A voltage control arrangement for a system of multiple windfarms with transmission lines. Voltage is regulated at a point of regulation on the system, such as a high voltage substation or other system bus. Regulation is achieved at the point of regulation by sensing the voltage, comparing to a reference voltage, and adjusting the reactive power output of the wind turbines and other equipment in the system. The regulation point may be shifted to another point if needed to respect voltage limits at that points of the system after attempting to shift reactive load to restore voltage within limits at the other points in the system. The reference voltage may be adjusted to minimize losses for the system of multiple windfarms and transmission lines. A loss optimizing algorithm is applied to the combined multiple windfarm and transmission line to shift reactive load among local windfarms to minimize losses and to shift reactive load among individual wind turbines within an individual windfarm.

Owner:GENERAL ELECTRIC CO

Method for calculating power capability of battery packs using advanced cell model predictive techniques

ActiveUS7321220B2Batteries circuit arrangementsMaterial analysis by electric/magnetic meansPower capabilityEngineering

The present invention relates to a method and an apparatus for estimating discharge and charge power of battery applications, including battery packs used in Hybrid Electric Vehicles (HEV) and Electric Vehicles (EV). One charge / discharge power estimating method incorporates voltage, state-of-charge (SOC), power, and current design constraints and works for a user-specified prediction time horizon Δt. At least two cell models are used in calculating maximum charge / discharge power based on voltage limits. The first is a simple cell model that uses a Taylor-series expansion to linearize the equation involved. The second is a more complex and accurate model that models cell dynamics in discrete-time state-space form. The cell model can incorporate a inputs such as temperature, resistance, capacity, etc. One advantage of using model-based approach is that the same model may be used in both Kalman-filtering to produce the SOC and the estimation of maximum charge / discharge current based on voltage limits.

Owner:LG ENERGY SOLUTION LTD

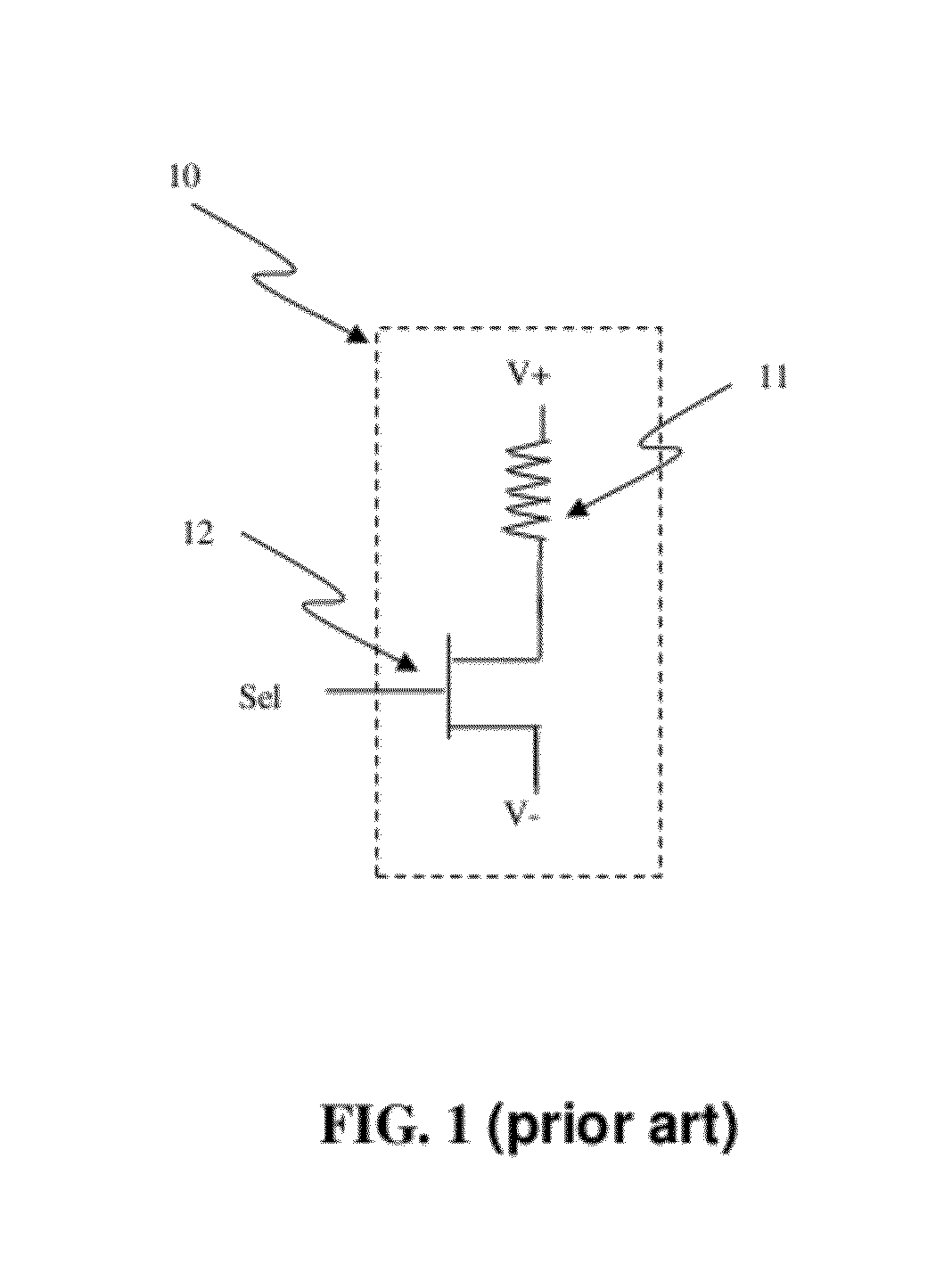

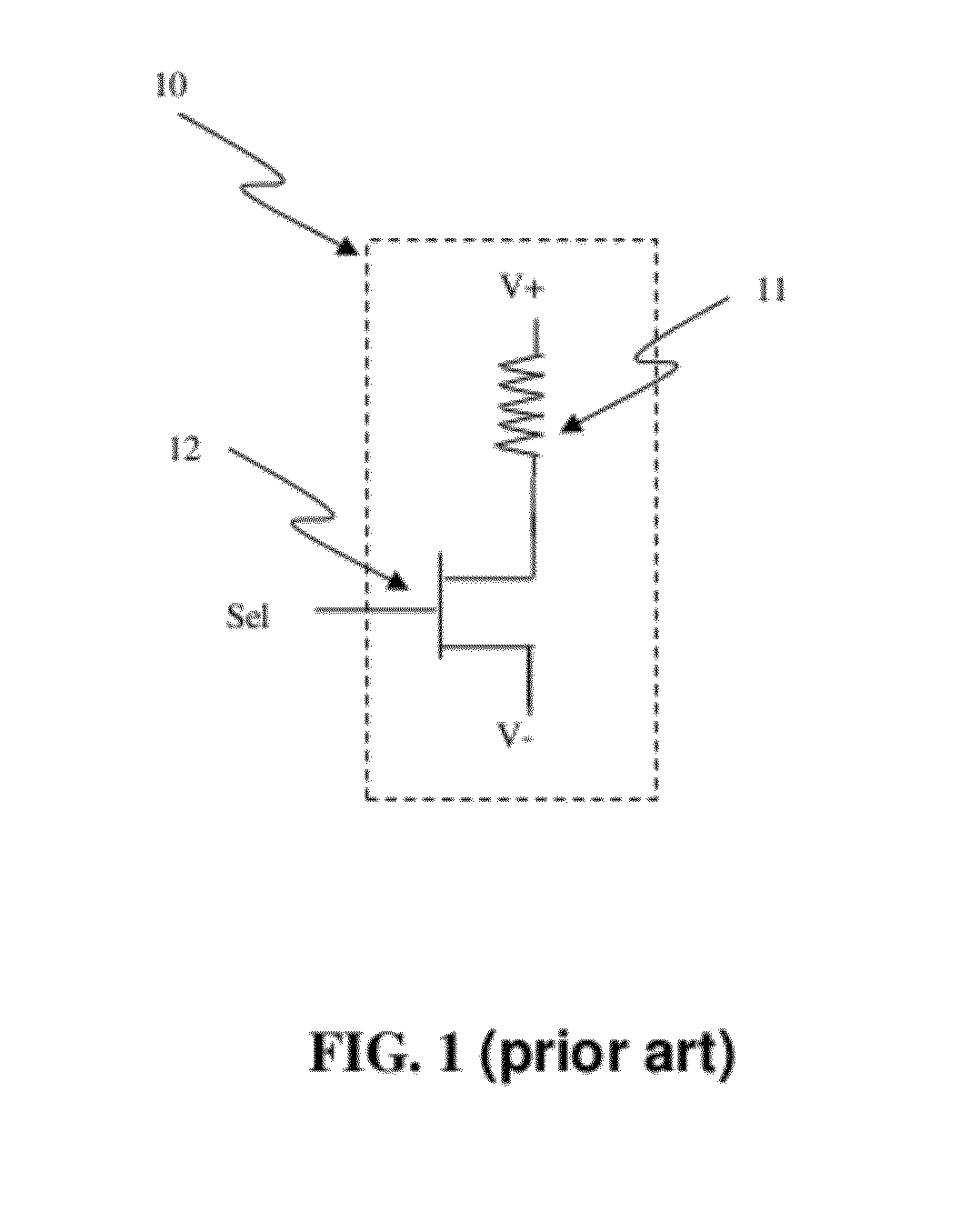

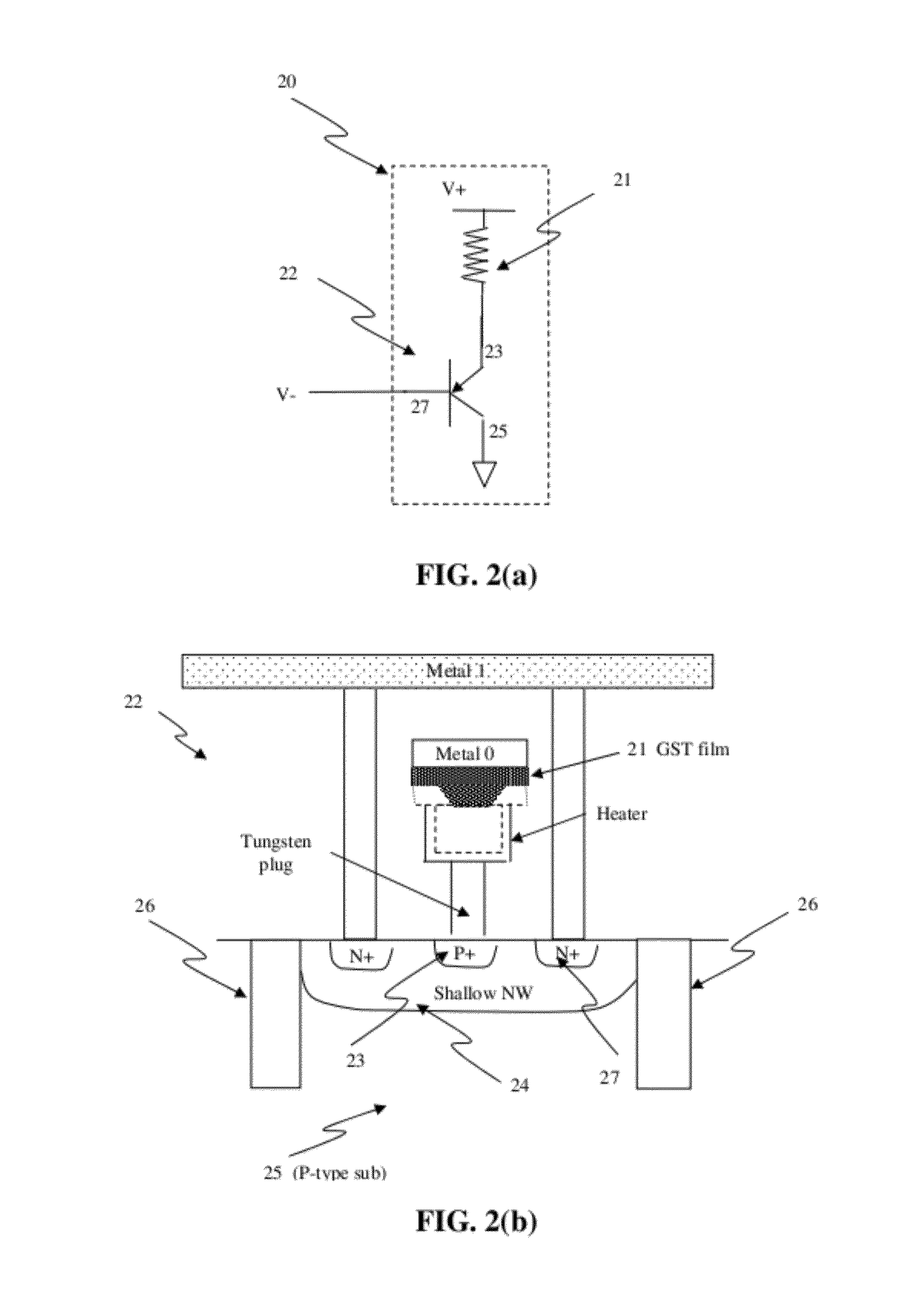

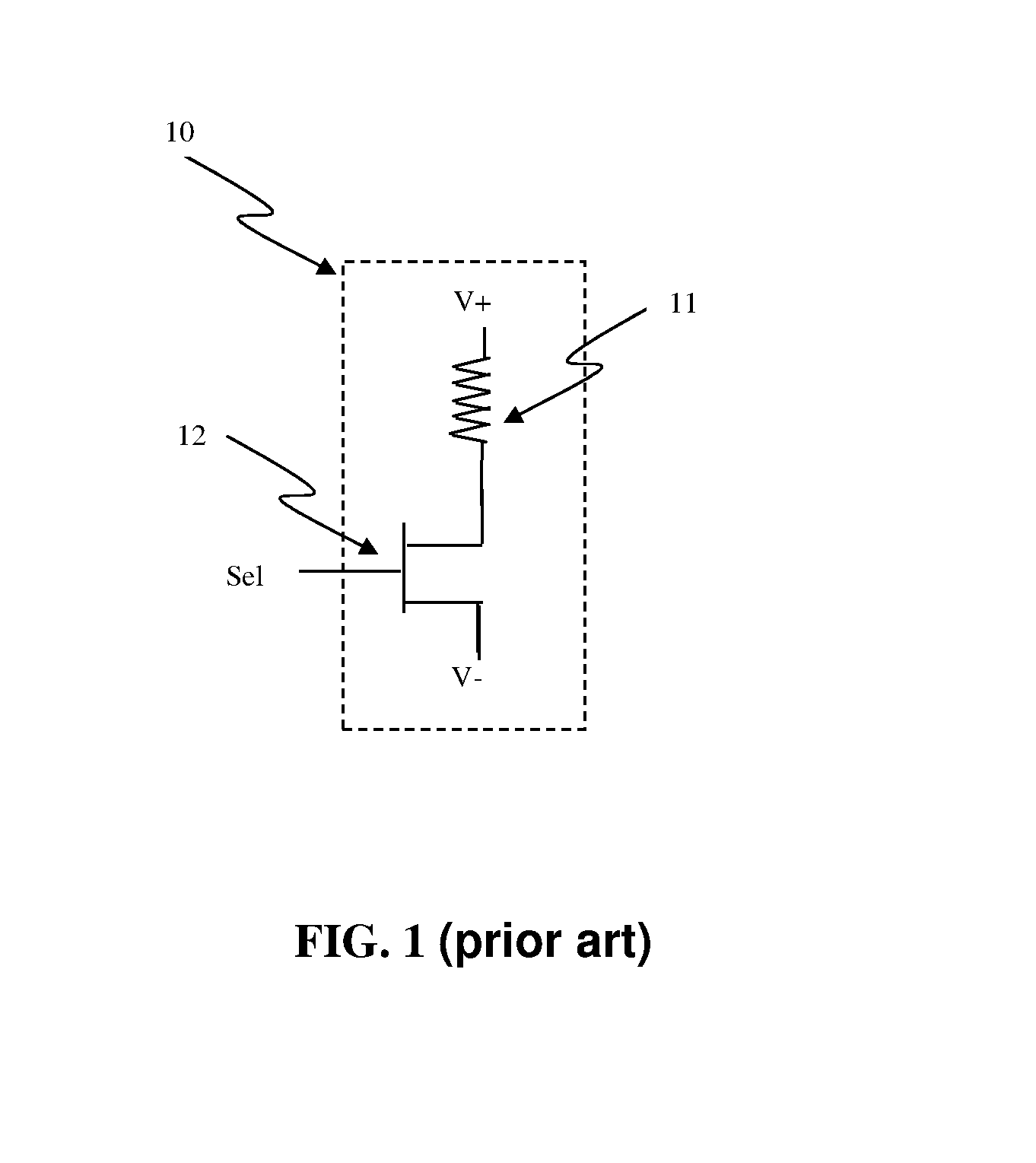

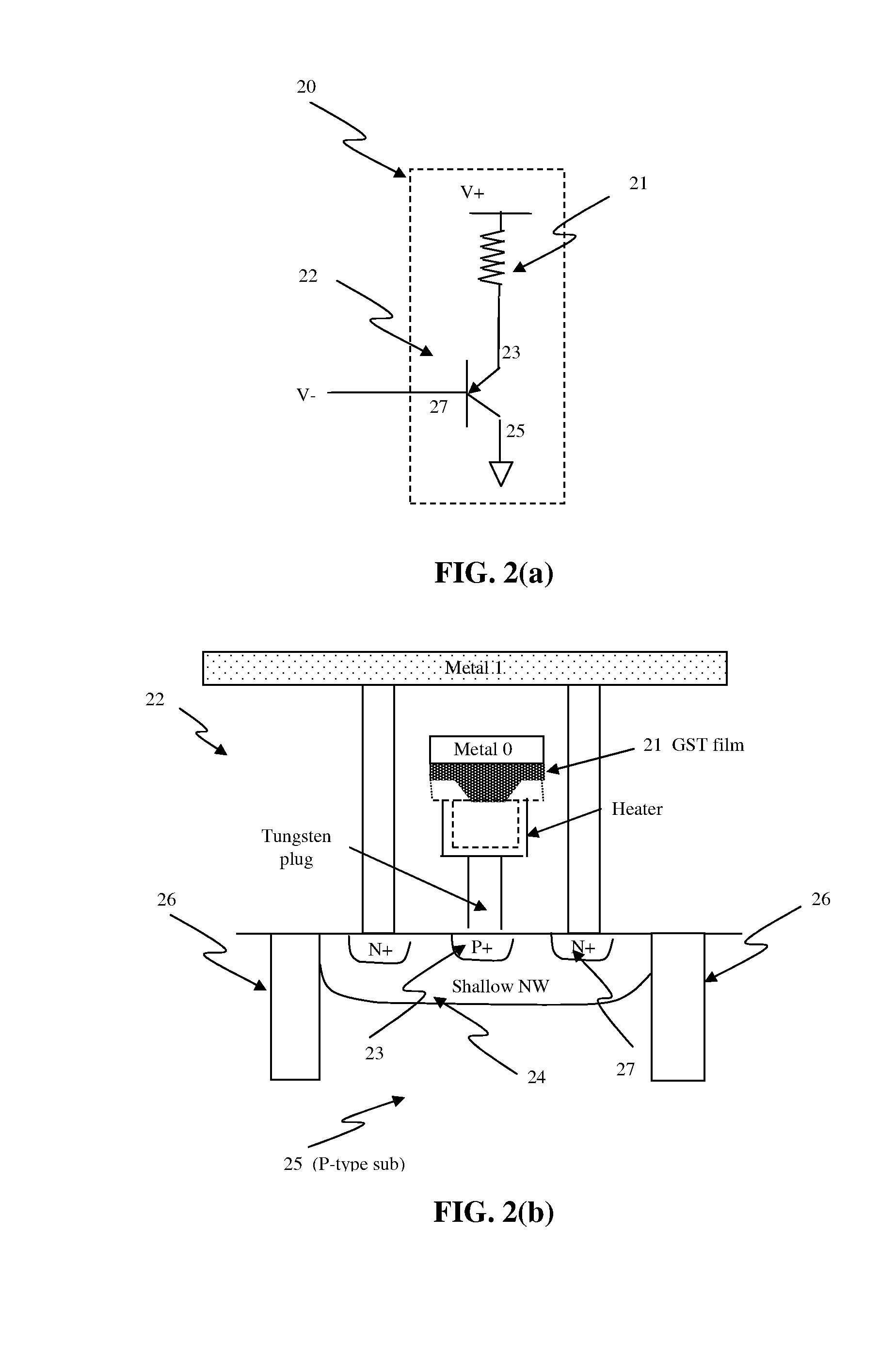

Reversible resistive memory using diodes formed in CMOS processes as program selectors

ActiveUS20120044747A1Small cell sizeLow costSolid-state devicesRead-only memoriesCMOSElectrical resistance and conductance

Junction diodes fabricated in standard CMOS logic processes can be used as program selectors for reversible resistive memory cells that can be programmed based on magnitude, duration, voltage-limit, or current-limit of a supply voltage or current. These cells are PCM, RRAM, CBRAM, or other memory cells that have a reversible resistive element coupled to a diode. The diode can be constructed by P+ and N+ active regions on an N well as the P and N terminals of the diode. The memory cells can be used to construct a two-dimensional memory array with the N terminals of the diodes in a row connected as a wordline and the reversible resistive elements in a column connected as a bitline. By applying a voltage or a current to a selected bitline and to a selected wordline to turn on the diode, a selected cell can be programmed into different states reversibly based on magnitude, duration, voltage-limit, or current-limit. The data in the reversible resistive memory can also be read by turning on a selected wordline to couple a selected bitline to a sense amplifier. The wordlines may have high-resistivity local wordlines coupled to low-resistive global wordlines through conductive contact(s) or via(s).

Owner:ATTOPSEMI TECH CO LTD

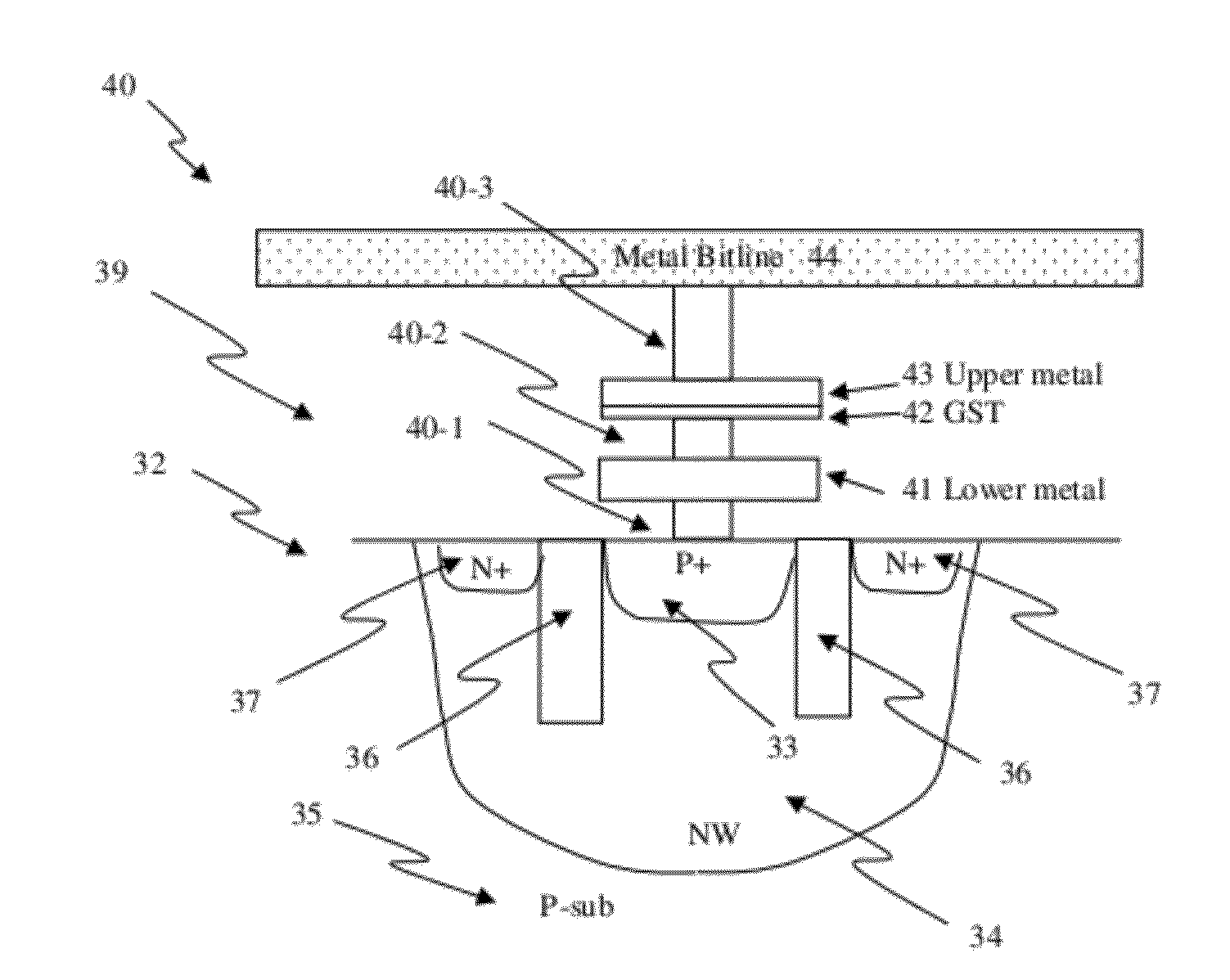

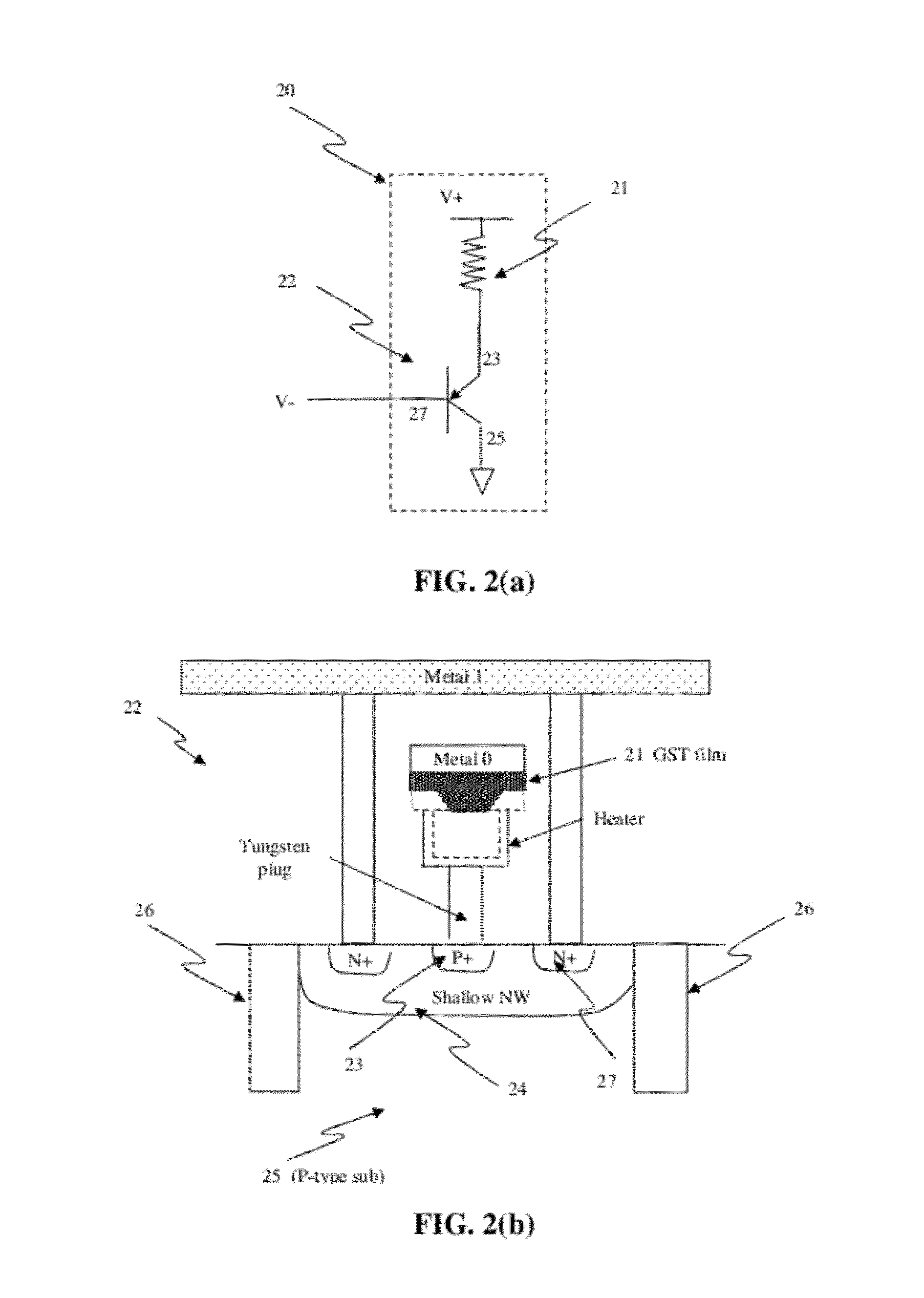

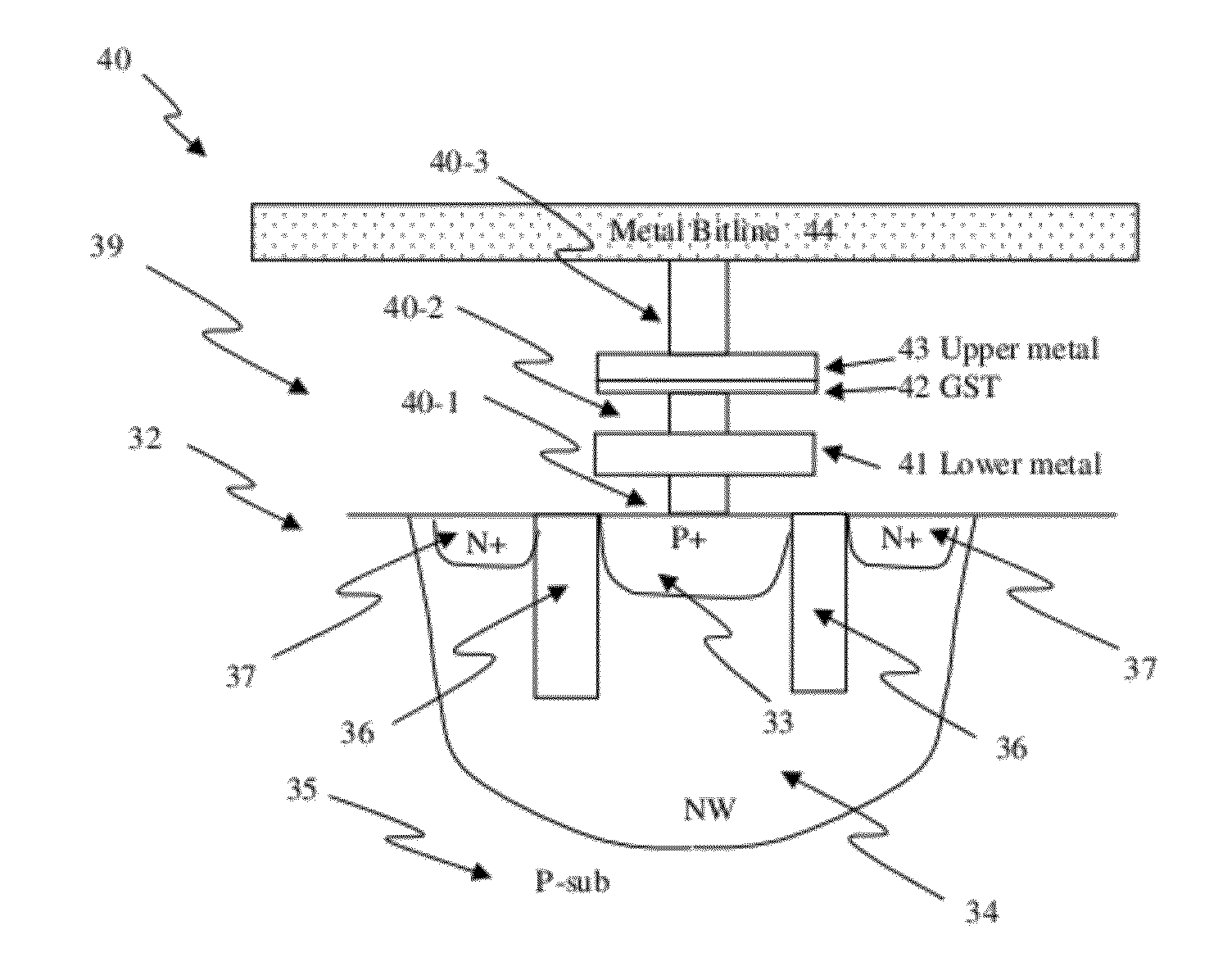

Programmably reversible resistive device cells using CMOS logic processes

ActiveUS20120044753A1Small cell sizeLow costSolid-state devicesRead-only memoriesCMOSCurrent limiting

Junction diodes fabricated in standard CMOS logic processes can be used as program selectors for reversible resistive devices, such as PCM, RRAM, CBRAM, or other memory cells. The reversible resistive devices have a reversible resistive element coupled to a diode. The diode can be constructed by P+ and N+ active regions on an N well as the P and N terminals of the diode. By applying a voltage or a current between a reversible resistive element and the N terminal of a diode, the reversible resistive device can be programmed into different states based on magnitude, duration, voltage-limit, or current-limit in a reversible manner. The P+ active region of the diode can be isolated from the N+ active region in the N well by using dummy MOS gate, SBL, or STI / LOCOS isolations.

Owner:ATTOPSEMI TECH CO LTD

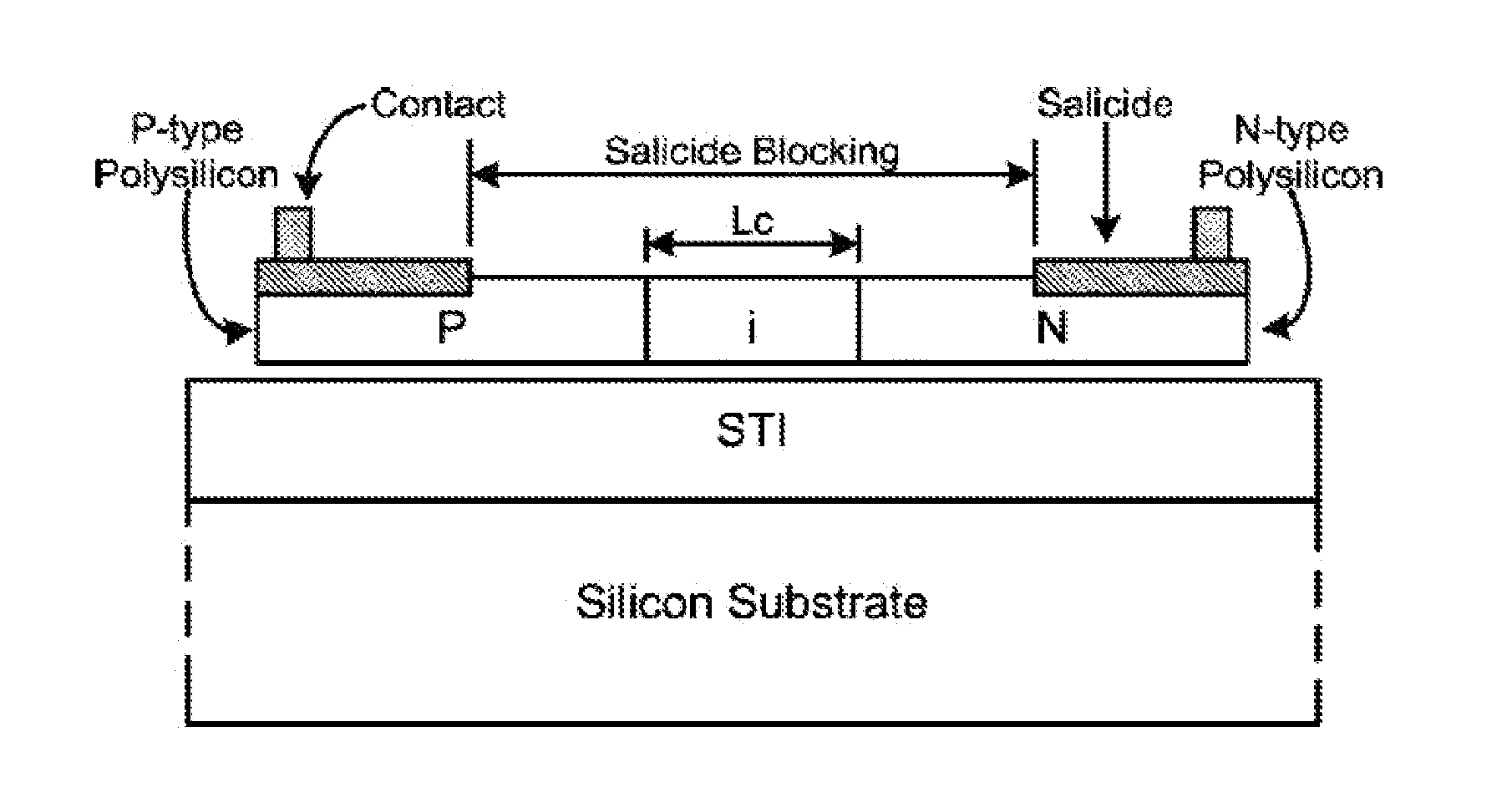

Programmably reversible resistive device cells using polysilicon diodes

ActiveUS20120044744A1Change resistanceSolid-state devicesRead-only memoriesEngineeringBlocking layer

Polysilicon diodes fabricated in standard CMOS logic processes can be used as program selectors for reversible resistive devices such as PCRAM, RRAM, CBRAM, or other memory cells. The reversible resistive devices have a reversible resistive element coupled to a diode. The diode can be constructed by P+ / N+ implants on a polysilicon as a program selector. By applying a voltage or a current between a reversible resistive element and the N-terminal of a diode, the reversible resistive device can be programmed into different states based on magnitude, duration, voltage-limit, or current-limit in a reversible manner. On the polysilicon diode, the spacing and doping level of a gap between the P- and N-implants can be controlled for different breakdown voltages and leakage currents. The Silicide Block Layer (SBL) can be used to block silicide formation on the top of polysilicon to prevent shorting.

Owner:ATTOPSEMI TECH CO LTD

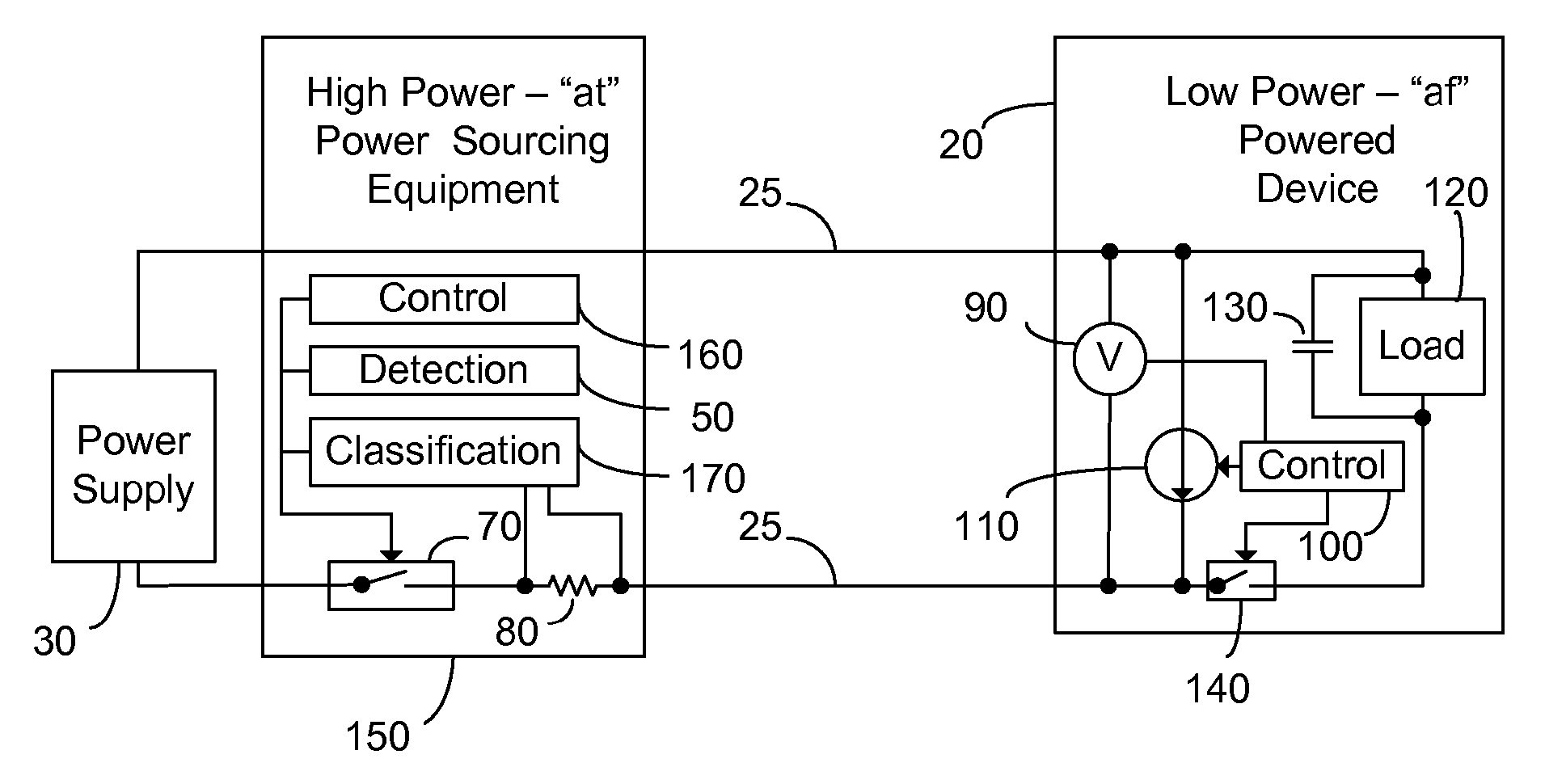

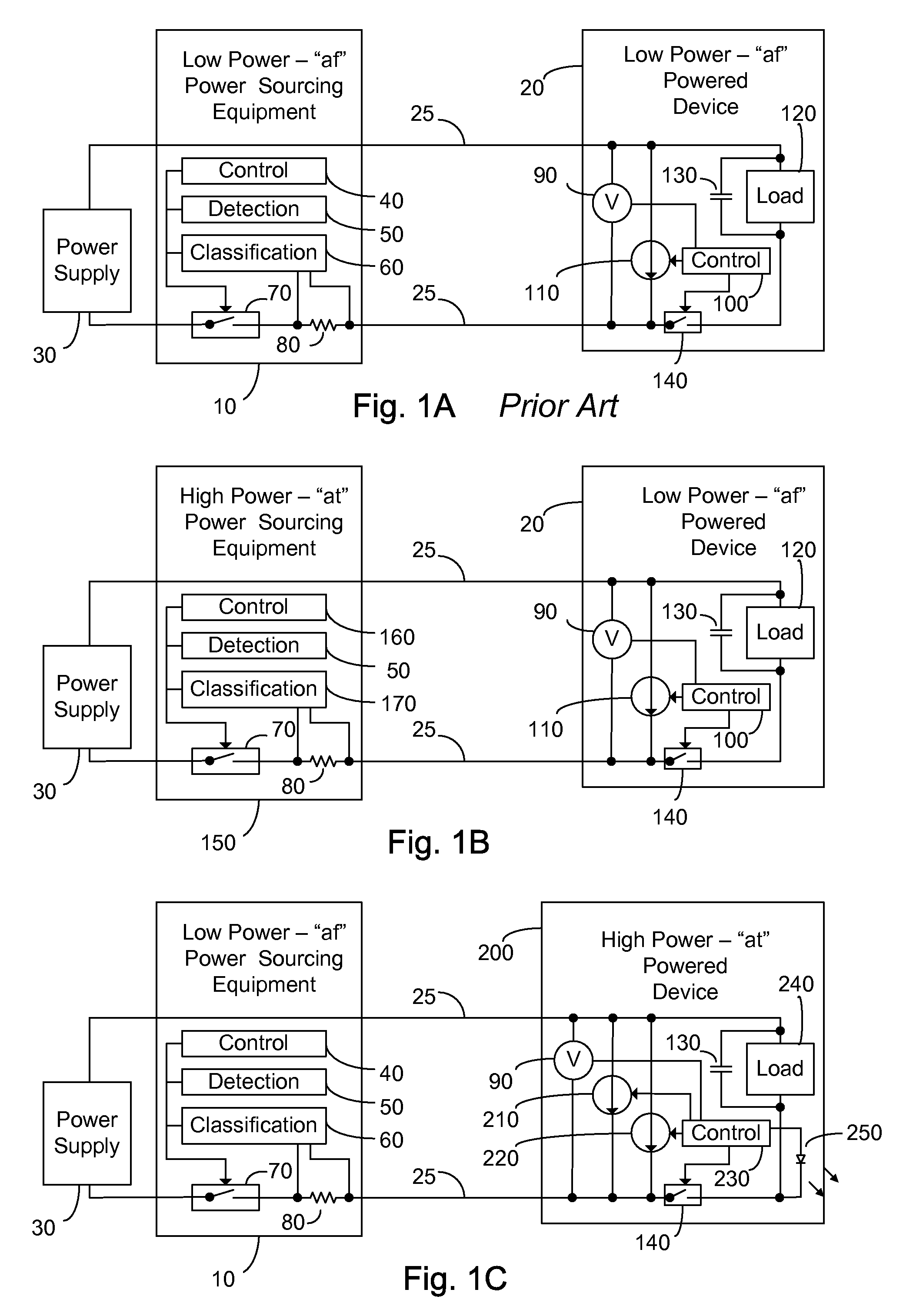

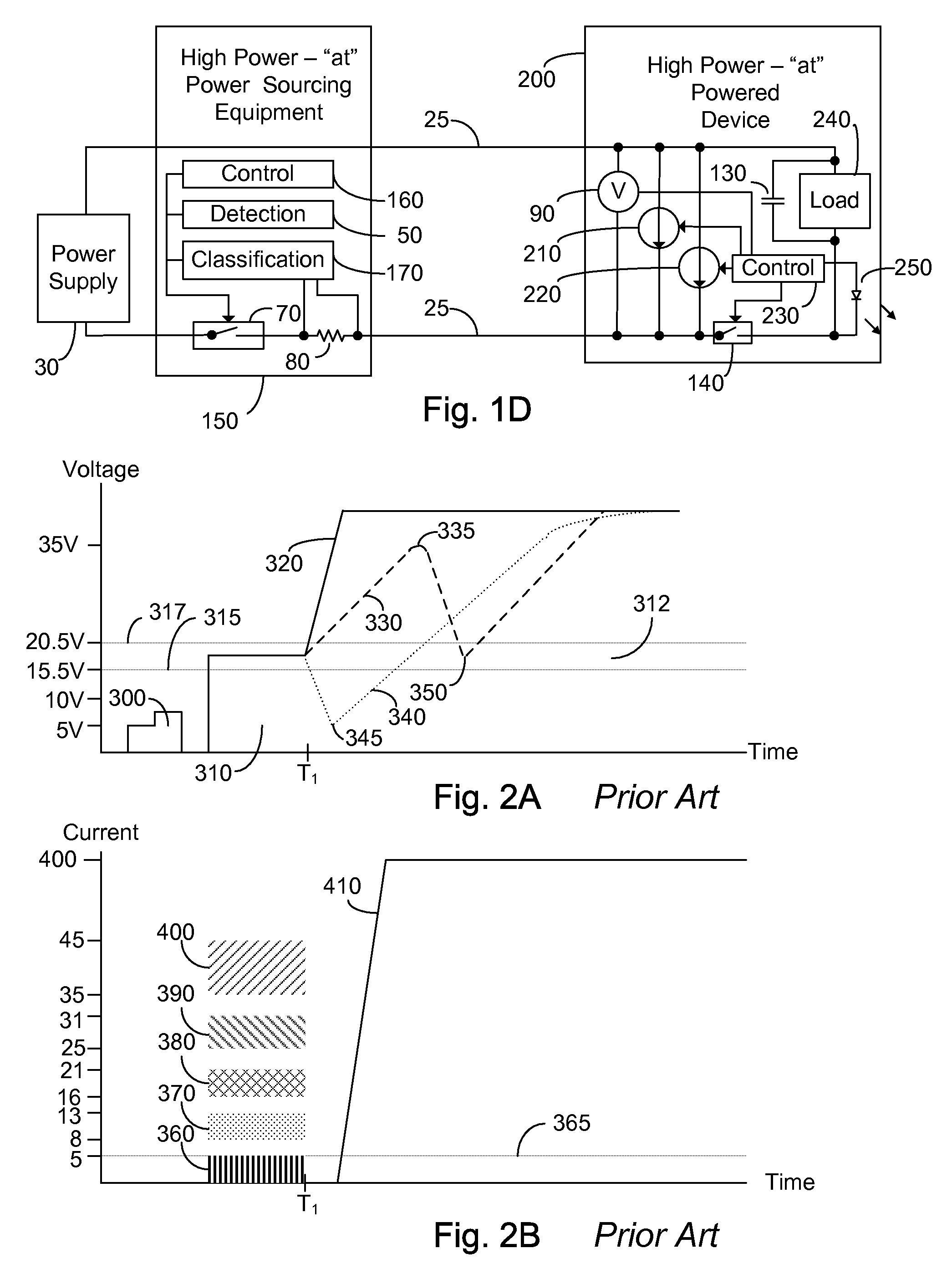

Enhanced Classification for Power Over Ethernet

InactiveUS20070103829A1Overcome disadvantagesCurrent/voltage measurementPower supply for data processingEngineeringVoltage range

A method of classification of power requirements in a power over Ethernet system, the method comprising: providing a first classification voltage for a first classification cycle time, the provided first classification voltage being within a classification voltage range defined by a lower classification voltage limit and upper classification voltage limit; measuring a first current flow responsive to the provided first classification voltage; subsequent to the first classification cycle time, providing a voltage outside of the classification voltage range for a classification indexing time; subsequent to the classification indexing time, providing a second classification voltage for a second classification cycle time, the provided second classification voltage being within the classification voltage range; measuring a second current flow responsive to the provided second classification voltage; determining a classification responsive to the measured first current flow and the measured second current flow; and allocating power responsive to the determined classification.

Owner:NEVERMORE SOLUTIONS

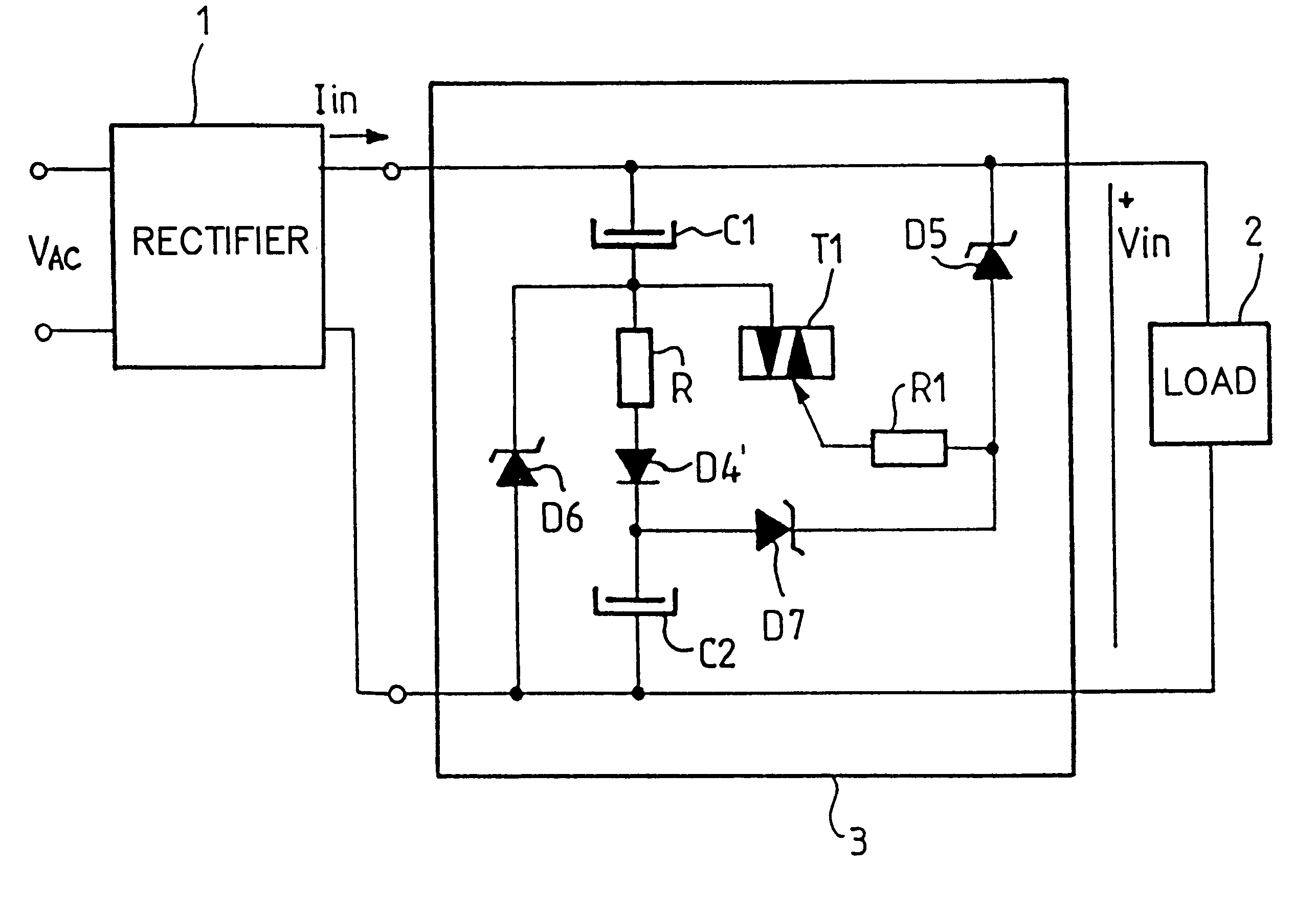

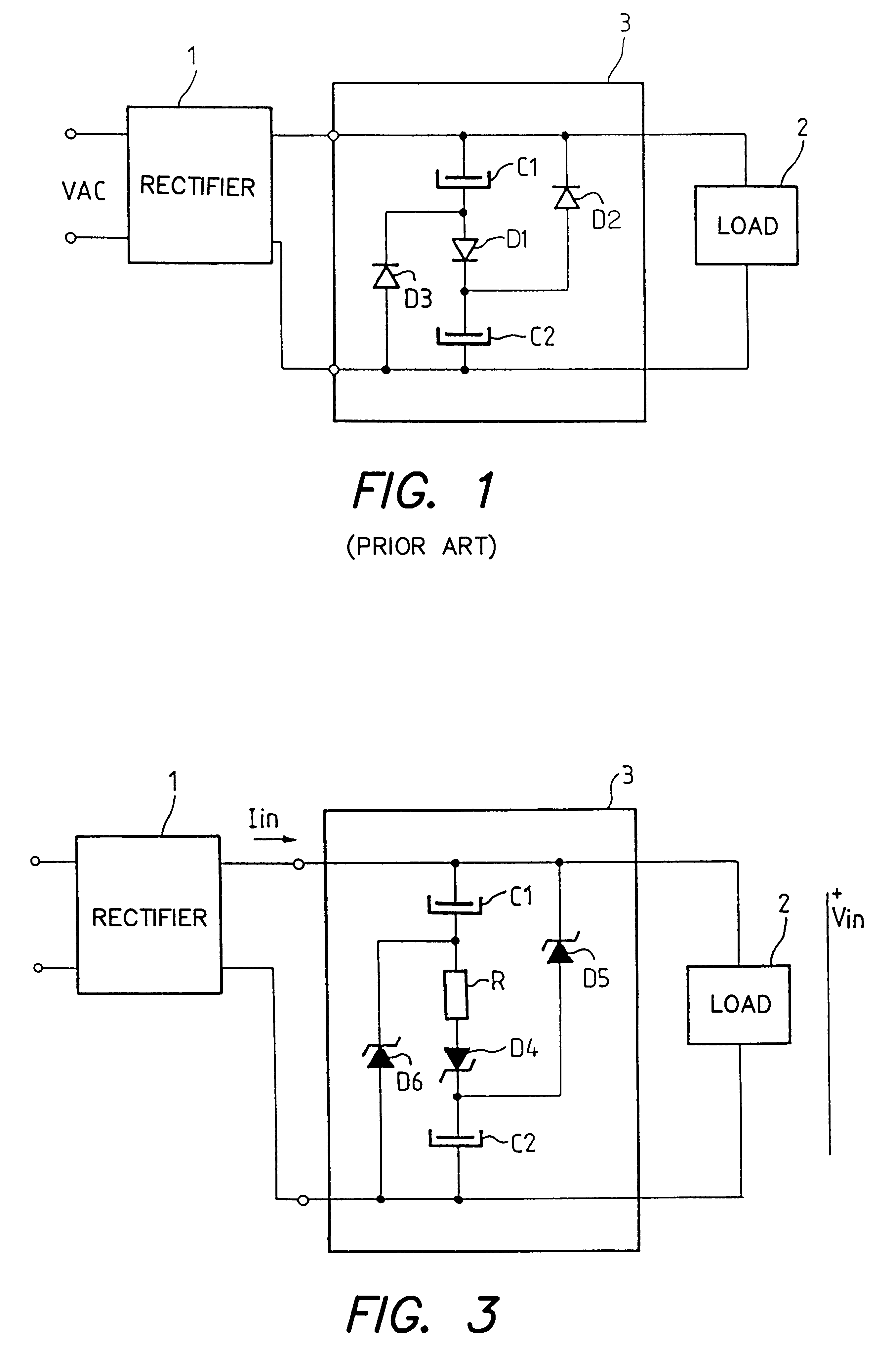

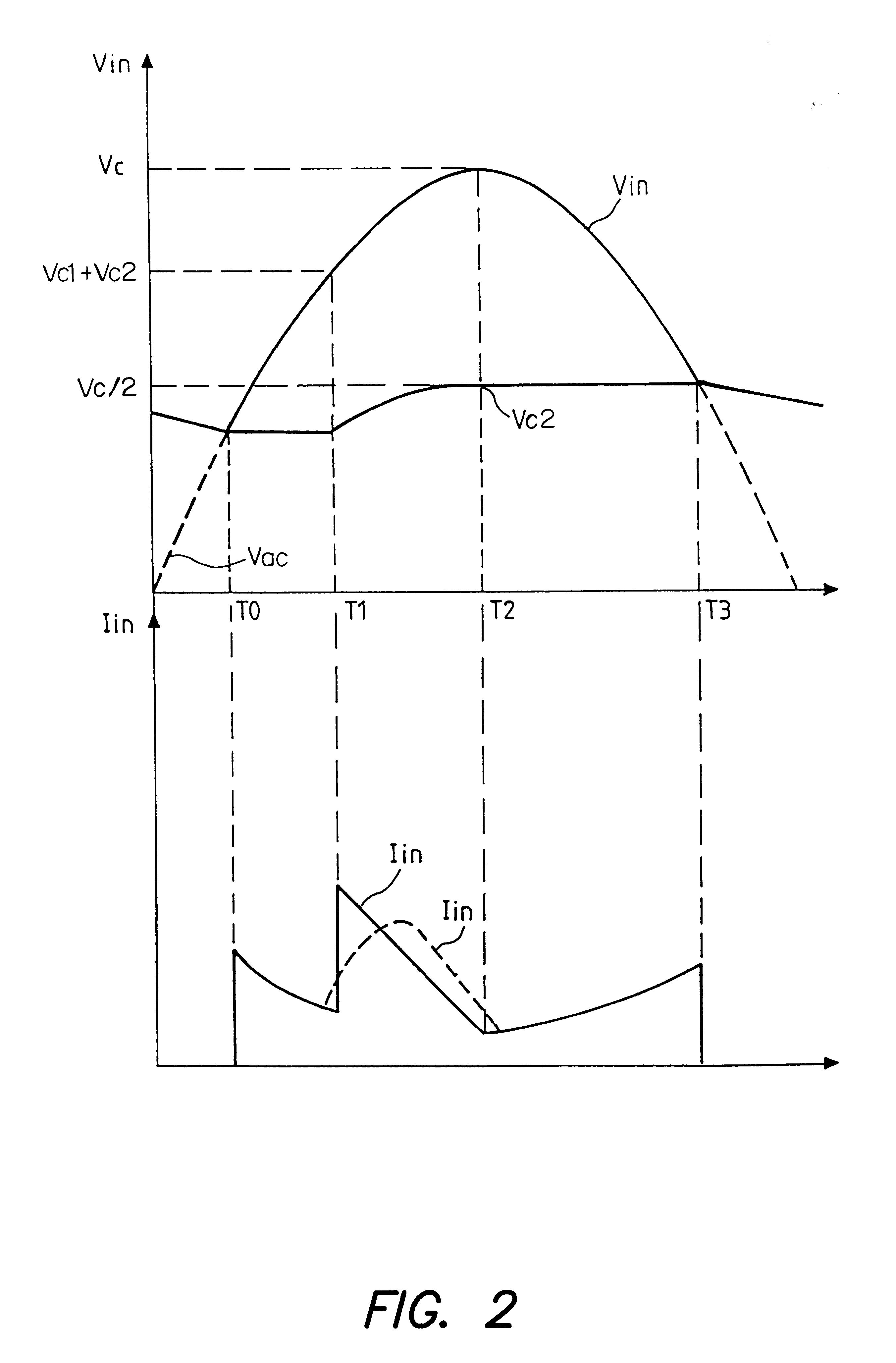

Electronic power supply device

InactiveUS6219263B1Efficient power electronics conversionAc-dc conversionOvervoltageElectronic switch

A power factor correction circuit using a first rectifier diode to control the series charging of two capacitors and two rectifier diodes to control the parallel discharging of the two capacitors. The power factor correction circuit further includes a resistor that is series-connected with the first diode to improve the power factor and to reduce the current drawn when the voltage is turned on. The rectifier diodes are advantageously voltage limiting diodes to protect the downline circuitry against overvoltages. In one improvement, a current-controlled electronic switch is used for protection against overvoltages that are just above the peak value of the line voltage.

Owner:STMICROELECTRONICS SRL

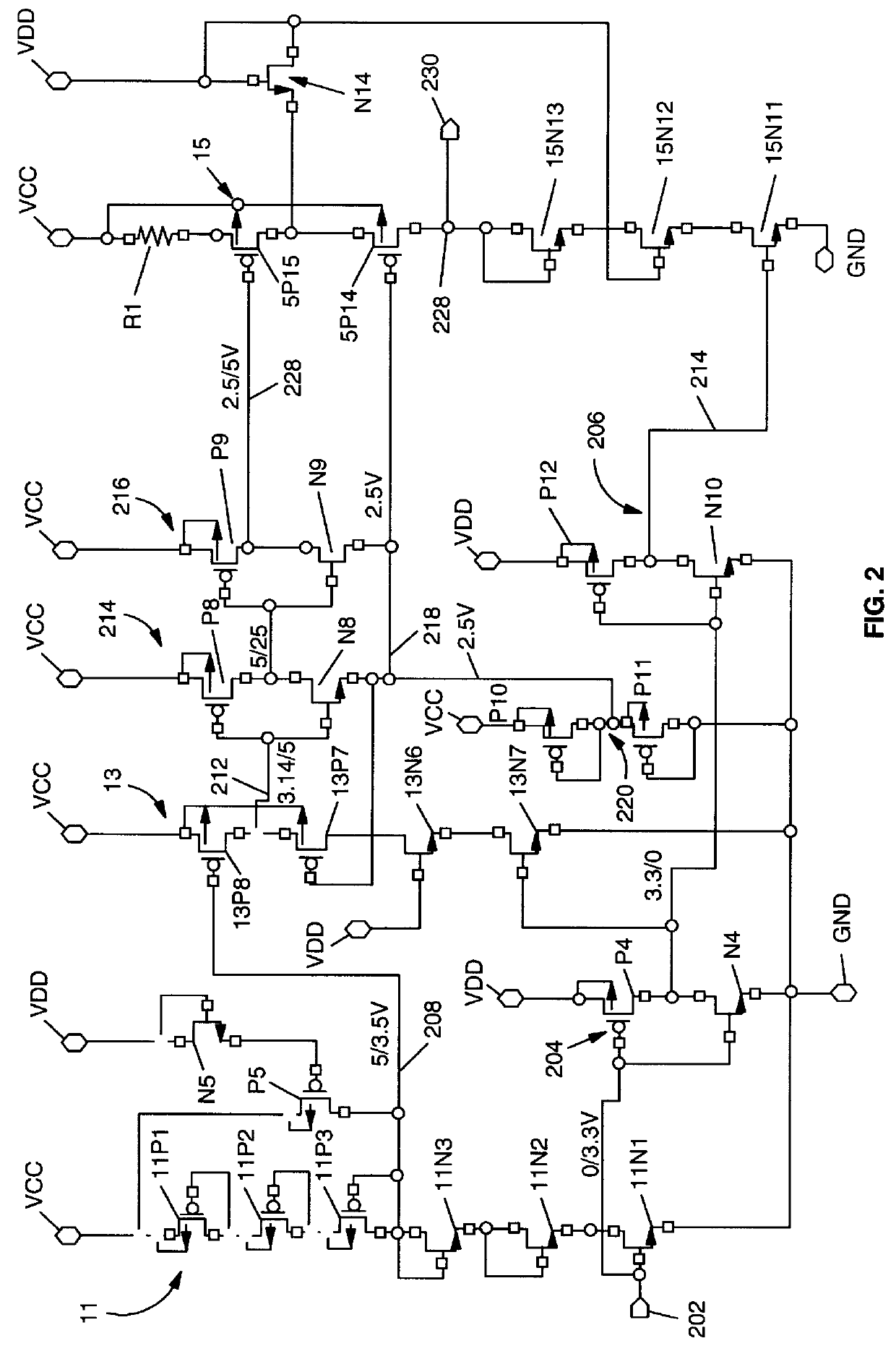

Driver for switch and a method of driving the same

ActiveUS20080018366A1TransistorAmplifier with semiconductor-devices/discharge-tubesPower switchingEngineering

A driver for a switch, a related method of driving the switch, and a power converter employing the same. In one embodiment, the driver includes switching circuitry having a driver switch referenced to a voltage level and configured to provide a drive signal to a control terminal of a power switch referenced to another voltage level and subject to a control voltage limit. The driver also includes a comparator configured to change a state of the driver switch when a voltage at the control terminal passes a threshold voltage.

Owner:INTEL CORP

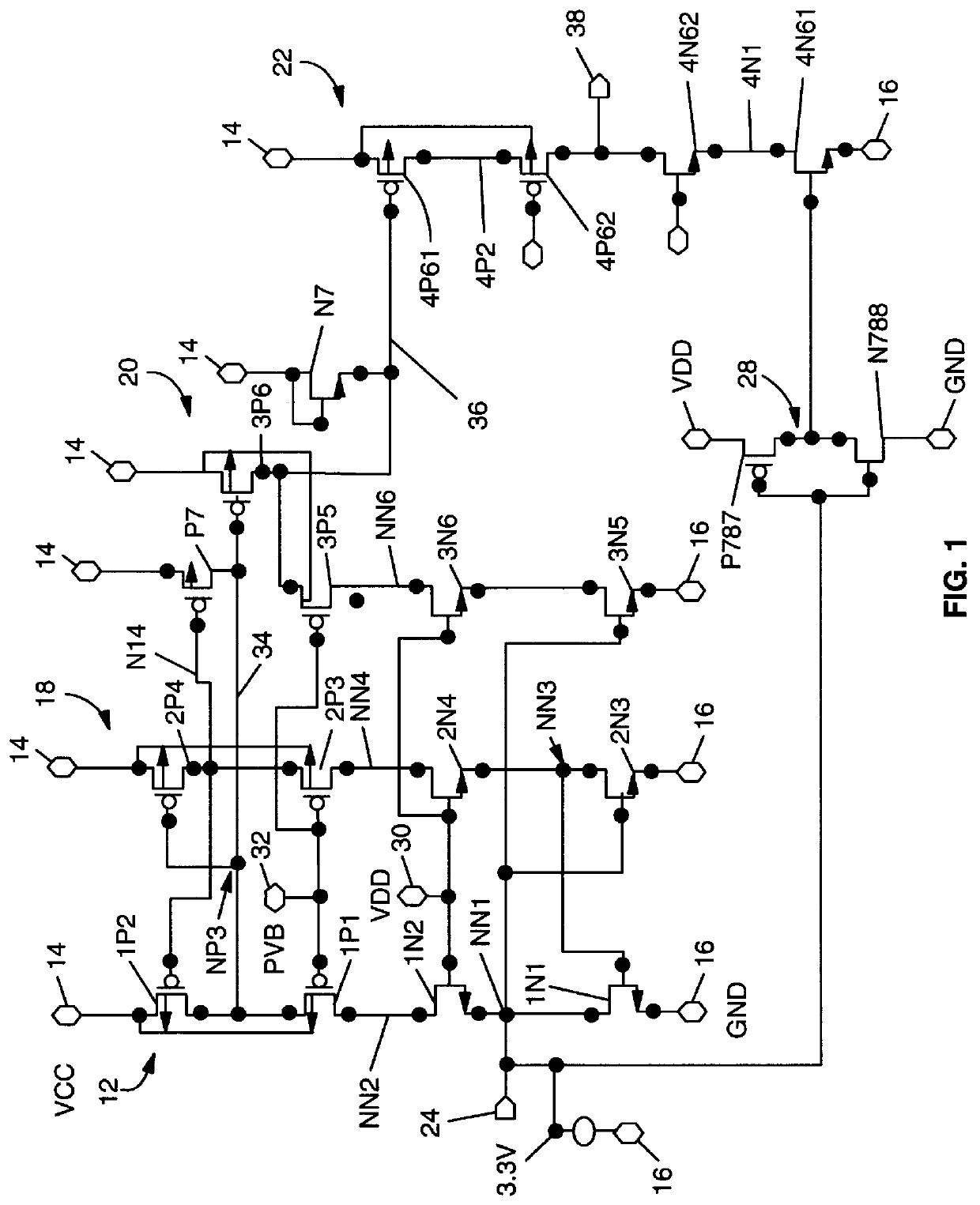

Low voltage CMOS circuit for on/off chip drive at high voltage

InactiveUS6031394AAvoid failureReliability increasing modificationsLogic circuits characterised by logic functionCMOSCascode

A low voltage CMOS circuit and method provide output current ability meeting multimode requirements of high voltage off-chip drivers while protecting the CMOS devices from various breakdown mechanisms. The circuit and method utilize intermediate voltages between two power rails and voltage division techniques to limit the voltages to acceptable limits for drain-to-source, gate-to-drain, and gate-to-source of CMOS devices in any chosen technology. The circuit comprises first and second CMOS cascode chains connected between a high voltage power rail, e.g 5 volt and a reference potential power rail, e.g. ground. Each CMOS cascode chain comprises first and second p-type MOS devices in series with first and second n-type MOS devices. An input circuit is coupled to a node at the midpoint of the first CMOS cascode chain. A bias voltage, typically 3.3 volts is connected to the NMOS devices in the first and CMOS cascode chains. A second bias voltage is coupled to the PMOS devices in the first and second CMOS cascode chains. An output is provided from the second CMOS cascode chain to a third CMOS cascode chain for purposes of providing sufficient pullup capability to drive an output circuit comprising a fourth CMOS cascode chain between the high and reference potentials without exceeding the breakdown mechanisms for any MOS device in the CMOS cascode chains.

Owner:GOOGLE LLC

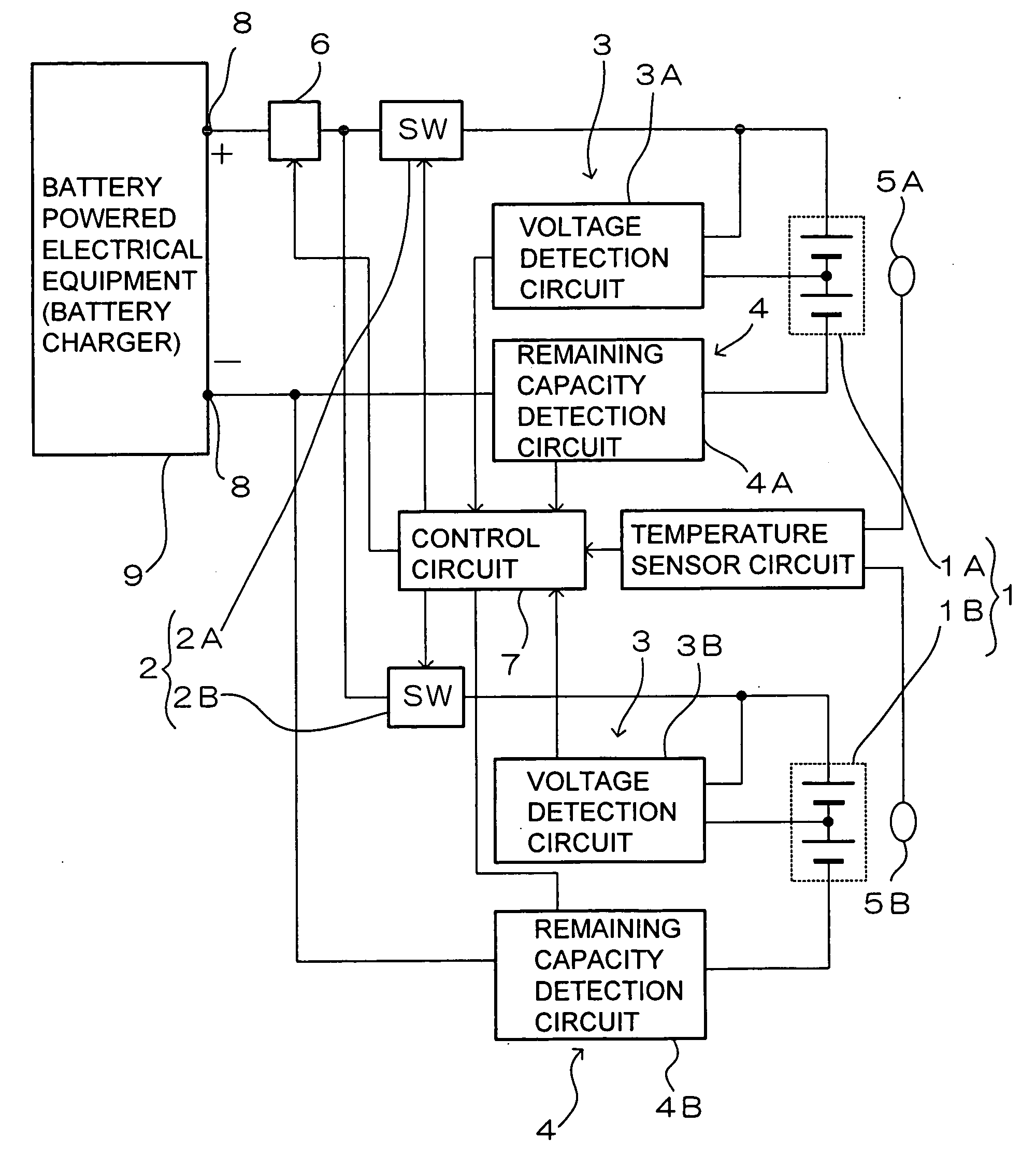

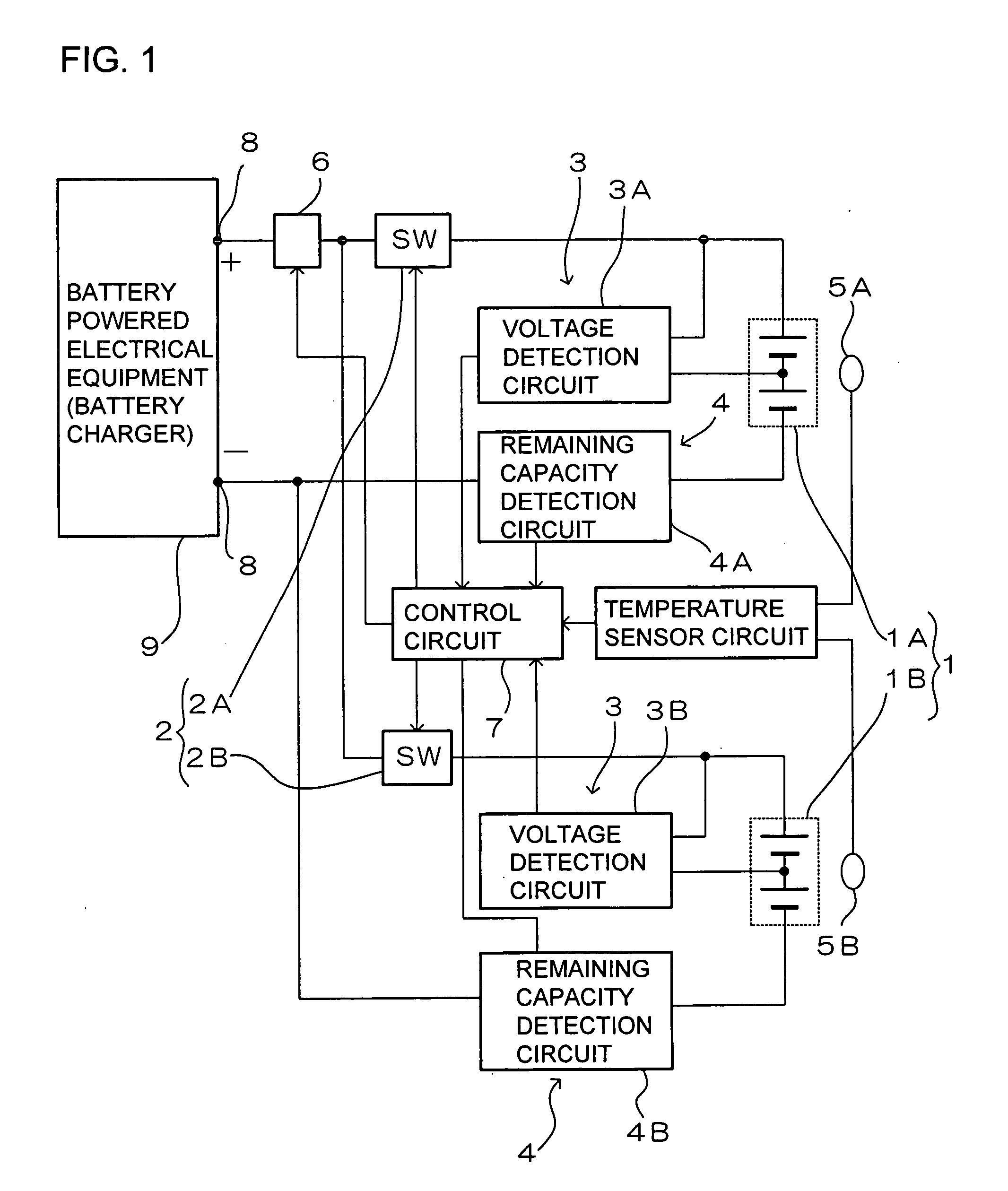

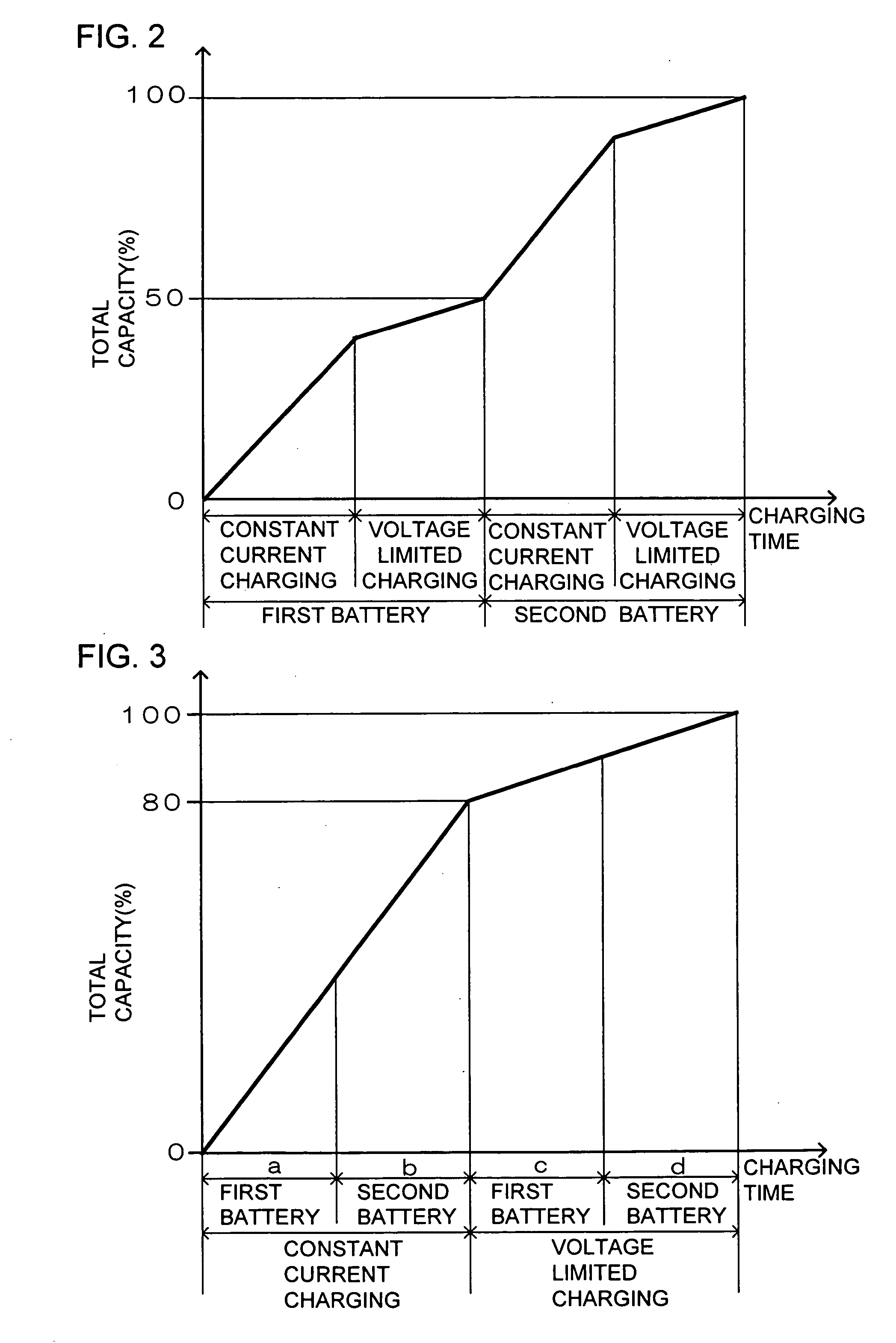

Method of charging and discharging a plurality of batteries

InactiveUS20050001593A1Reduce battery capacityCharge equalisation circuitSequential battery dischargeElectrical devicesEngineering

Owner:SANYO ELECTRIC CO LTD

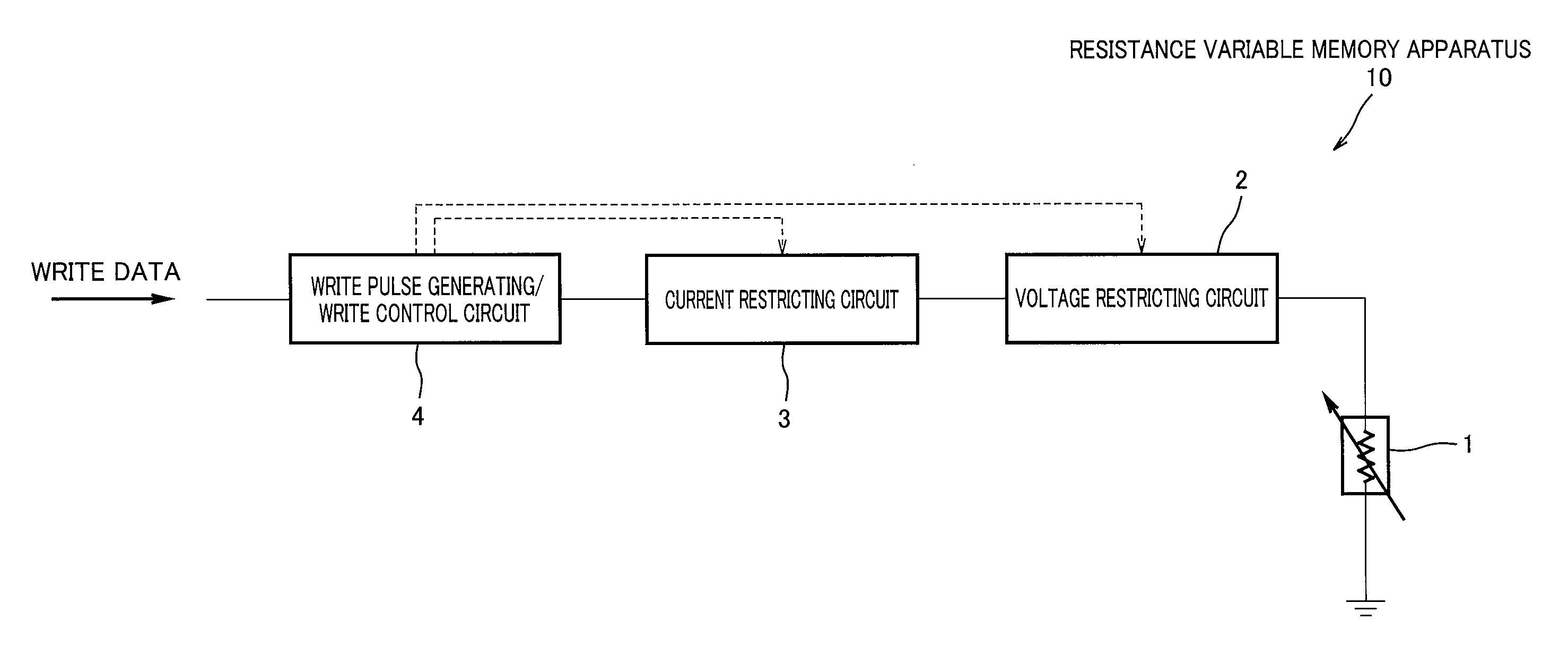

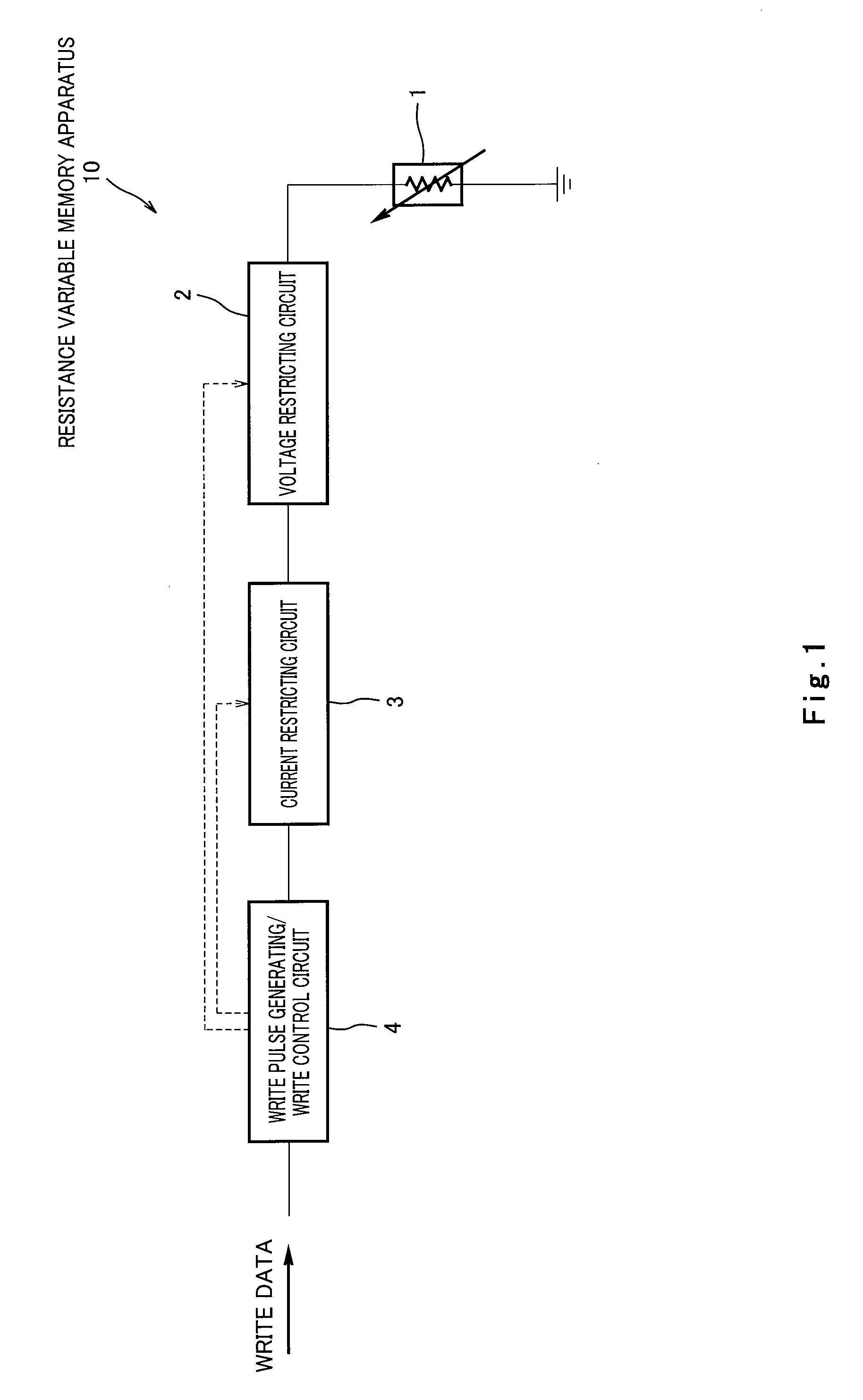

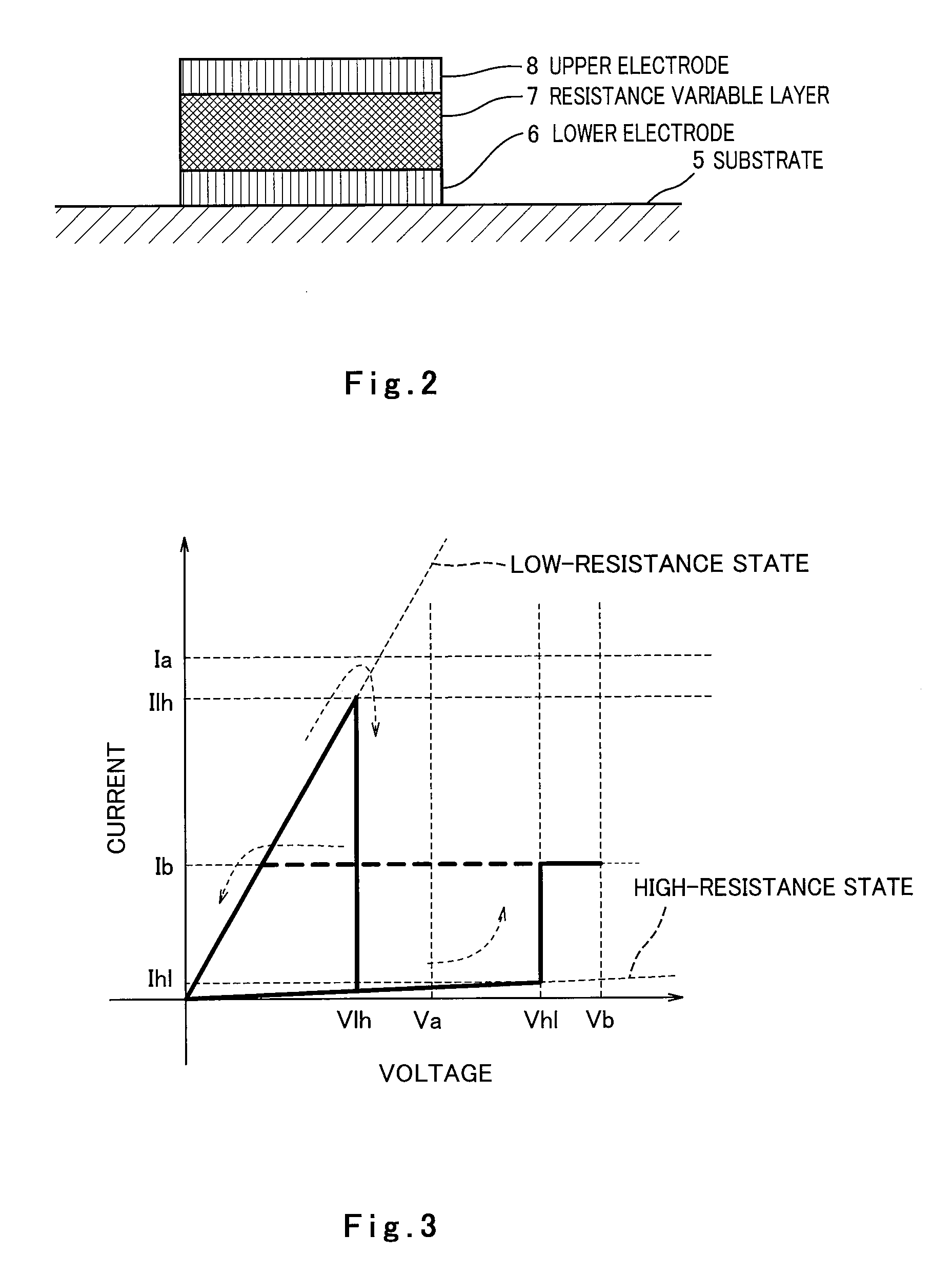

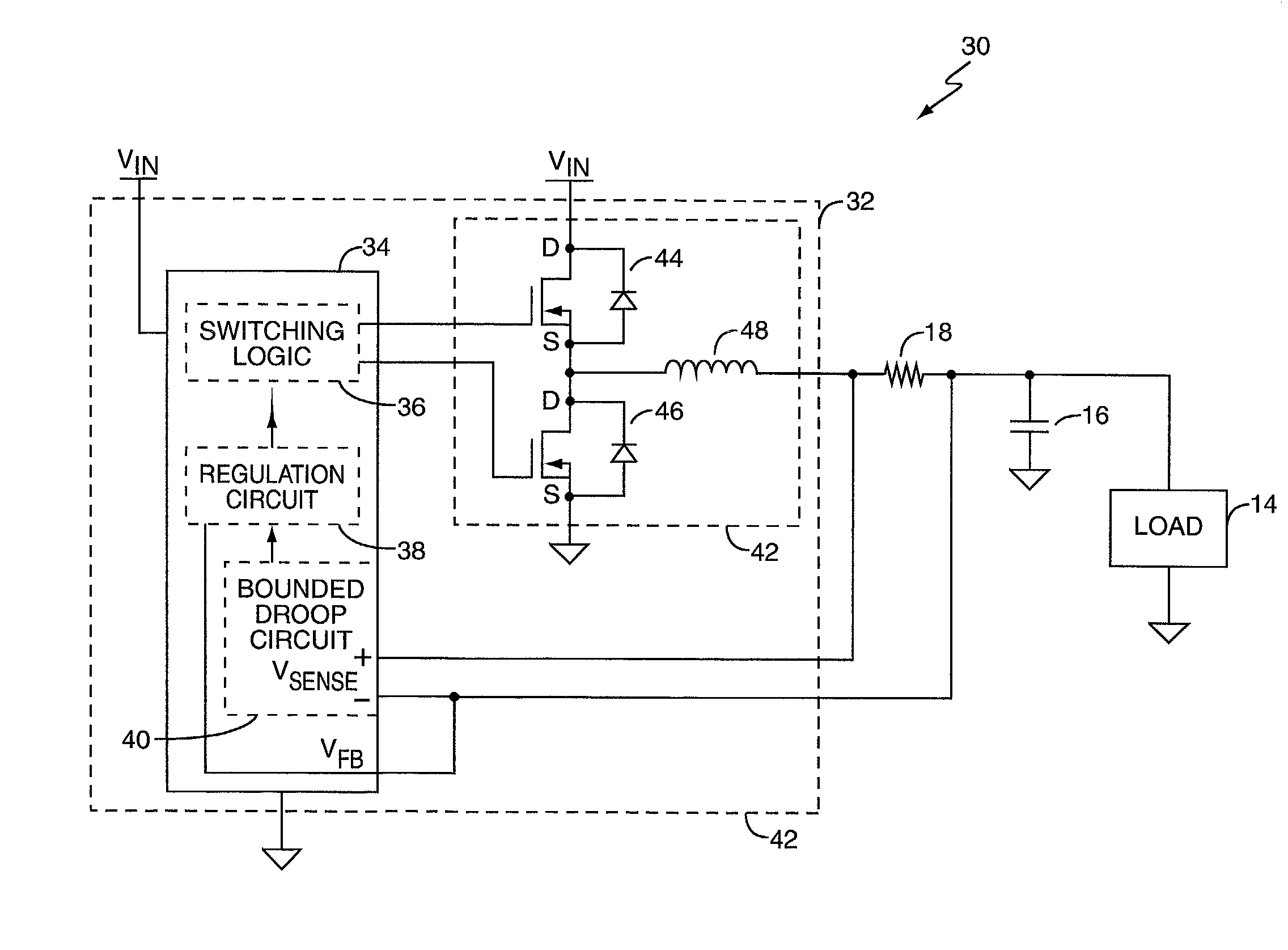

Resistance variable memory apparatus

ActiveUS20100110767A1Improper operationRead-only memoriesDigital storageHigh resistanceElectrical resistance and conductance

A resistance variable memory apparatus (10) of the present invention comprises a resistance variable element (1) which is switched to a high-resistance state when a voltage exceeds a first voltage and is switched to a low-resistance state when the voltage exceeds a second voltage, a controller (4), a voltage restricting active element (2) which is connected in series with the resistance variable element (1); and a current restricting active element which is connected in series with the resistance variable element (1) via the voltage restricting active element (2), and the controller (4) is configured to control the current restricting active element (3) so that a product of a current and a first resistance value becomes a first voltage or larger and to control the voltage restricting active element (2) so that the voltage between electrodes becomes smaller than a second voltage when the element is switched to the high-resistance state, while the controller (4) is configured to control the current restricting active element (3) so that an absolute value of a product of the current and the second resistance value becomes the second voltage or larger and an absolute value of a product of the current and the first resistance value becomes smaller than the first voltage, when the element is switched to the low-resistance state.

Owner:PANASONIC SEMICON SOLUTIONS CO LTD

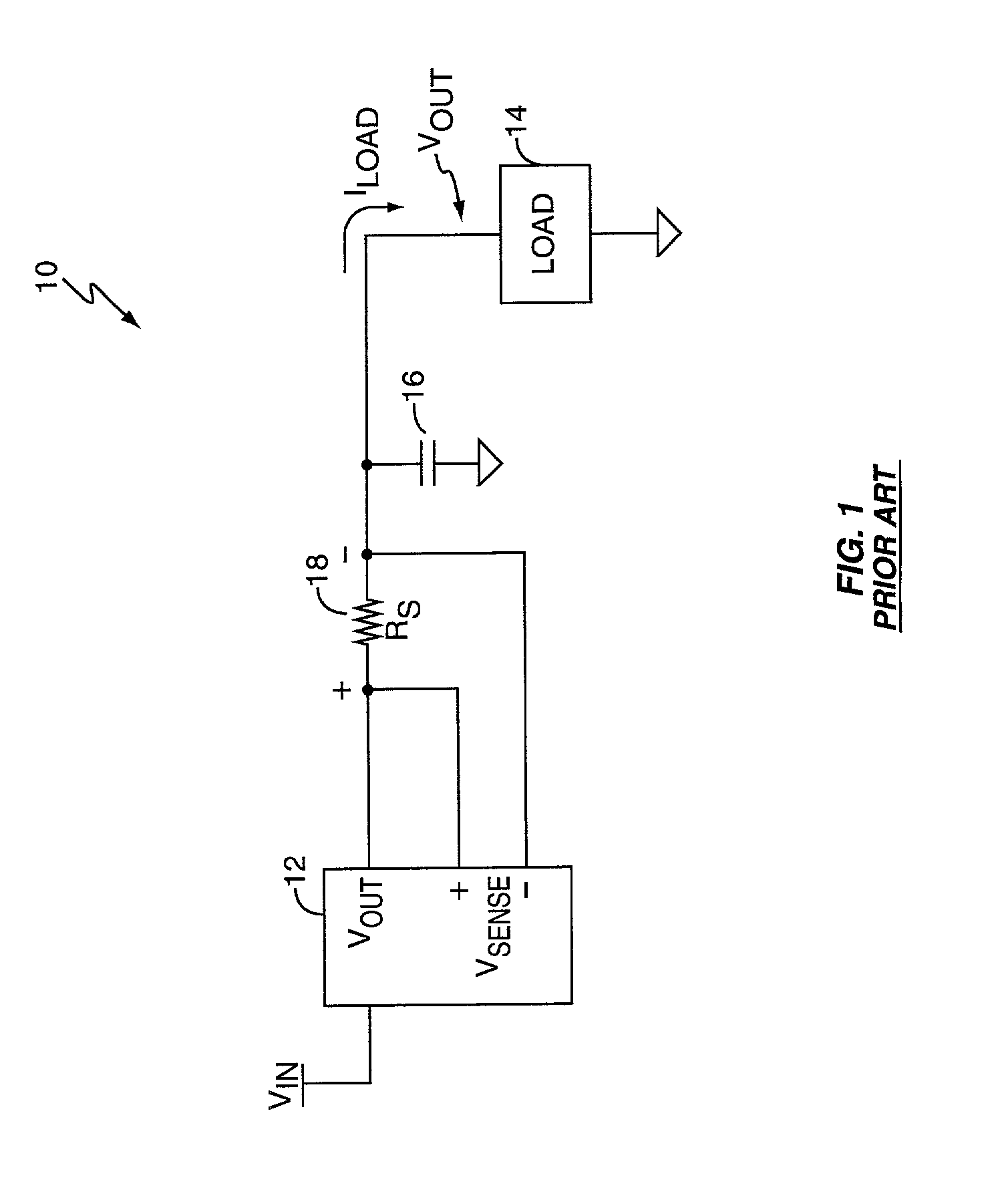

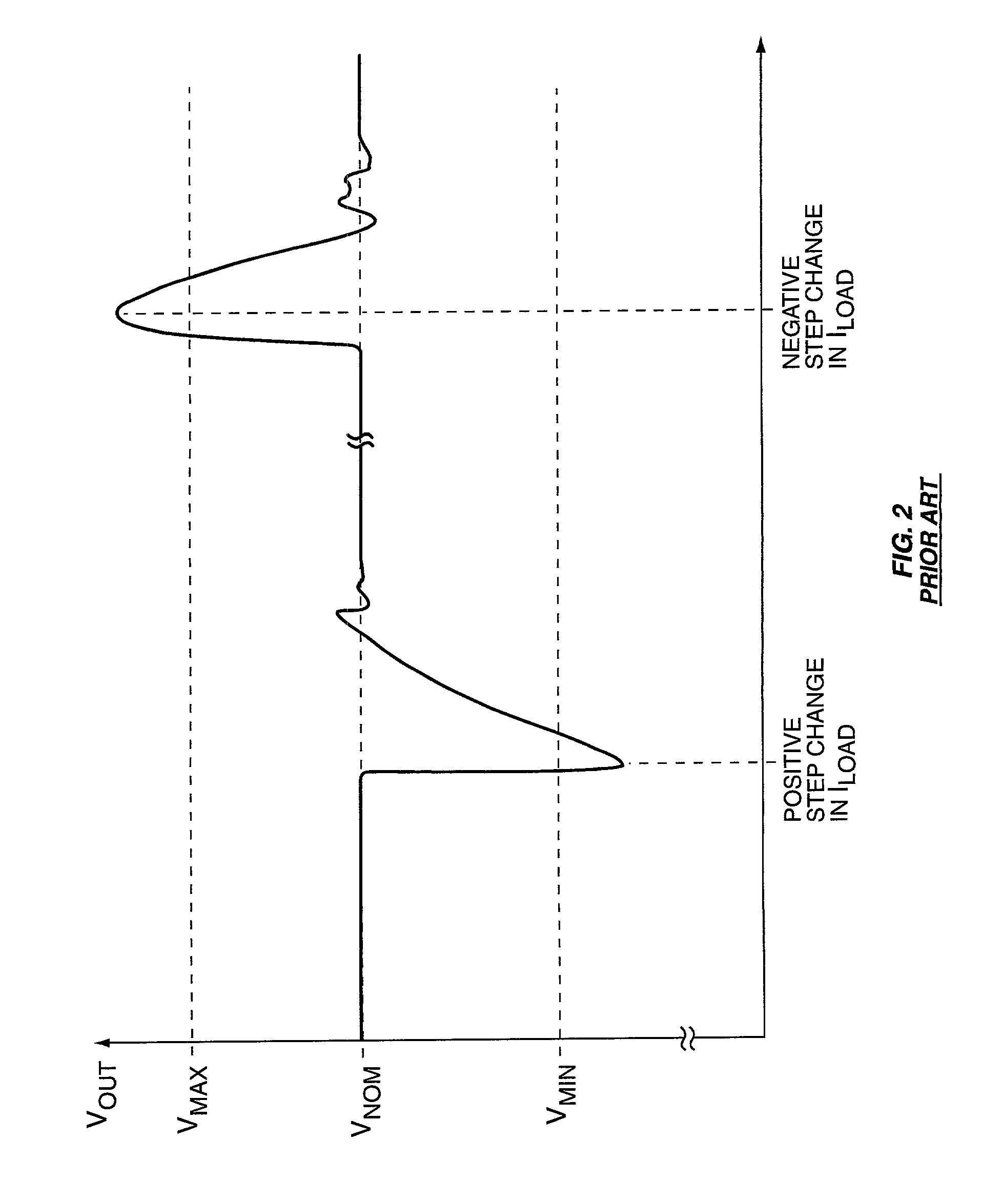

Bounded power supply voltage positioning

InactiveUS20020125871A1Facilitates active voltage positioningPrevent fallingDc-dc conversionElectric variable regulationVoltage amplitudeLower limit

A voltage positioning technique allows a power supply controller to more fully exploit active voltage positioning as a way of maintaining supply voltage within the limits defined for an associated electrical load. The supply voltage is allowed to "droop" as a function of load current. Droop may be implemented in linear proportion to load current, or as a discrete droop function once load current exceeds a given threshold. In either case, the droop circuitry of the supply controller implements a bounding function that establishes an accurately known maximum droop voltage magnitude. This maximum droop voltage limit establishes a reliable lower limit for the supply voltage independent of increasing load current. This accurately set lower bound for the droop voltage enables the controller to more aggressively position the supply voltage at the lower voltage limit of the load, which minimizes voltage overshoot and load power consumption.

Owner:SEMTECH CORP

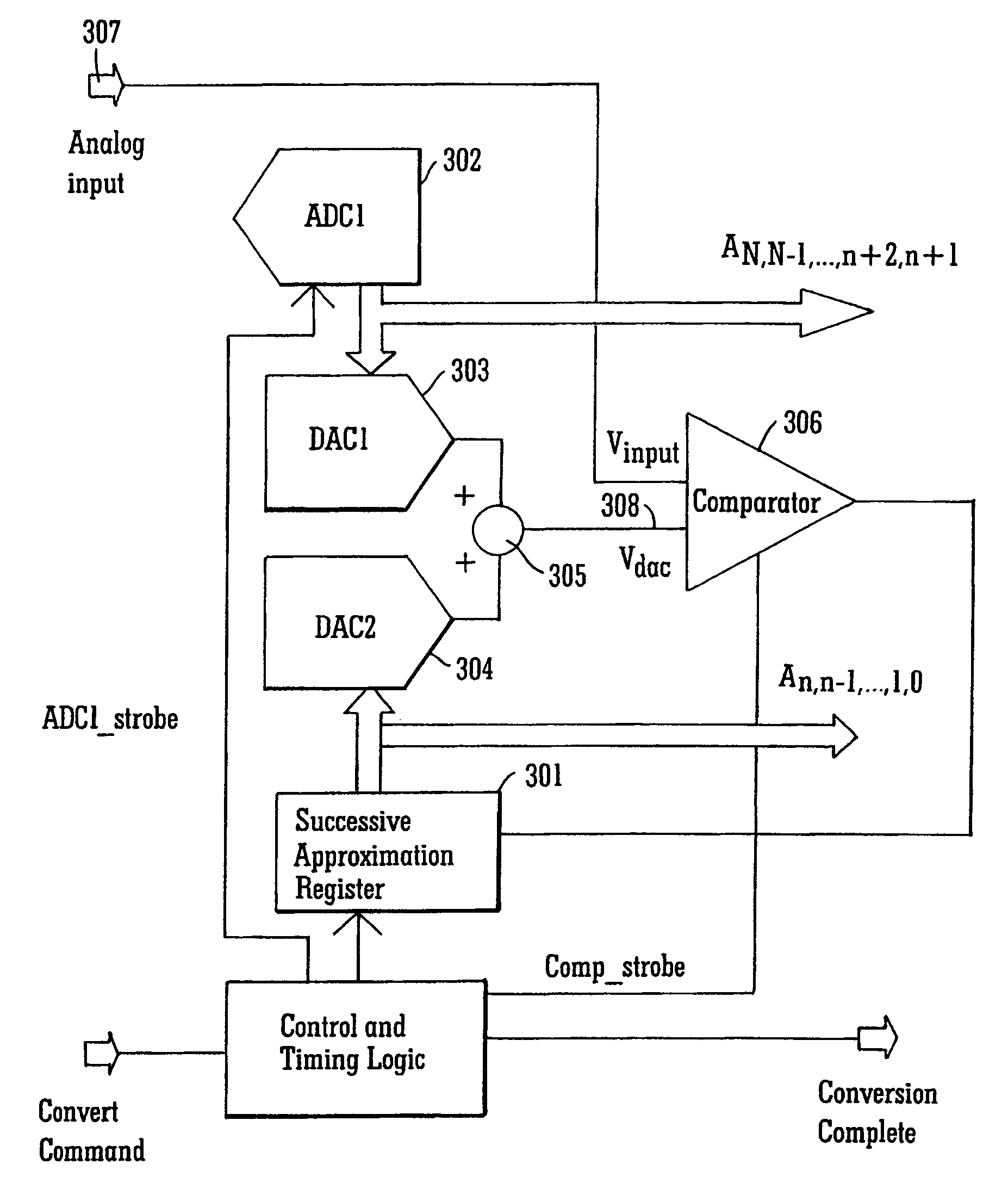

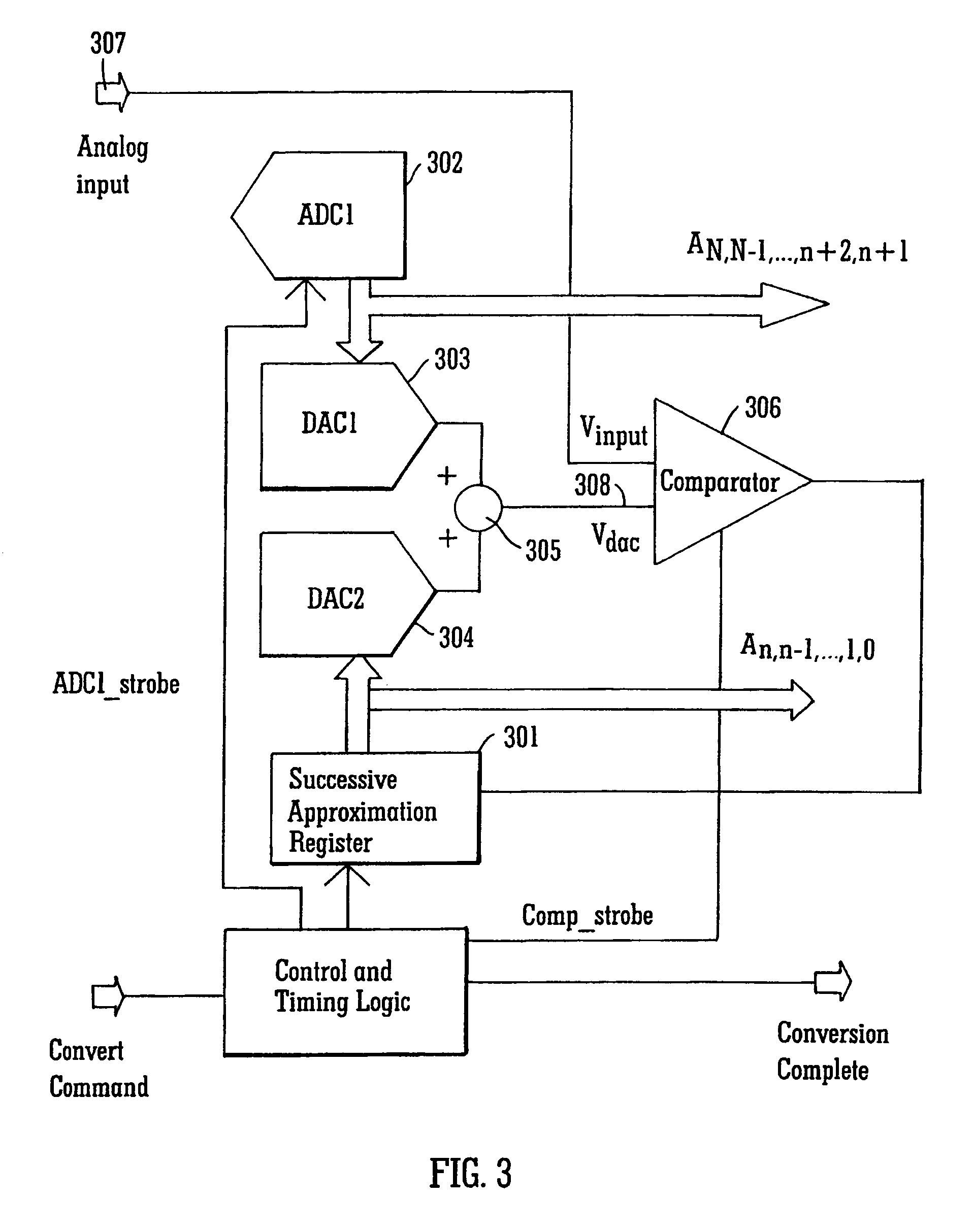

Successive approximation analog-to-digital converter with pre-loaded SAR registers

InactiveUS7038609B1Efficiently transitionEliminate effectiveElectric signal transmission systemsAnalogue-digital convertersDigital down converterFlash ADC

A SAR converter having enhanced performance by virtue of effectively pre-loading the SAR's most significant bits with a value that makes the associated DAC output almost equal to the signal to be converted. A normal SAR conversion is then completed with the SAR bits that have not been pre-loaded. The value used to pre-load the most significant bits of the SAR is preferably obtained from a low-resolution, high-speed converter, such as a flash. The range of DAC bits used in the normal SAR part of the conversion may be increased such that errors up to a certain magnitude in the high-speed converter can be corrected. Reducing power consumption of a SAR system can be readily accomplished by reducing comparator supply voltage. For a SAR converter architecture using a CAPDAC array or CAPDAC (capacitor array DAC), fairly large variations in comparator input voltage can be expected under these circumstances. If the input voltage variation becomes too large, damage to the comparator input devices can occur, or inaccuracies may develop. In one embodiment of the invention, the most significant bits are provided by sampling the input signal through a flash ADC that does not suffer from the input voltage restriction described above.

Owner:ANALOG DEVICES INC

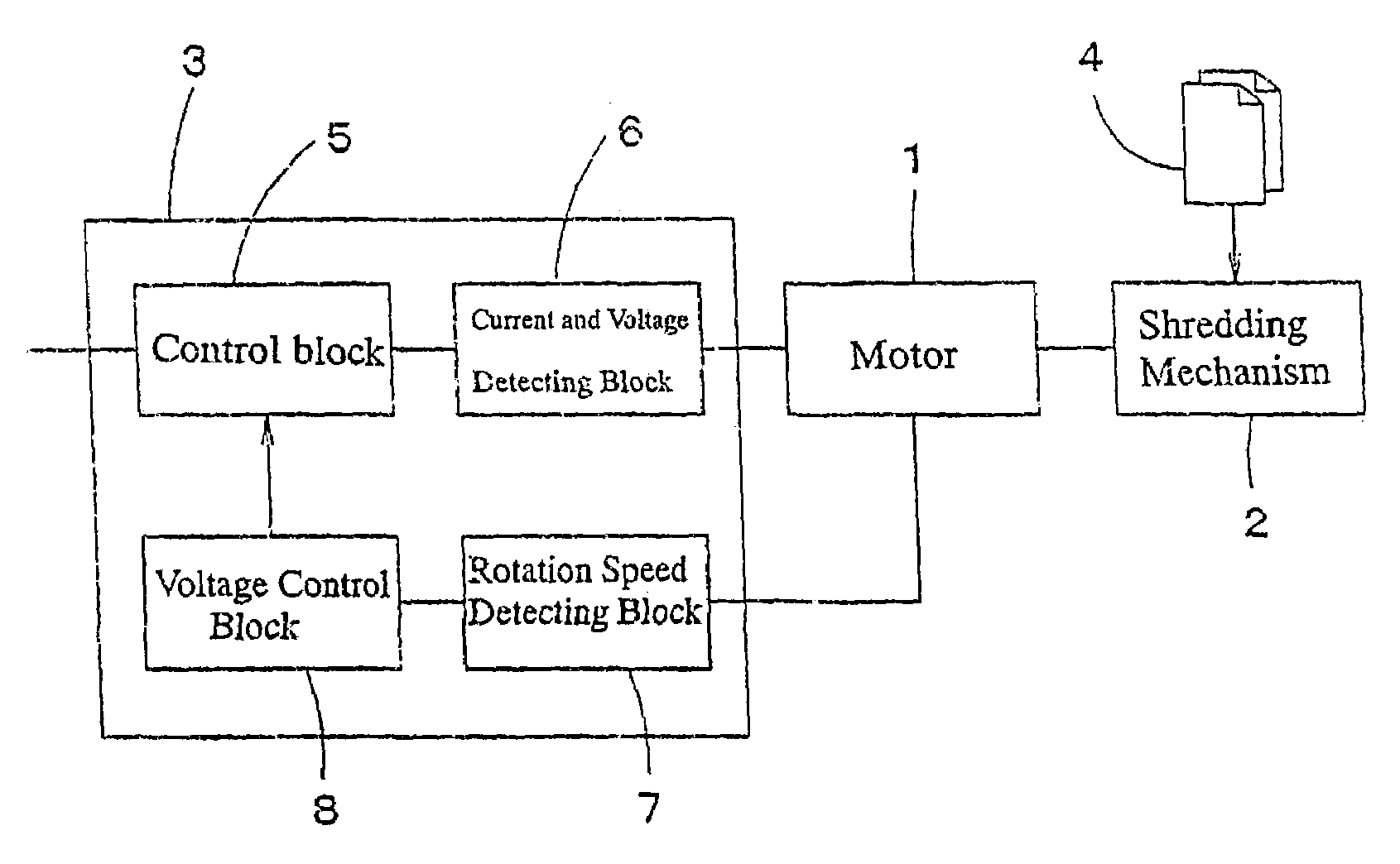

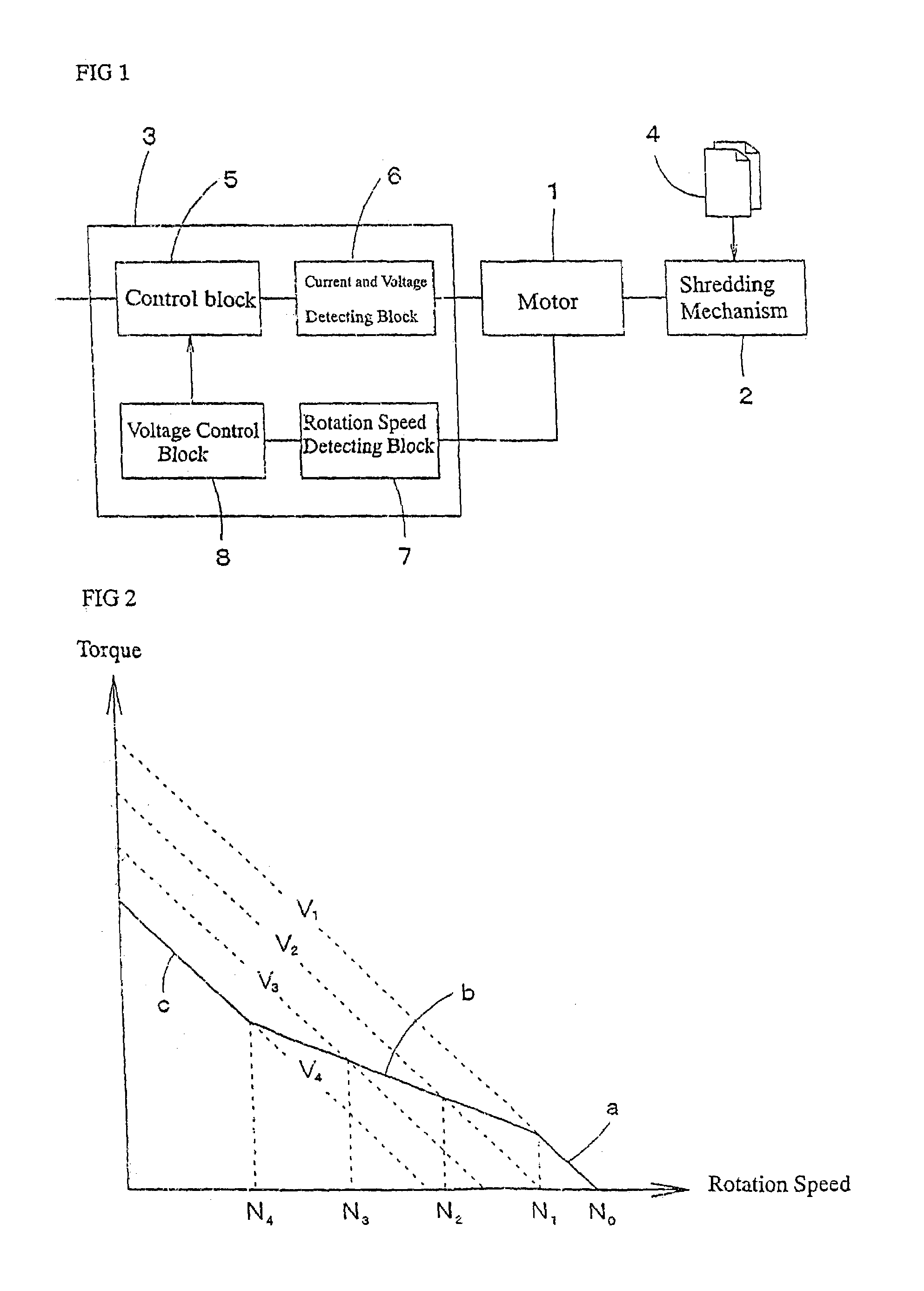

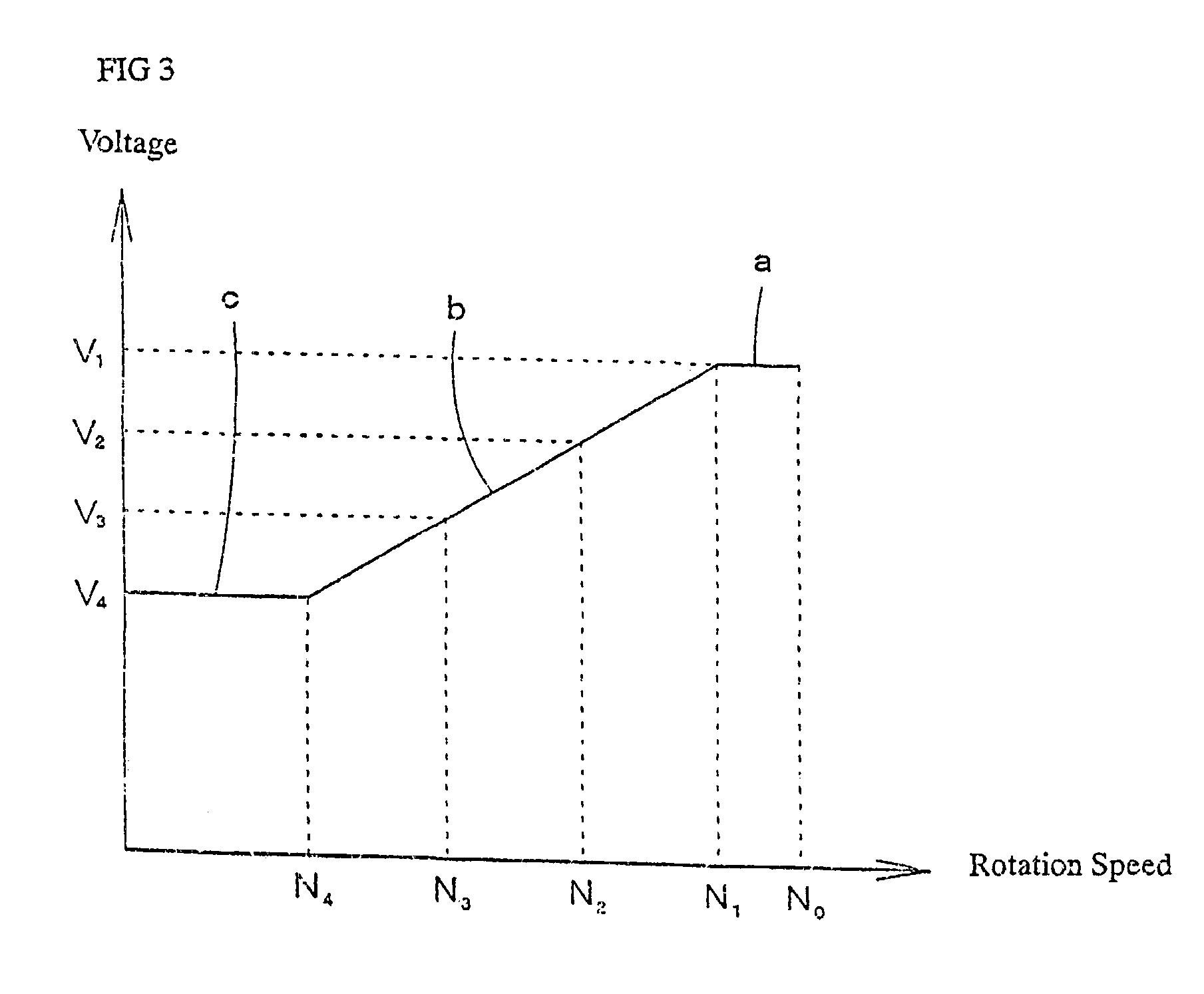

Motor control circuit for paper shredders

InactiveUS6997408B2Control power consumptionImprove energy savingElectric motor controlEnergy industryLow speedControl power

A paper shredder enables to control power consumption and achieve energy saving by realizing a torque characteristic of low torque at high speed or high torque at low speed keeping an output of a motor within a steady level. This circuit adopts a paper shredder structured with a driving motor for a rotary cutter having an inverted linear flow characteristic between rotation speed and torque and a control circuit composed of a detecting block for said rotation speed of said motor, a voltage control block for restricting a voltage output of said motor within a certain range in accordance with said rotation speed, and a current and voltage detecting block for monitoring a current flow of said motor. While a voltage is decreased on account of motor rotation speed which correlates negatively with a torque increase of said motor in shredding papers, when a voltage is restricted to a minimum by said voltage control block, an operation of said motor is to be suspended or reversed in the case that a current detected by said current and voltage detecting block exceeds a certain level. If a motor current detected by said current and voltage detecting block exceeds a certain level, a motor operation is to be suspended or reversed by a delaying circuit.

Owner:NAKABAYASHI CORP +1

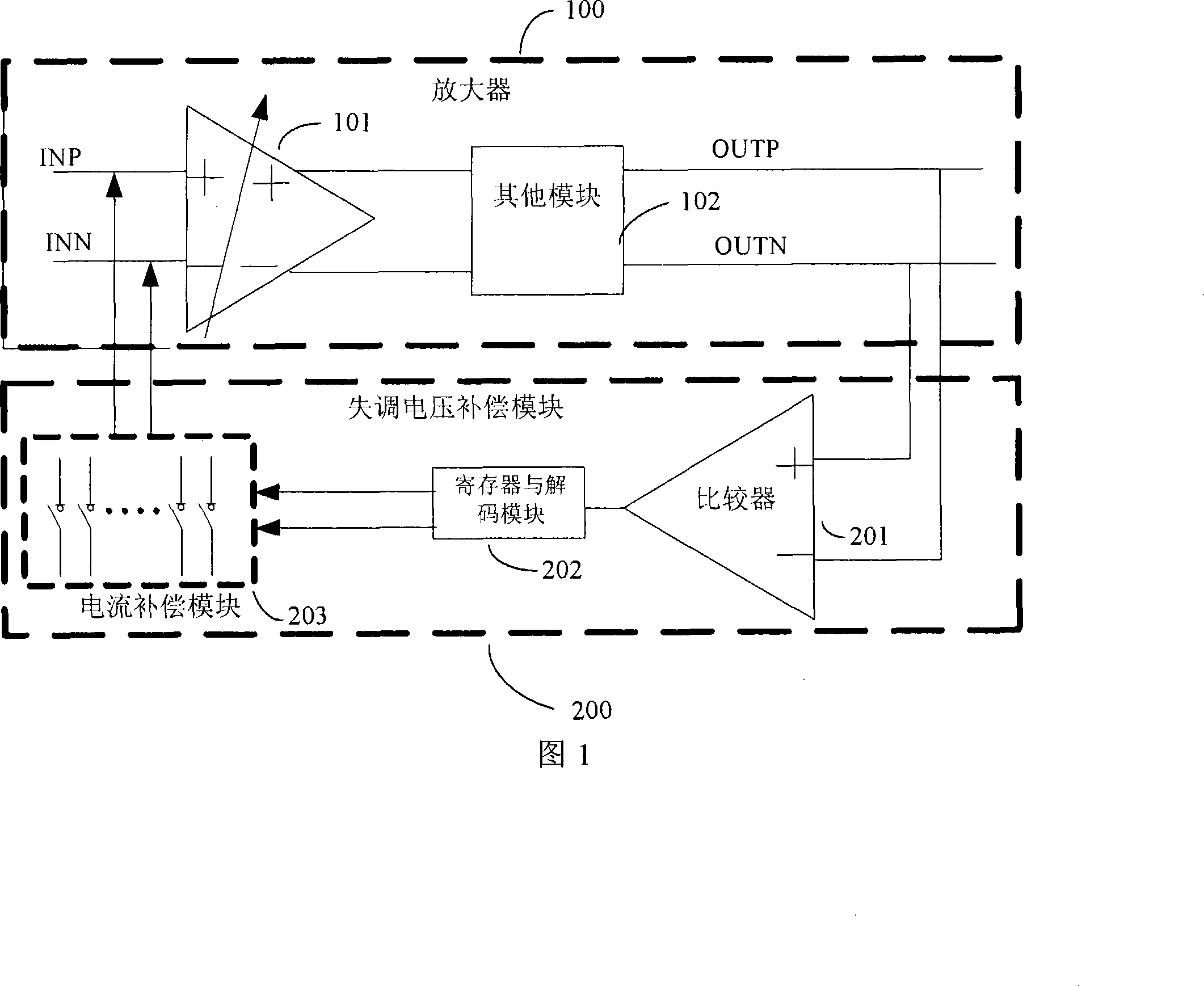

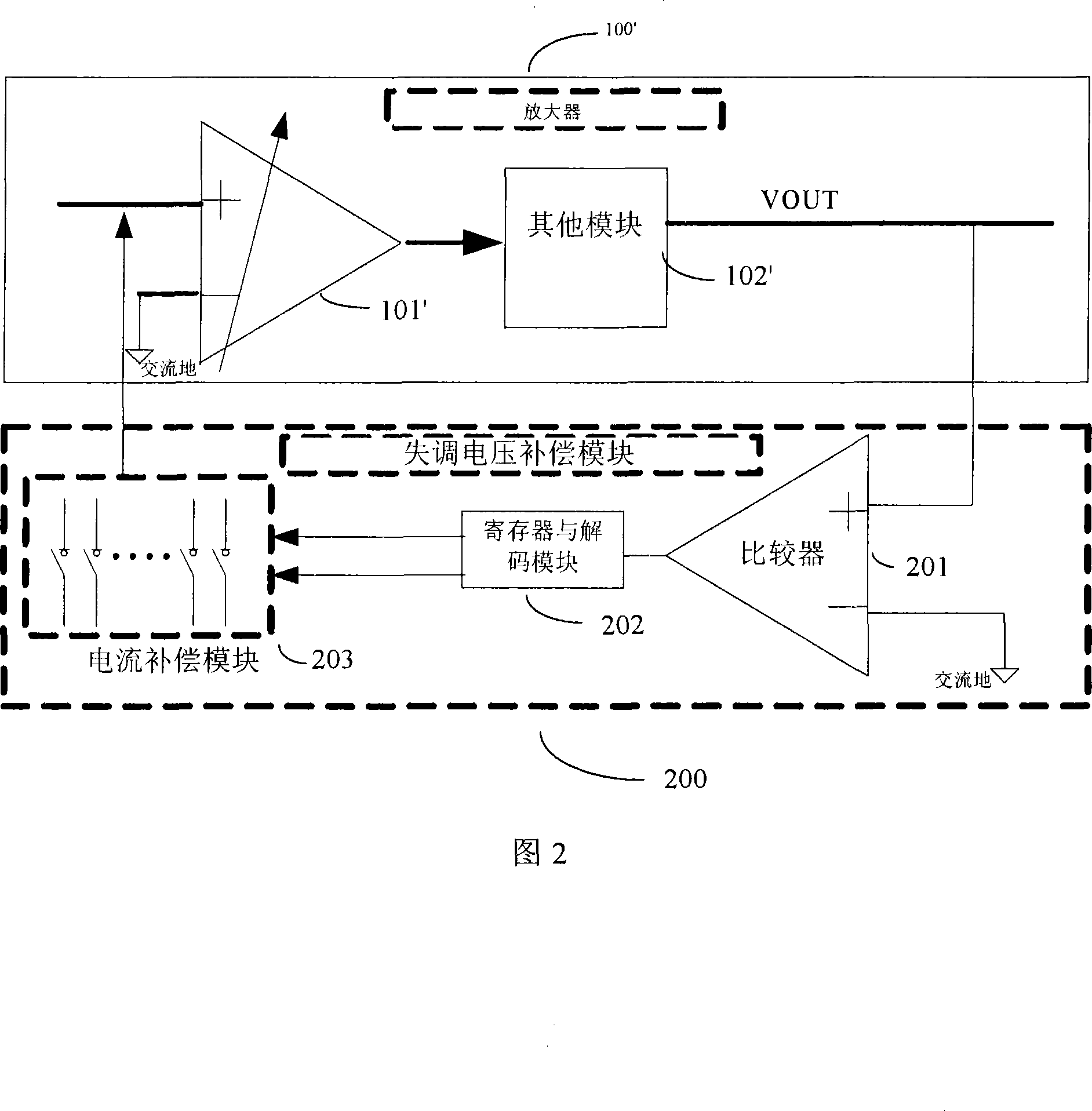

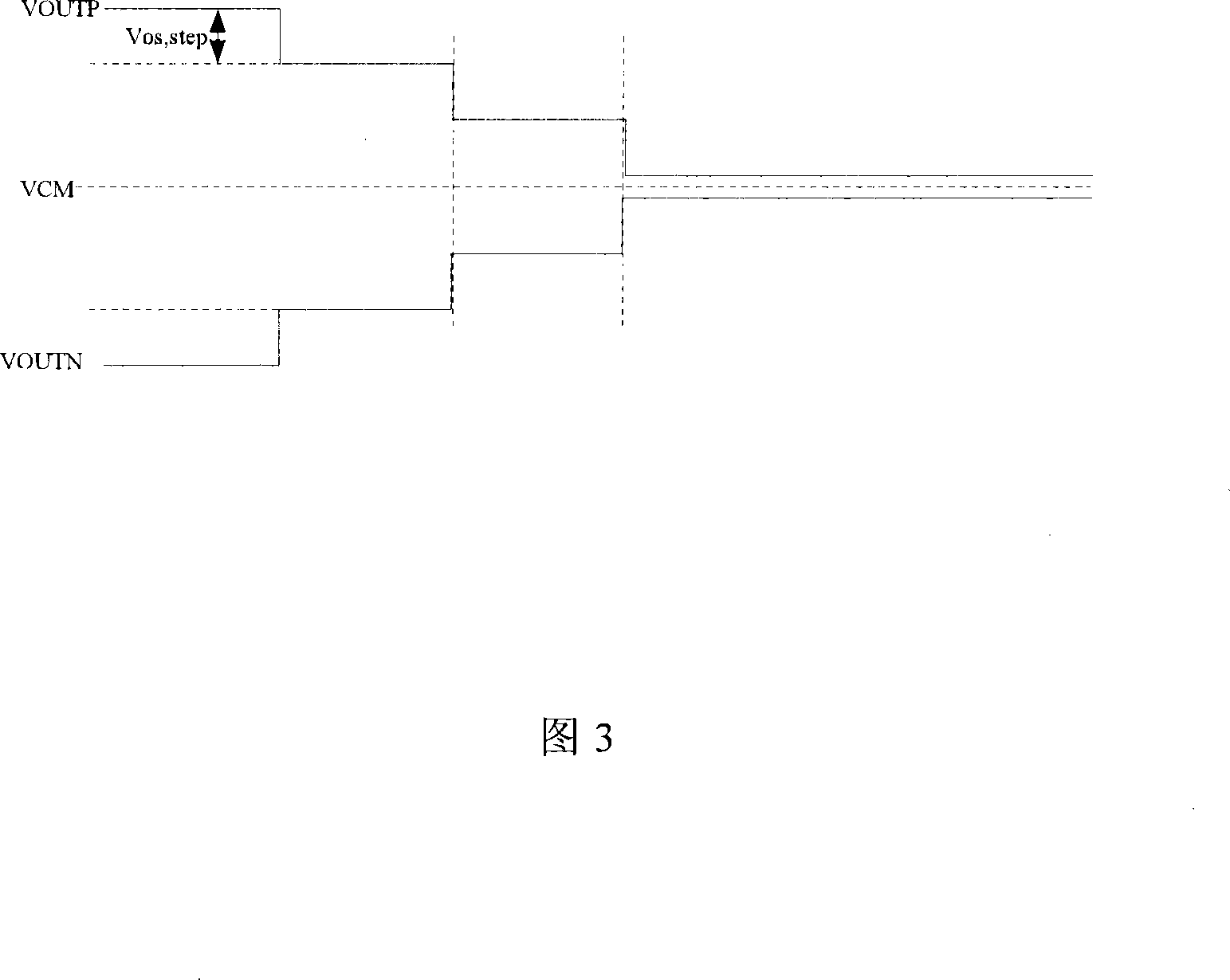

A compensatory method and device for DC offset voltage of amplifier

InactiveCN101217263ASmall scaleSimple structureDifferential amplifiersDc-amplifiers with dc-coupled stagesAudio power amplifierSwitching frequency

The invention provides a compensating method of the switching frequency of a amplifier which comprises the following steps: two output end polarities is compared in the state in which the amplifier has no signal outputting; the inputting end current of the amplifier is adjusted according to the electrode; repeated circle is carried out until achieving the requirement of stopping the cycle. The invention also provides a compensating device of the DC offset voltage of the amplifier which comprises a comparator, a register, a decoding module and a current compensation module. The invention has the advantages of simple structure, low cost, small power-consumption. Meanwhile, the invention is used both for a signal amplifier and an amplifier system, which can limit the imbalance voltage to be in small scope.

Owner:APEXONE MICROELECTRONICS

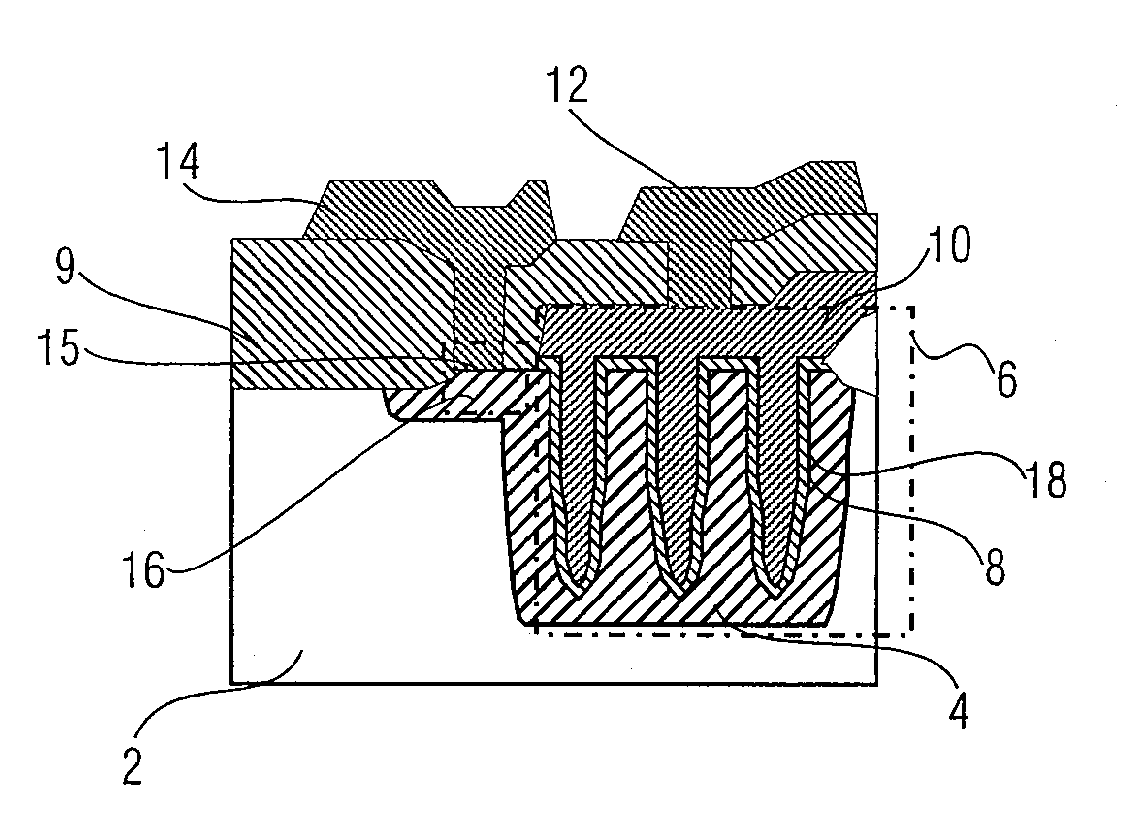

Integrated Snubber Device on a Semiconductor Basis for Switching Load Reduction, Voltage Limitation and/or Oscillation Attenuation

ActiveUS20070274014A1Reduce spendingSemiconductor/solid-state device detailsSolid-state devicesUltrasound attenuationElectric network

Integrated snubber device on a semiconductor basis for wiring an electric network for absorbing electric energy from an electric energy store, of an electric network, including at least two terminals for being connected to the electric network to be wired, an electric resistor structure, and a reactance structure, which are connected between the terminals.

Owner:FRAUNHOFER GESELLSCHAFT ZUR FOERDERUNG DER ANGEWANDTEN FORSCHUNG EV

Surface-mediated cells with high power density and high energy density

ActiveUS20130202945A1Improvement factorImprove diffusivityPrimary cell to battery groupingMaterial nanotechnologyElectrical batteryHigh energy

A surface-mediated cell (SMC) comprising: (a) a cathode comprising a carbon-based cathode active material having a surface area to capture or store lithium thereon; (b) an anode comprising an anode current collector alone, or combined anode current collector and anode active material; (c) a porous separator disposed between the anode and the cathode; (d) a lithium-containing electrolyte, wherein the anode and / or cathode active material has a specific surface area no less than 100 m2 / g in direct physical contact with the electrolyte to receive lithium ions therefrom or to provide lithium ions thereto; and (e) a lithium source disposed in at least one of the two electrodes when the cell is made, and the cell has an open-circuit voltage (OCV) of at least 0.8 volts; wherein the cell operates between a lower voltage limit lower than the OCV and an upper limit of between 3.8 and 4.5 volts.

Owner:GLOBAL GRAPHENE GRP INC +1

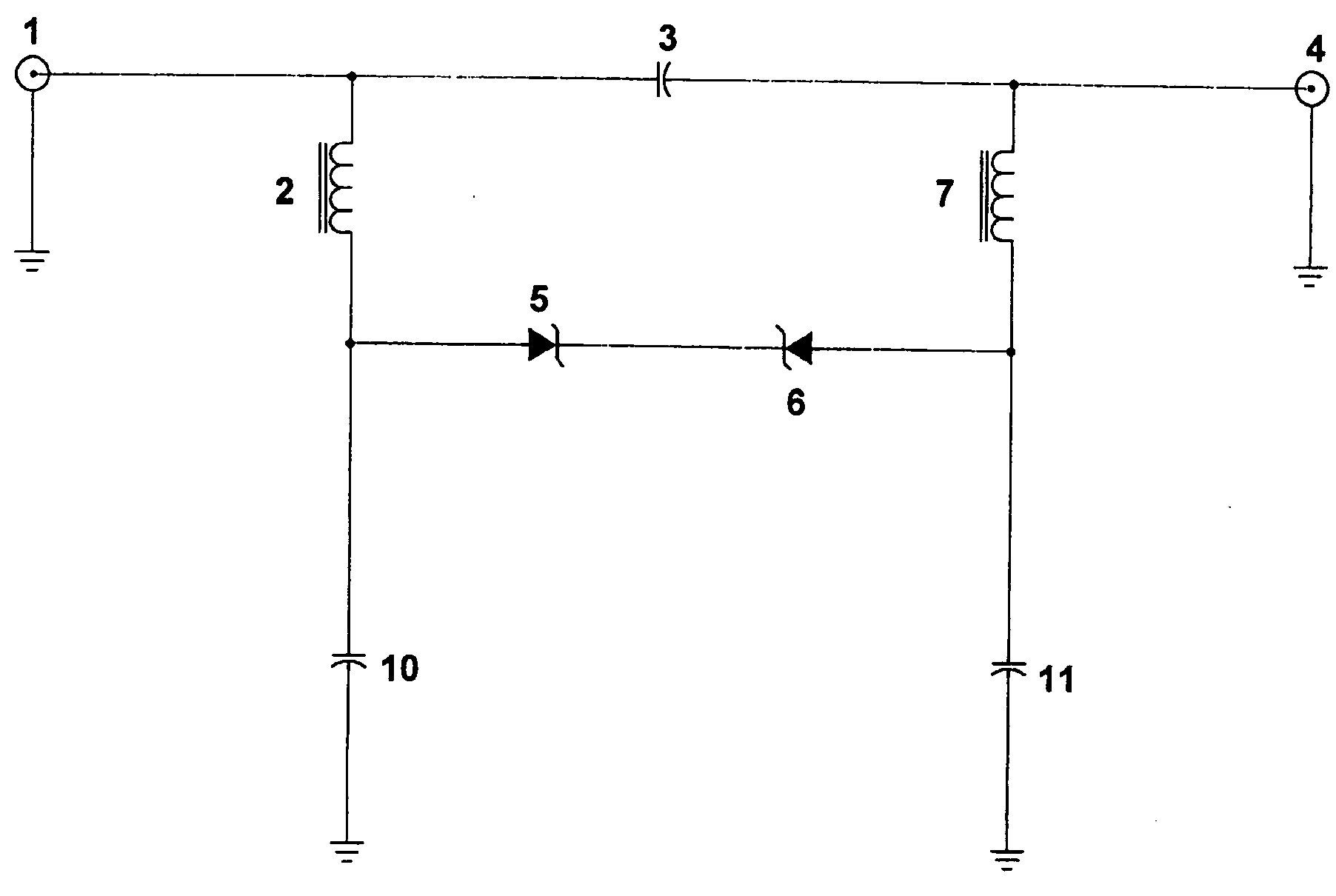

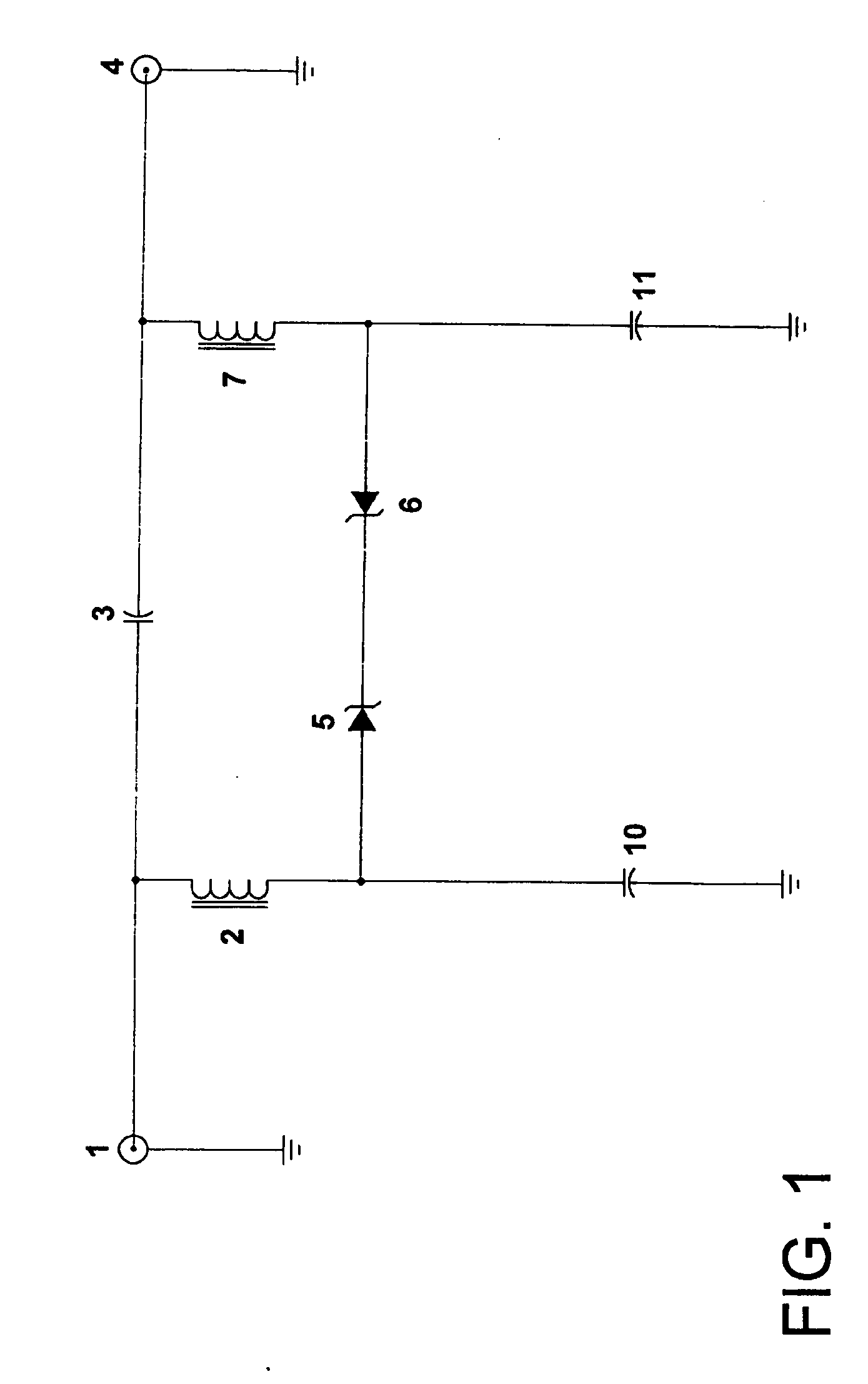

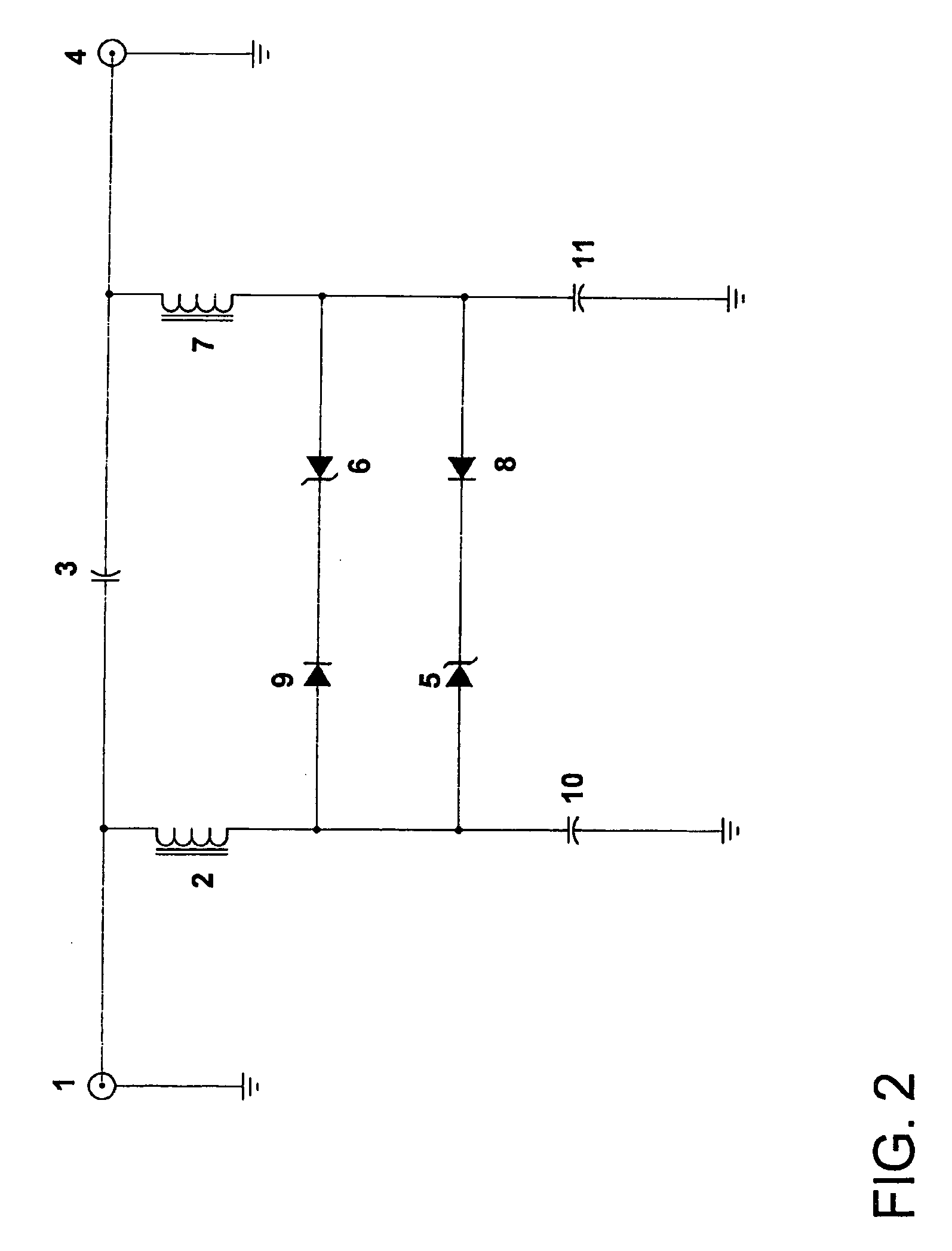

Voltage limiter for coaxial cable carrying RF signals and voltage

InactiveUS20050047051A1Easy to installImprove efficiencyEmergency protective arrangement detailsBroadcast transmission systemsCoaxial cableAC power

A voltage limiter for a coaxial cable line that carries an RF signal and an AC powering voltage signal is provided, including a signal input carrying a first AC voltage signal and an RF signal, a signal output arranged in series with the input and carrying the RF signal and a second AC voltage signal that is lower than the first AC voltage signal, and a voltage limiting mechanism arranged between the input and the output. The voltage limiting mechanism reduces the first AC voltage signal to the second AC voltage signal without substantially affecting the integrity of the RF signal.

Owner:EAGLE COMTRONICS

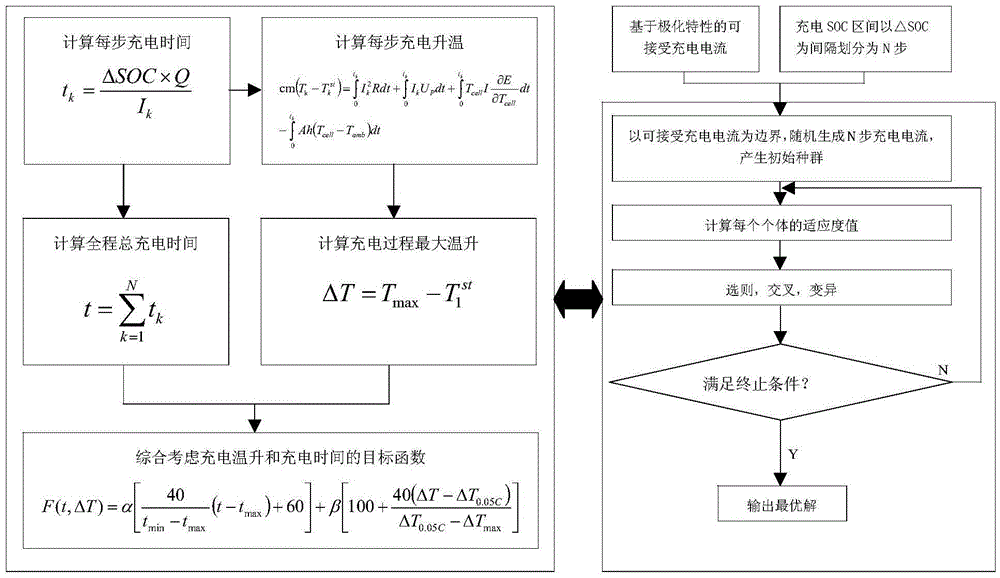

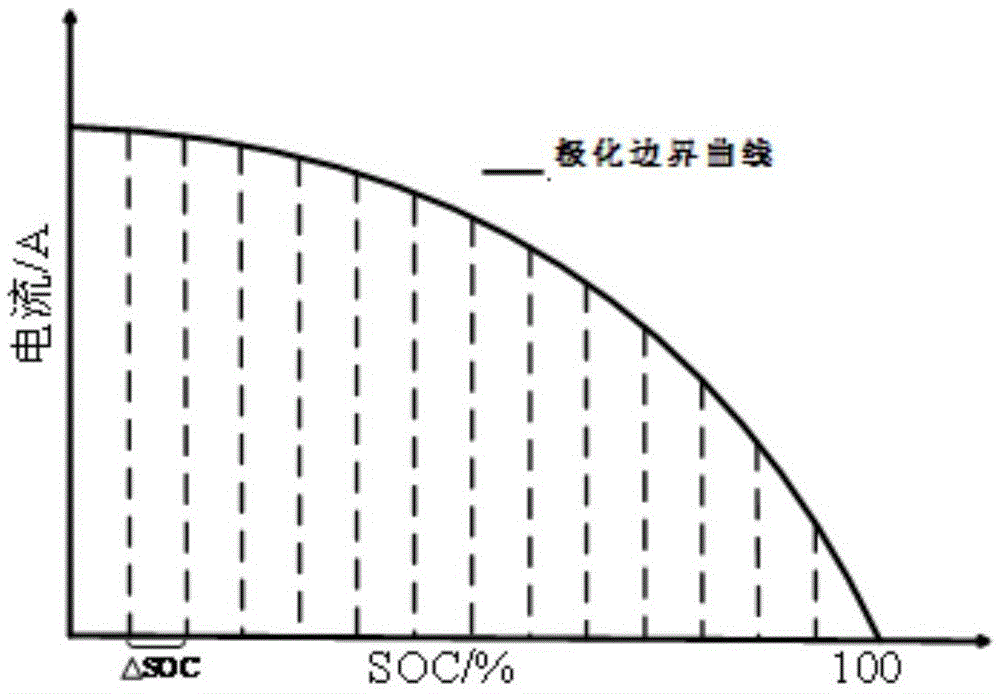

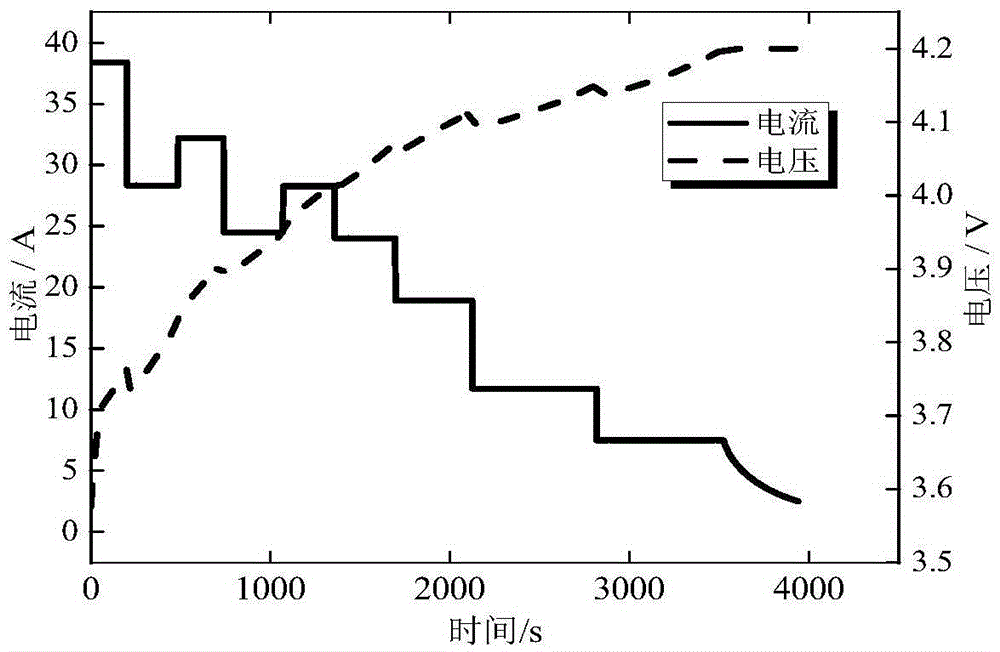

Lithium ion battery optimized charging method based on time and temperature

ActiveCN105552465ALimit charging temperature riseAvoid thermal runawayBatteries circuit arrangementsSecondary cells charging/dischargingCharge currentGenetic algorithm

The invention relates to the technical field of battery charging, in particular to a charging method of a lithium ion battery based on time and temperature. Polarization voltage limited maximum charging current is calculated based on lithium ion battery polarization characteristics, and under the constraint of the maximum charging current, charging temperature rise and charging time are considered comprehensively, genetic algorithm is employed to search the optimal charging current so as to balance the mutual contradictory objects of reducing charging time and lowering charging temperature rise. The result shows that the optimal charging current ensures charging rapidity, at the same time controls the polarization voltage and temperature rise of the charging process within an allowable range, and guarantees the charging capacity, charging efficiency and charging safety and battery life.

Owner:BEIJING JIAOTONG UNIV

Voltage control at windfarms

Owner:GE INFRASTRUCTURE TECH INT LLC