Chip screening method and apparatus

A screening method and chip technology, applied in the field of communication, can solve problems such as high cost, low reliability, and high subjectivity, and achieve the effect of reducing screening cost and high reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

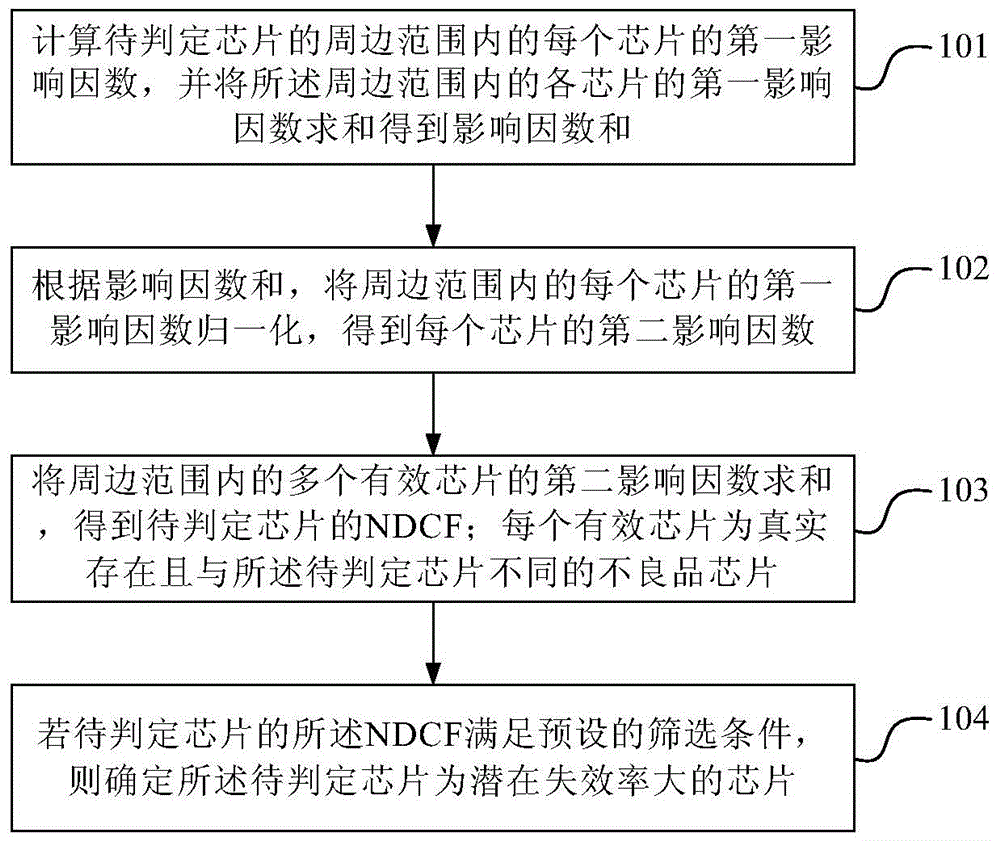

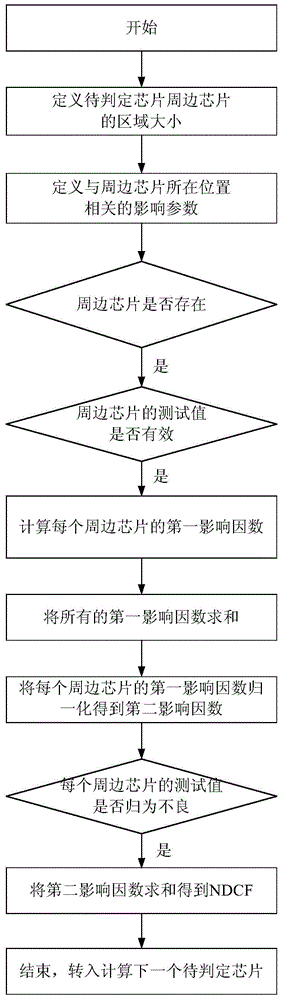

[0037] The chip screening method described in the embodiment of the present invention is a method of data statistics and probability statistics, which is based on the WaferMap (wafer mapping) data reflecting the situation of good chips obtained from the wafer test (WaferCP test). The peripheral range chips of the good product (PassDie) obtained in the pass die are counted to evaluate the possibility of potential failure of the good product chip. It should be noted that the term "chip" mentioned in the following example description, if it is applied to the description of wafer (Wafer), should actually be called wafer "Die". For the sake of uniformity, the full text is written as " chip". Therefore, the chip may be various types of semiconductor devices produced by semiconductor processing techniques such as wafers or wafers. In wafer testing, multiple chips are placed on a plane or platform with a certain distance from each other, and the distance between each chip can be equa...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More