High-speed parallel acquisition system clock synchronization device

A collection system, clock synchronization technology, applied in the direction of measuring device, radio wave measurement system, radio wave reflection/re-radiation, etc., to eliminate the influence of errors, facilitate miniaturization, good stability and reliability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0026] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

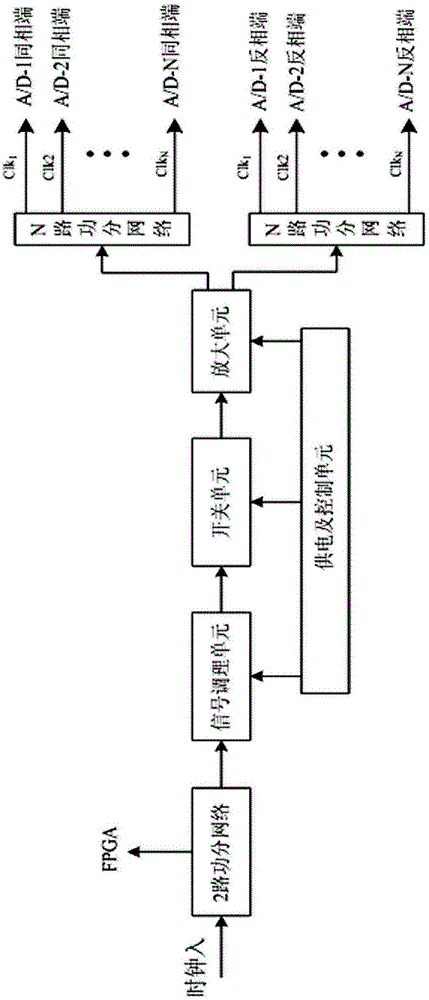

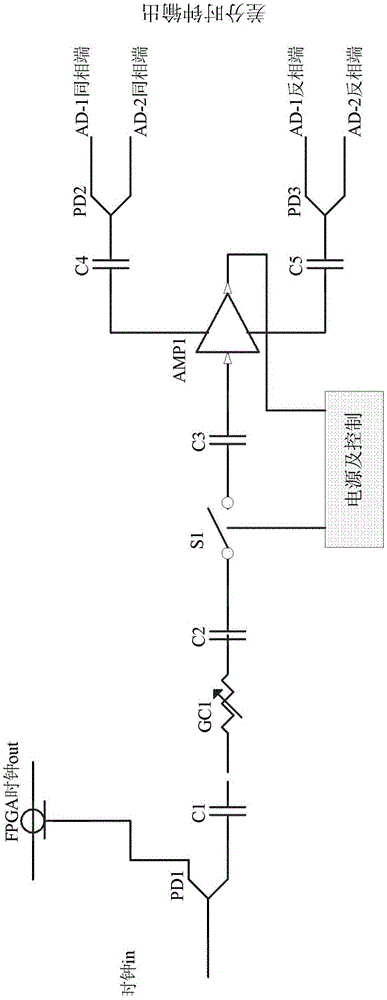

[0027] The invention discloses a clock synchronization device for a high-speed parallel acquisition system. The specific principle is: by configuring the peripheral circuit, the unstable time at the initial moment of the trigger is greatly compressed, that is, by configuring the signal conditioning unit, setting the range of the clock input amplitude, in the switch unit Before conduction, the signal amplitude is increased to a level sufficient to saturate the post-stage amplifier, thereby increasing the steepness of the rising edge of the switch through the saturation state of the amplifier, reducing the number of cycles of triggering the instantaneous critical amplitude, and triggering the clock signal at the initial momen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More