Super junction structure, super junction mosfet and manufacturing method thereof

A segment structure and column technology, applied in the field of super junction semiconductor devices, can solve the problems of reducing device breakdown voltage and high doping concentration in the top region, and achieve the effects of improving stability, short process cycle and low production cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

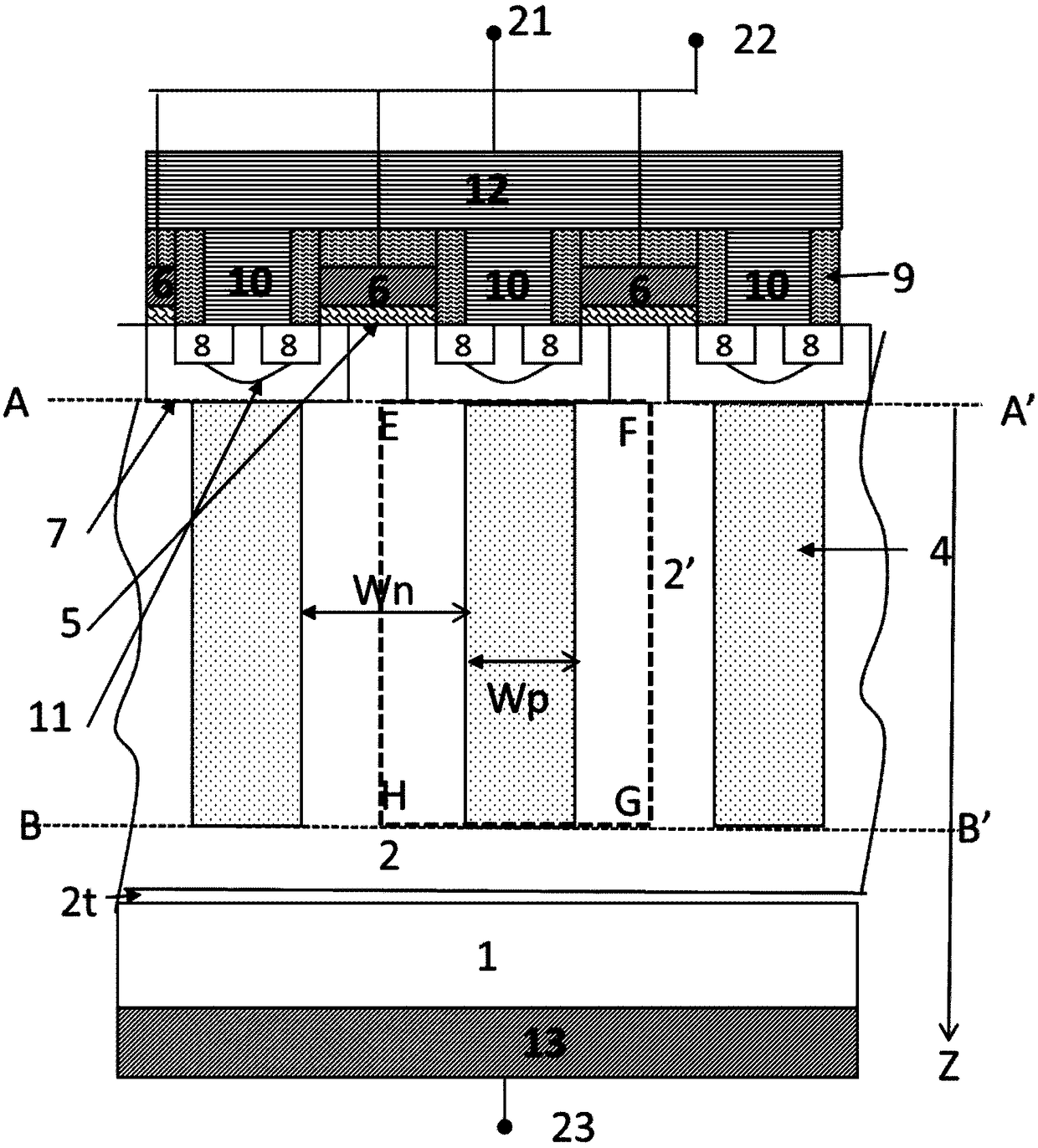

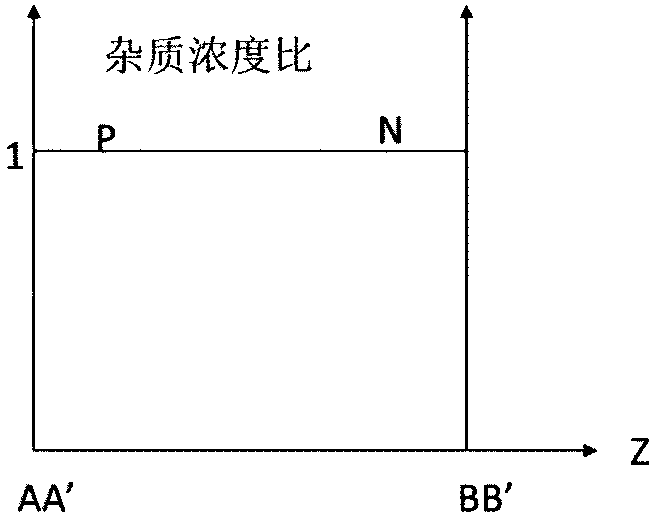

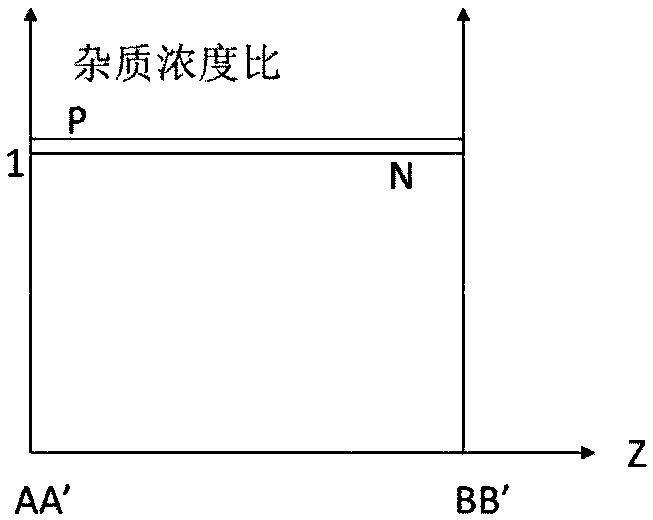

[0065] see Figure 4a , which is a specific embodiment of the super-junction structure of the present invention, which is a super-junction MOSFET (here, NMOSFET) to which the super-junction structure is applied. On the N-type heavily doped silicon substrate 1 is an N-type epitaxial layer 2. Due to the difference in doping concentration, there is a transition region 2t between the heavily doped silicon substrate 1 and the uniform concentration epitaxial layer 2, and the N-type epitaxial layer 2 Layer 2 has a plurality of P-shaped columns 4 . The N-type epitaxial layer 2 between every two adjacent P-type pillars 4 can be regarded as an N-type pillar 2'. In this way, a plurality of P-type pillars 4 and N-type pillars 2' arranged alternately are formed in the N-type epitaxial layer 2, that is, a super-junction structure. The super-junction structure here refers to Figure 4a The area between AA' under the middle p-well 7 and the bottom of the trench BB', such as Figure 4b show...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com