Fixed-bit-width multiplier with high accuracy and low energy consumption properties

A low-energy, fixed-bit technology, used in instruments, electrical digital data processing, digital data processing components, etc., can solve the problem of low application value, large errors in operation results and accurate results, and restricting the application of fixed-bit width CSD multipliers. scope, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

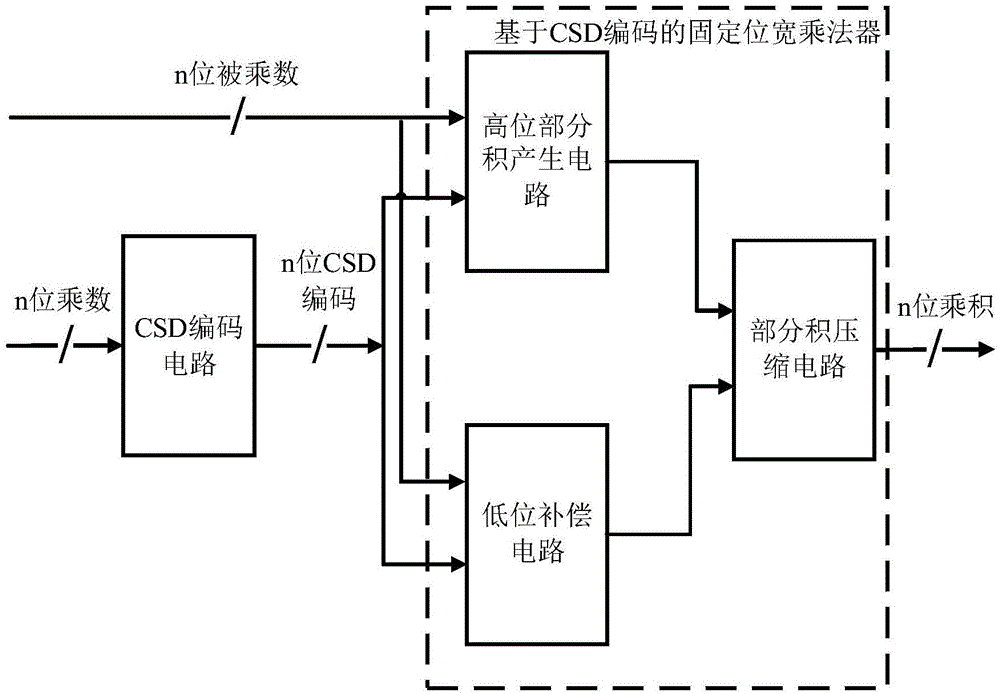

[0050] In order to improve the problem that the traditional fixed bit width CSD multiplier cannot take into account the accuracy, power consumption and speed, the present invention designs a high-precision low-bit compensation circuit, adopts a simple circuit structure, reduces the hardware overhead of the overall circuit, and improves the multiplication The operating speed of the device. The low-bit compensation structure of the present invention can be operated in parallel with the partial product compression circuit to a certain extent, further improving the operation speed of the overall circuit;

[0051] This example works as follows:

[0052] In this example, it is mainly divided into four main circuit parts, CSD encoding circuit, high-order partial product generation circuit, low-order compensation circuit and partial product compression circuit.

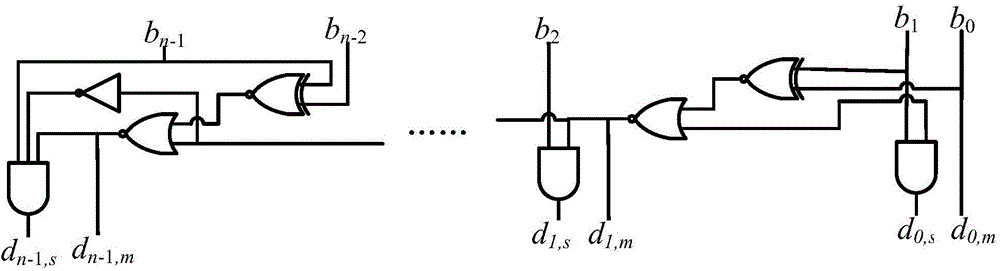

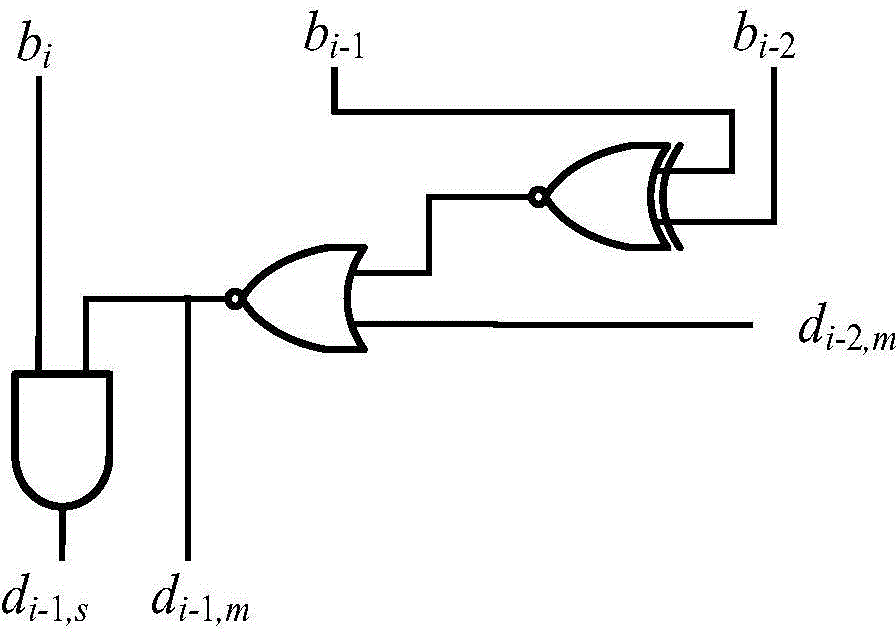

[0053] The CSD encoding circuit adopts an iterative serial structure, such as figure 2 and image 3 As shown, its logic...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More