Built-in automatic aging testing device of integrated circuit chips

A technology for integrated circuit and burn-in testing, which is applied in the field of integrated circuit testing and reliability assessment testing. It can solve the problems of high cost and time cost, and achieve the effects of saving time and cost, adjusting the aging voltage, and saving costs.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

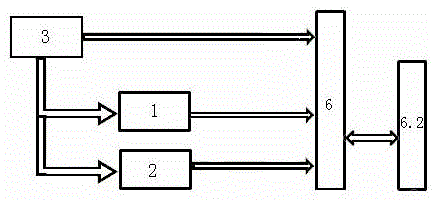

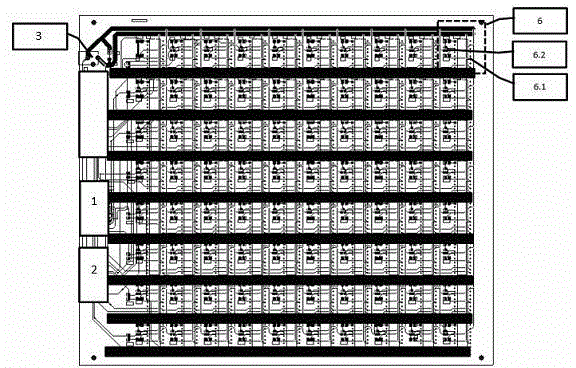

[0015] see figure 1 and figure 2 , The built-in integrated circuit chip automatic aging test device of the present invention includes a reset module 1, a clock signal module 2, a power module 3 and a large number of test units 6 neatly arranged. Each test unit 6 respectively includes a chip holder 6.1 for placing the chip to be tested and a status display light 6.2, and each chip to be tested is equipped with a memory module. The reset module 1 , the clock signal module 2 and the power module 3 are respectively connected to each test unit 6 , and the power module 3 supplies power to the reset module 1 , the clock signal module 2 and each test unit 6 respectively.

[0016] The steps of the test method using the automatic aging test device of the above-mentioned embodiments of the present invention are as follows:

[0017] 1) Download the automatic burn-in test program to the memory module of the chip under test. The automatic aging test program must support the aging proces...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com