A Synchronization Method for Software-Hardware Co-simulation

A technology of software and hardware collaboration and event triggering, applied in software simulation/interpretation/simulation, instruments, calculations, etc., can solve the problem of long time-consuming recording of waveforms, inability to make continuity test cases, and inability of verifiers to know and make decisions in time Check and other issues to achieve the effect of reducing the programming burden

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0009] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without creative efforts fall within the protection scope of the present invention.

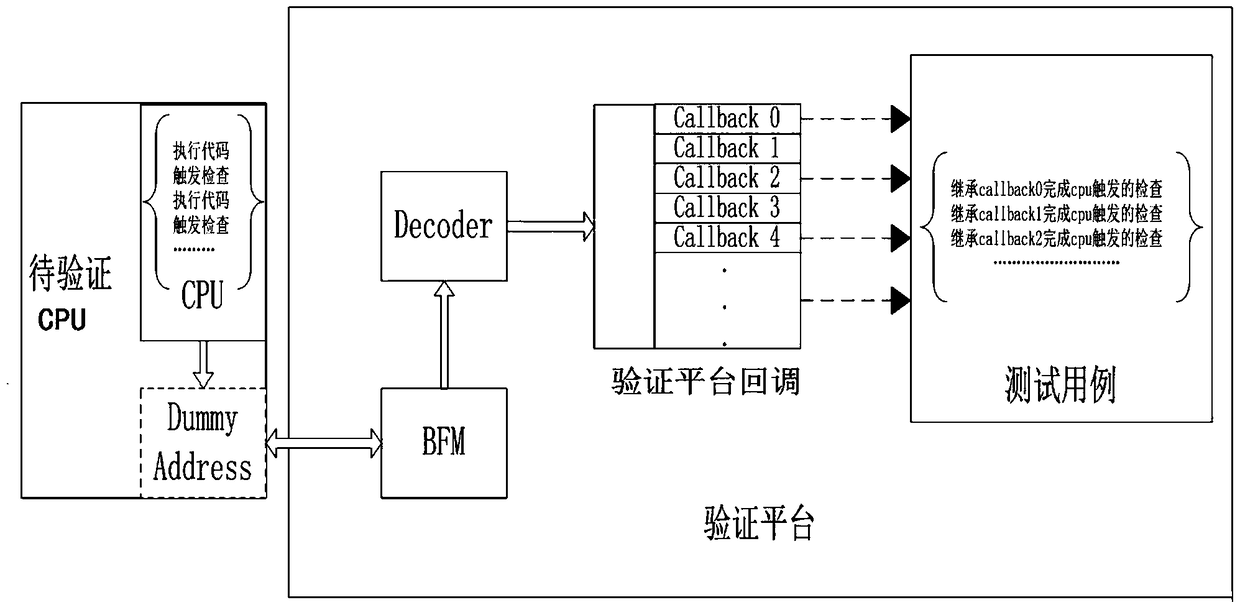

[0010] figure 1 It is a system block diagram of the synchronization method of software and hardware co-simulation. The CPU to be verified is connected to the verification platform through a bus. It is characterized in that a trigger event address space is reserved in the CPU to be verified. The virtual address Dummy Address that coincides with the actual address of the CPU internal register and memory to be verified; the trigger event address space is divided into ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More