A simultaneous testing method and system supporting multiple pcie cards

A test method and test data technology, applied in the field of testing, can solve problems such as low efficiency and single test content, and achieve the effect of reducing the number of tests, wide applicability, and improving test efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

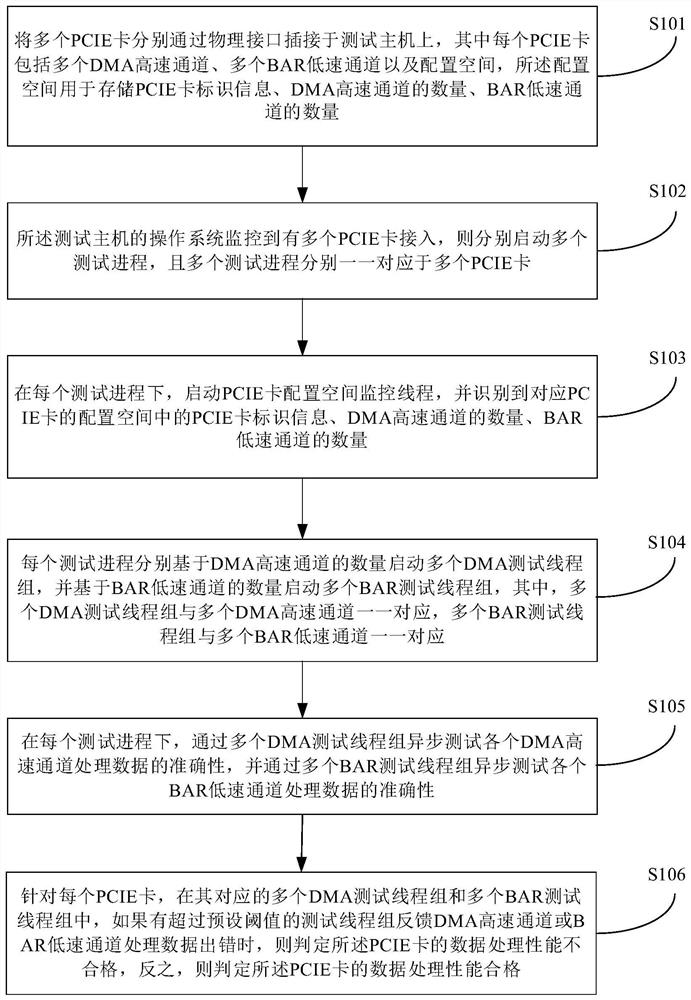

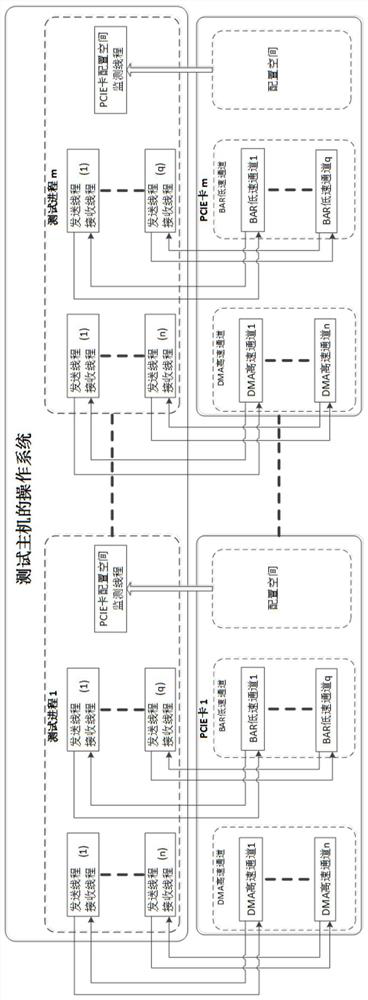

[0051] Such as figure 1 As shown, the embodiment of the present invention provides a kind of simultaneous testing method that supports a plurality of PCIE cards, and described method comprises the following steps:

[0052] S101: Insert a plurality of PCIE cards on the test host through physical interfaces, wherein each PCIE card includes a plurality of DMA high-speed channels, a plurality of BAR low-speed channels and a configuration space, and the configuration space is used to store PCIE card identification information , the number of DMA high-speed channels, the number of BAR low-speed channels;

[0053] S102: The operating system of the test host monitors that multiple PCIE cards are connected, and then starts multiple test processes respectively, and the multiple test processes correspond to multiple PCIE cards one by one;

[0054] S103: Under each test process, start the PCIE card configuration space monitoring thread, and identify the PCIE card identification informati...

Embodiment 2

[0060] On the basis of the above-mentioned embodiment 1, the difference between the embodiment of the present invention and the above-mentioned embodiment is that this embodiment further optimizes the test process in step S105, and each DMA test thread group includes A DMA sending thread for channel sending test data and a DMA receiving thread for receiving response data, each BAR test thread group includes a BAR sending thread for sending test data to the BAR low-speed channel and a BAR receiving thread for receiving response data, Specifically:

[0061] S1051: The DMA sending thread sends the DMA test data to the corresponding DMA high-speed channel, and the BAR sending thread sends the BAR test data to the corresponding BAR low-speed channel;

[0062] S1052: After the corresponding DMA high-speed channel receives the DMA test data and performs transparent transmission or processing, returns the DMA response data to the corresponding DMA receiving thread; at the same time, t...

Embodiment 3

[0065] In order to test the limit speed of each PCIE card, the embodiment of the present invention also provides a kind of simultaneous testing method that supports a plurality of PCIE cards, and the difference with each above-mentioned embodiment is that the present embodiment also includes the following steps:

[0066] S107: After determining that the data processing performance of the PCIE card is qualified, test the limit speed of each DMA high-speed channel through each DMA test thread group corresponding to the test process, and test the limit of each BAR low-speed channel through each BAR test thread group speed.

[0067] As a kind of implementable mode, the limit speed of each DMA high-speed channel is tested respectively by each DMA test thread group corresponding to the test process, specifically including:

[0068] S1071: The DMA sending thread repeatedly sends DMA test data to the corresponding DMA high-speed channel according to the preset initial frequency, and m...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More