Floating point fusion multiplication and addition method based on interior forward-push, apparatus and processor

A technology of adding device and floating point, applied in the direction of electrical digital data processing, digital data processing components, instruments, etc., can solve the problems of long blocking time and low execution speed, so as to reduce the blocking beat, improve the execution speed, reduce the The effect of running water

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

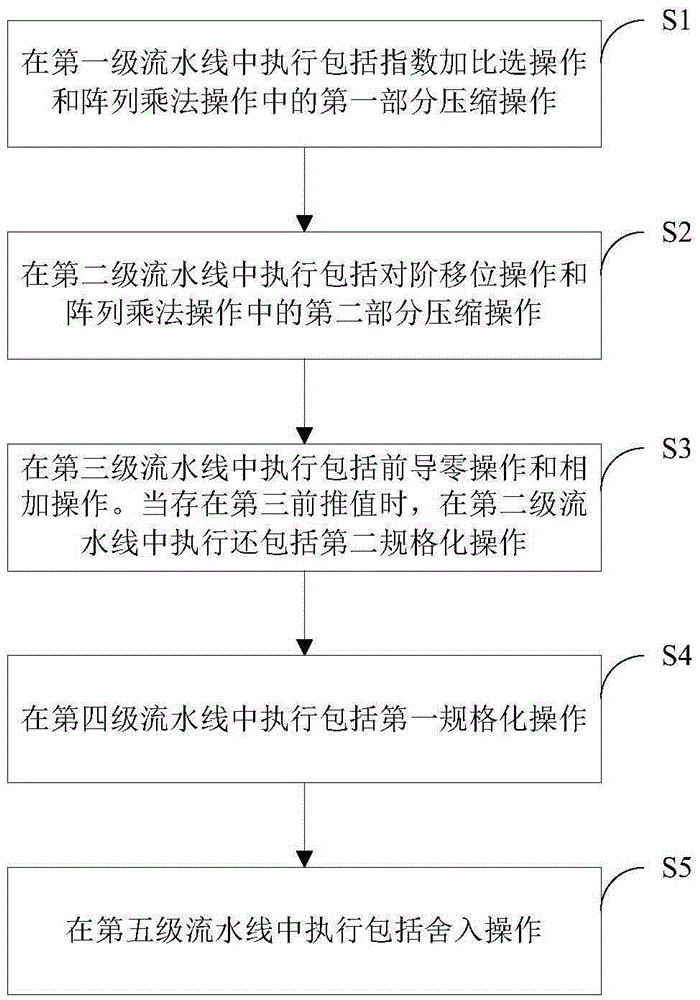

[0046] This embodiment provides a floating-point fusion multiply-add method based on internal forwarding, for example, it is applied to perform a floating-point fusion multiply-add operation in the form of B×C+A, and the floating-point fusion multiply-add operation can be one instruction (that is, the Instruction execution operation: B×C+A), may also include at least two instructions (such as instruction 1 execution operation: A2=B1×C1+A1, instruction 2 execution operation: A3=B2×C2+A2, instruction 3 execution operation : A4=B3*C3+A3, etc.), so the first product operation hereinafter is, for example, B1*C1, and the second product operation is, for example, B2*C2. Such as figure 2 As shown, the floating-point fusion multiplication-add method includes a five-stage pipeline, including the following steps:

[0047] S1. Execute the first part of compression operations including exponent addition, comparison and selection operations and array multiplication operations in the first...

Embodiment 2

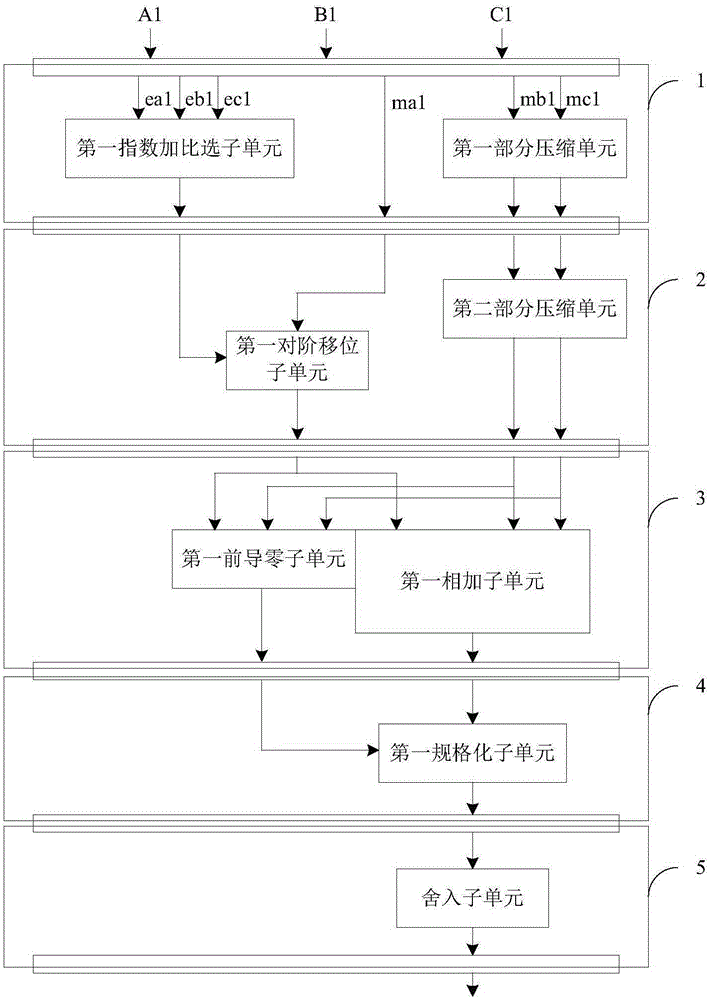

[0082] Corresponding to Embodiment 1, this embodiment provides a floating-point fusion multiplication and addition device based on internal forward push, including:

[0083] The first-stage unit 1 includes an exponent plus ratio selection unit for performing an exponent plus comparison selection operation in the first-stage pipeline and a first part of compression for performing the first part of the compression operation in the first-stage pipeline in the array multiplication operation Unit, the index addition and comparison selection unit includes a first index addition and comparison selection subunit, which is used for the exponent value of the addend in the addition operation and the first product operation when there is no first forward value or second forward value. The exponent value of the first factor and the exponent value of the second factor in the first product operation are subjected to an exponent addition ratio selection operation to generate the first control ...

Embodiment 3

[0100] This embodiment provides a processor, including the floating-point fusion multiplication and addition device in Embodiment 2.

[0101] Those skilled in the art should understand that the embodiments of the present invention may be provided as methods, systems, or computer program products. Accordingly, the present invention can take the form of an entirely hardware embodiment, an entirely software embodiment, or an embodiment combining software and hardware aspects. Furthermore, the present invention may take the form of a computer program product embodied on one or more computer-usable storage media (including but not limited to disk storage, CD-ROM, optical storage, etc.) having computer-usable program code embodied therein.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com