Light emitting diode chip and manufacturing method therefor

A technology for light-emitting diodes and a manufacturing method, which is applied to electrical components, circuits, semiconductor devices, etc., can solve the problems of low reflectivity of non-vertically incident light and low luminous efficiency of LED chips, and achieves improved stability, improved luminous brightness and luminous The effect of efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

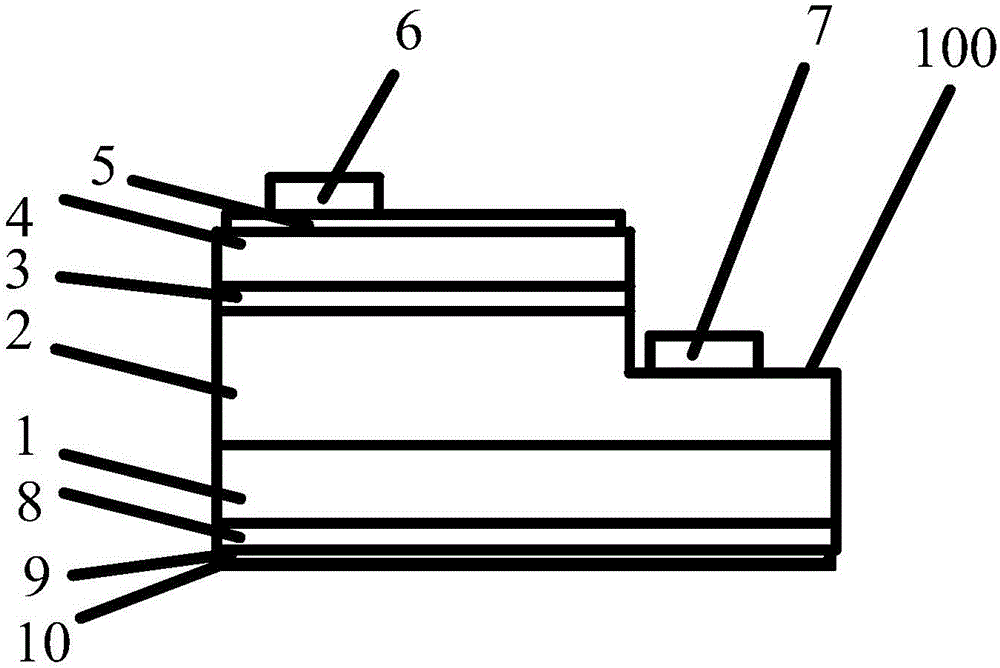

[0036] An embodiment of the present invention provides a light emitting diode chip, see figure 1 The light-emitting diode chip includes a substrate 1, an N-type layer 2, a light-emitting layer 3, a P-type layer 4, a transparent conductive film (TCO) 5, a P-type electrode 6, an N-type electrode 7, a DBR8, an Ag metal reflective layer 9 and The metal protection layer 10, the N-type layer 2, the light-emitting layer 3, and the P-type layer 4 are sequentially stacked on the first surface of the substrate 1, and the P-type layer 4 is provided with a groove extending from the P-type layer 4 to the N-type layer 2 100, the transparent conductive film 5 and the P-type electrode 6 are sequentially arranged on the P-type layer 4, the N-type electrode 7 is arranged on the N-type layer 2, and the DBR8, the Ag metal reflective layer 9, and the metal protective layer 10 are sequentially arranged on the substrate 1 The metal protective layer 10 and the DBR8 form a sealed space, the Ag metal r...

Embodiment 2

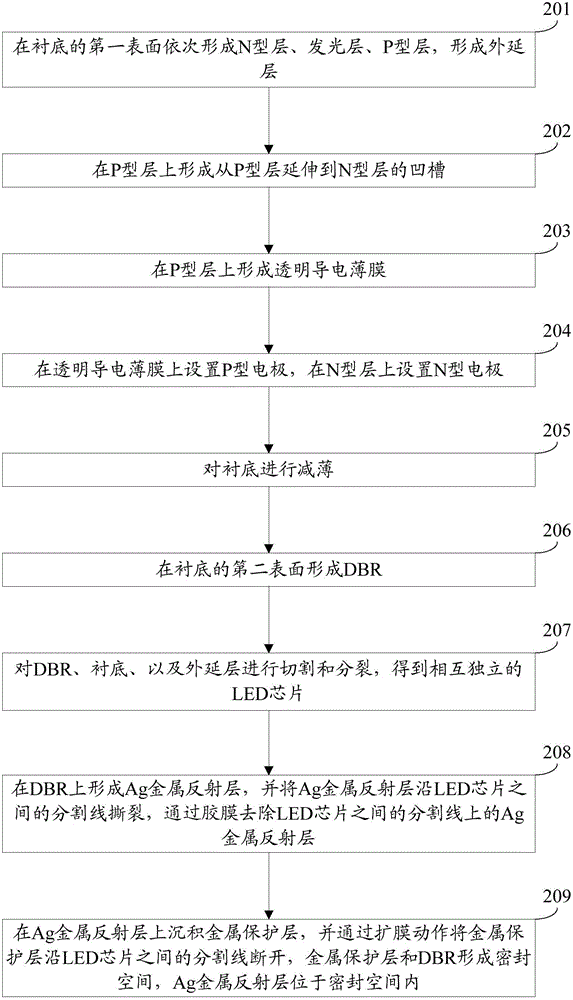

[0048] An embodiment of the present invention provides a method for manufacturing a light emitting diode chip, see figure 2 , the production method includes:

[0049] Step 201: sequentially forming an N-type layer, a light-emitting layer, and a P-type layer on the first surface of the substrate to form an epitaxial layer.

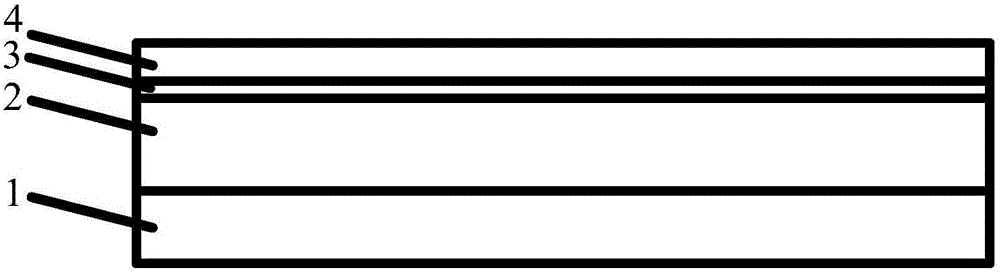

[0050] Figure 3a It is a schematic structural diagram of the LED chip after step 201 is performed. Wherein, 1 is a substrate, 2 is an N-type layer, 3 is a light-emitting layer, and 4 is a P-type layer.

[0051]In this embodiment, the N-type layer may be an N-type GaN layer, the light emitting layer may be alternately stacked InGaN layers and GaN layers, and the P-type layer may be a P-type GaN layer.

[0052] Optionally, the substrate can be one of a flat-surfaced sapphire substrate, a patterned sapphire substrate (Patterned Sapphire Substrate, PSS for short), a Si substrate, a GaN substrate, a SiN substrate, a SiC substrate, and a glass substrate. , ...

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap