Repairing method of retention time violation

A technology of hold time and repair method, applied in special data processing applications, instruments, electrical digital data processing and other directions, can solve problems such as hold time violation, space insertion buffer unit, and complete hold time violation repair, so as to reduce the impact, Eliminate the effect of overlapping cells

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

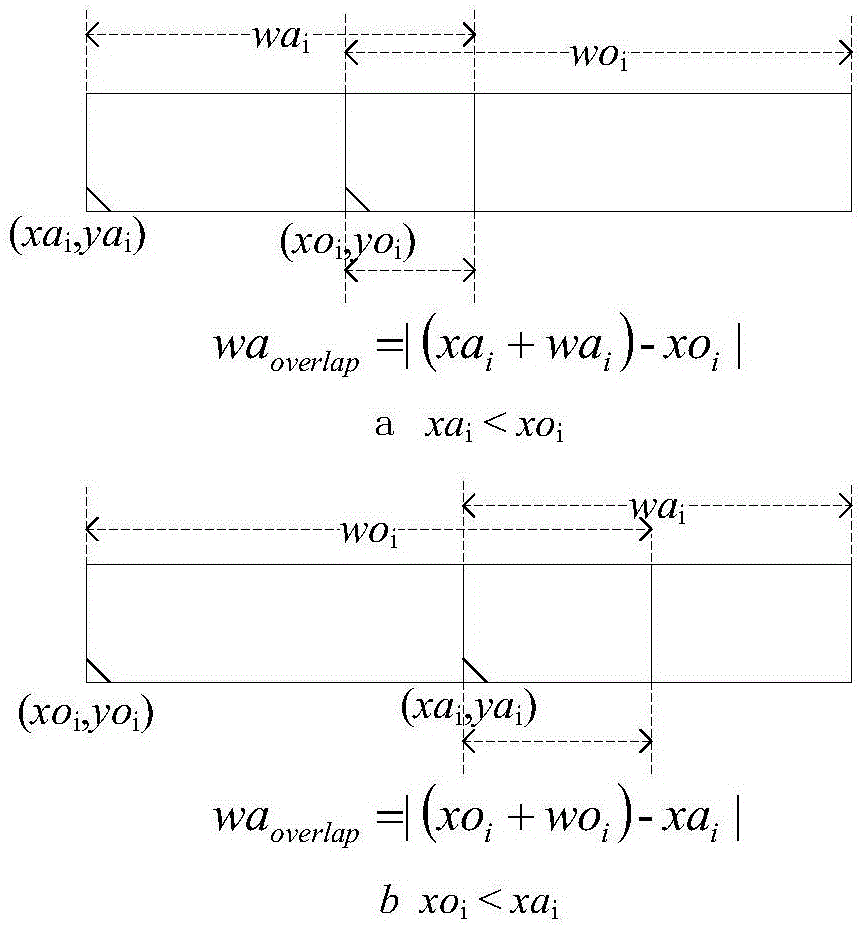

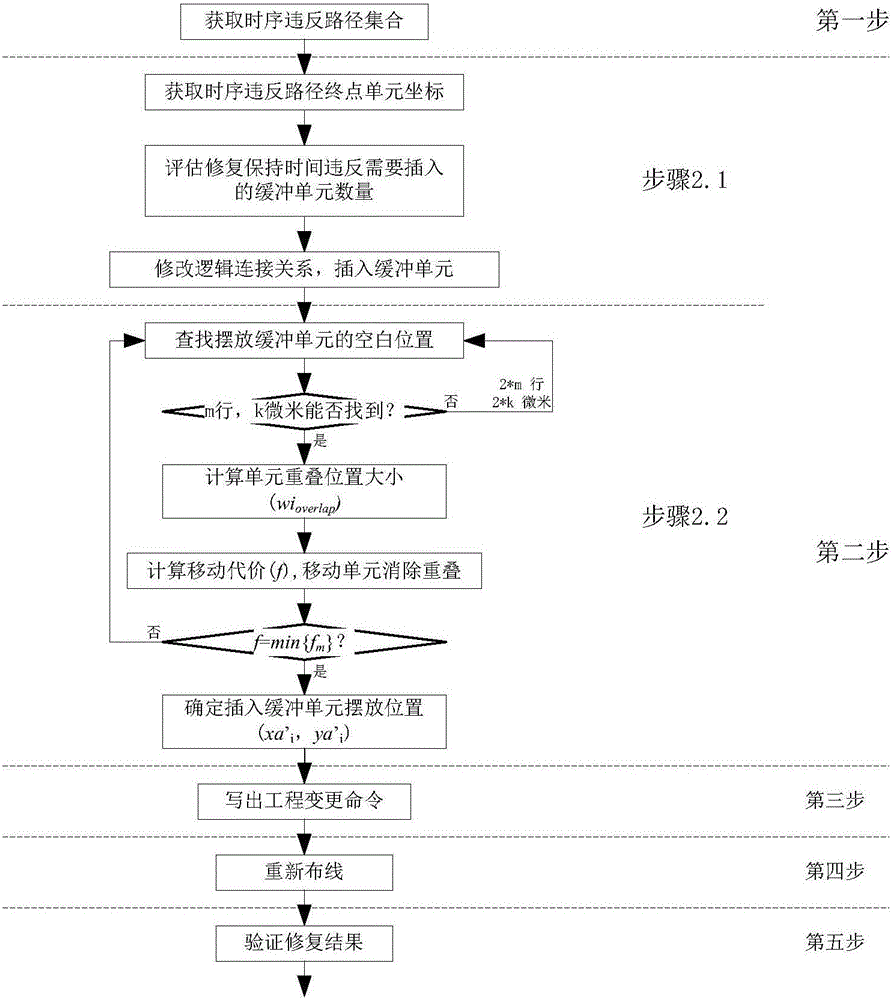

[0054] Such as image 3 As shown, it is a flowchart of a method for repairing a hold time violation of the present invention, and the present invention includes the following steps:

[0055] The first step is to obtain the start point, end point and violation value of the path with hold time violation from the results of static timing analysis;

[0056] 1.1 Perform static timing analysis on the results of chip physical design, and obtain path reports of hold time violations in each scenario;

[0057] 1.2 Obtain the end point of the timing violation path, the signal transition time on the interconnection line of the input terminal of the terminal unit, the load of the interconnection line of the terminal unit and the violation value from the path report;

[0058] 1.3 Merge the paths with the same end points in each scenario, and the combined timing violation value is the maximum violation value in all scenarios, which is recorded as t i , to cover hold violations for all scen...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More