An evaluation method of a chip power consumption evaluation platform

A power consumption and chip technology, applied in the evaluation field of chip power consumption evaluation platform, can solve the problems of reducing large-scale SOC simulation time, large server computing load, etc., to achieve the effect of reducing verification simulation time, reducing invalid access, and shortening simulation time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

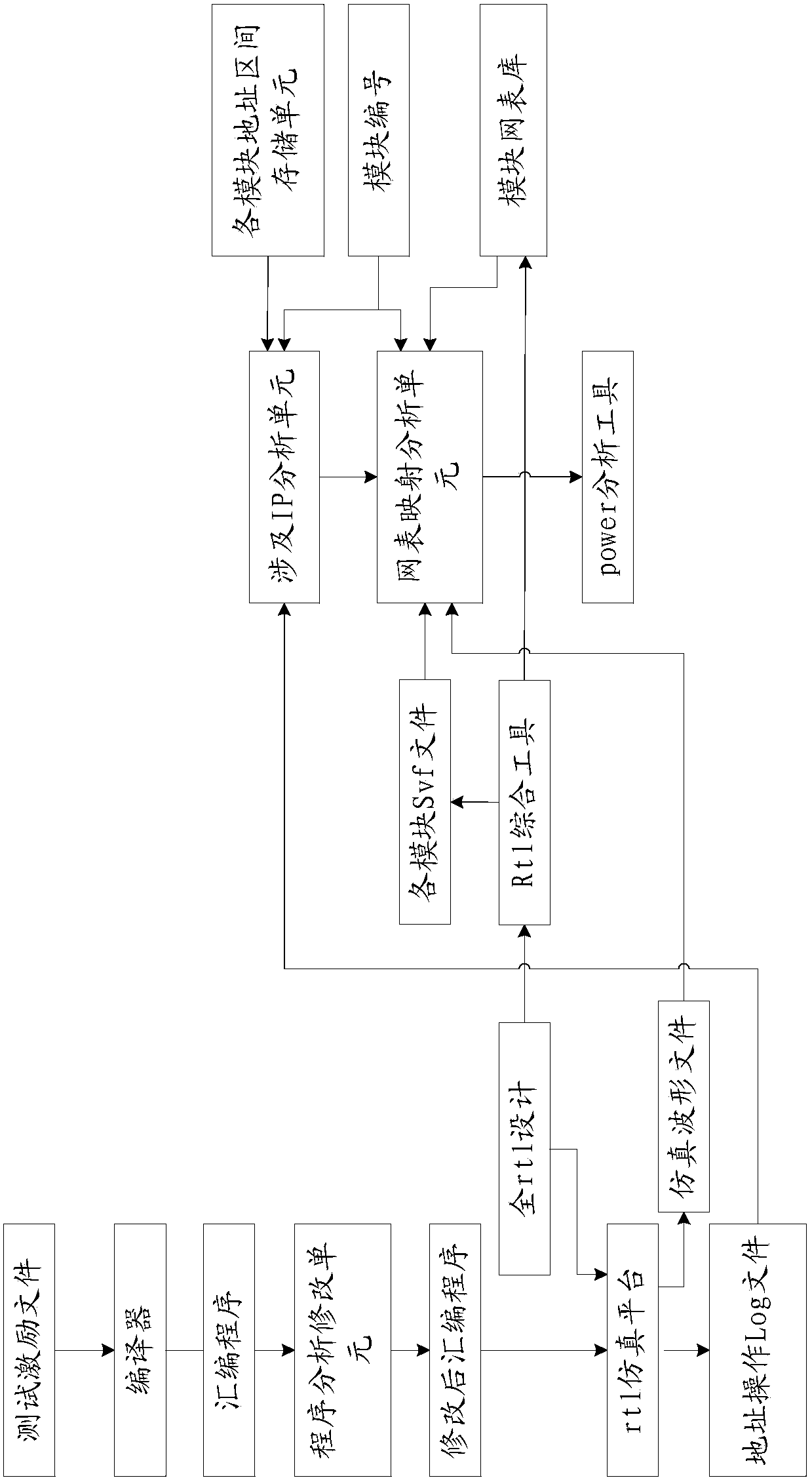

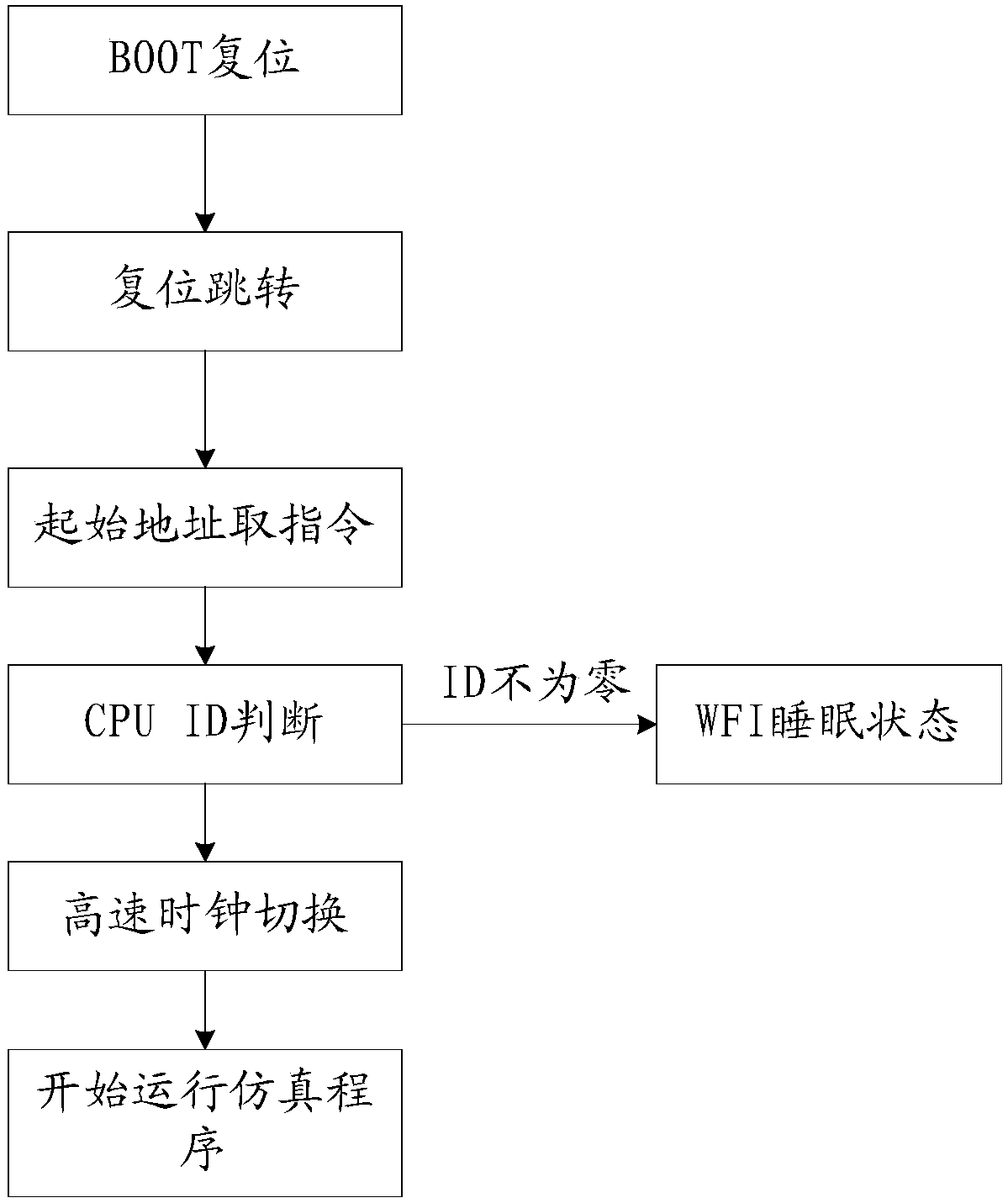

[0026] Such as figure 1 Shown, the evaluation method of the chip power consumption evaluation platform of the present invention, this chip power consumption evaluation platform consists of figure 1 The evaluation method needs to perform rtl synthesis on the rtl design according to the modules before the simulation. The synthesis tool is Design compiler. After the synthesis, the netlist of all accessible modules and the svf of all accessible modules are generated. The file, among which, the svf file is a file used to describe the mapping relationship in the process of converting rtl into netlist, and records the conversion and optimization process of synthesis tools from rtl to netlist. This file can be used for rtl design and netlist design Mapping analysis of corresponding points in .

[0027] The assessment methods then include:

[0028] Step 1, store all c program codes that the CPU in the SOC chip prepares to run in the test by a test encouraging c code file;

[0029] S...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More