Device and method for measuring voltage drop of chip

A measurement device and measurement method technology, applied in the field of measurement, can solve the problems of uncertain time window, inaccurate chip measurement results, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

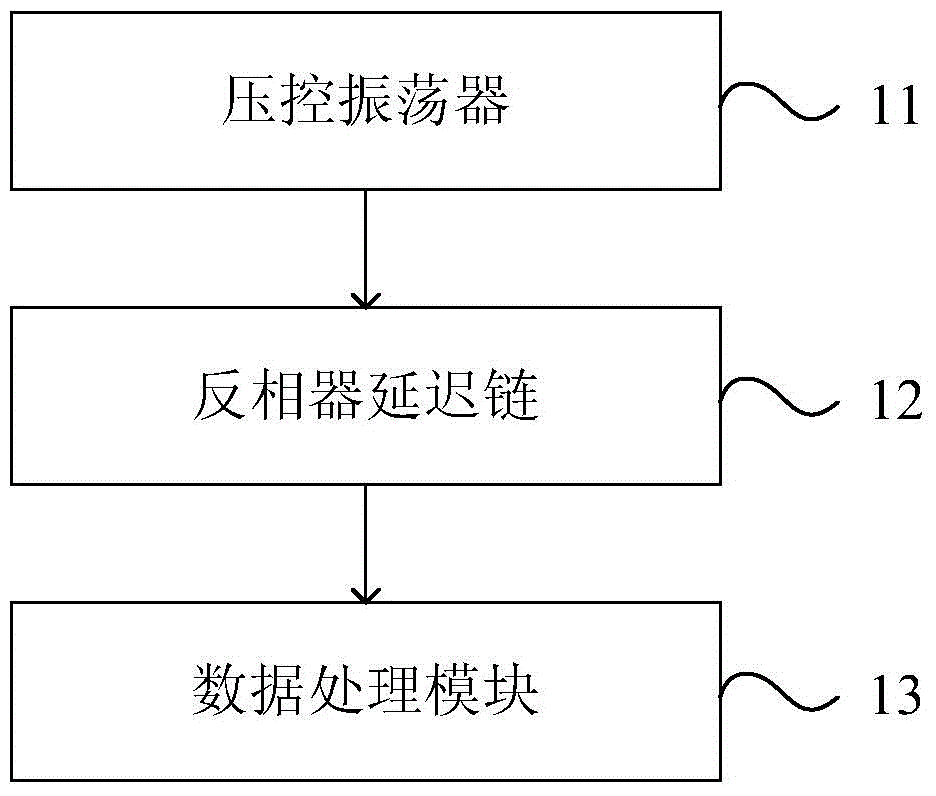

[0047] figure 1 It is a schematic structural diagram of a chip voltage drop measurement device provided by Embodiment 1 of the present invention. The measurement device provided in this embodiment is suitable for measuring the internal pressure drop of the chip. The measurement device is usually implemented by hardware and software methods, and can be integrated in the processor of the terminal device, for example, set in the processor chip, the measurement processor The internal voltage drop of the chip. Such as figure 1 As shown, the measurement device of this embodiment may include: a voltage controlled oscillator 11, an inverter delay chain 12 and a data processing module 13 provided in the chip.

[0048] The voltage controlled oscillator 11 is used to generate a clock signal, wherein when the voltage drop of the chip changes, the frequency of the clock signal generated by the voltage controlled oscillator 11 changes with the change of the voltage drop of the chip.

[0049] Th...

Embodiment 2

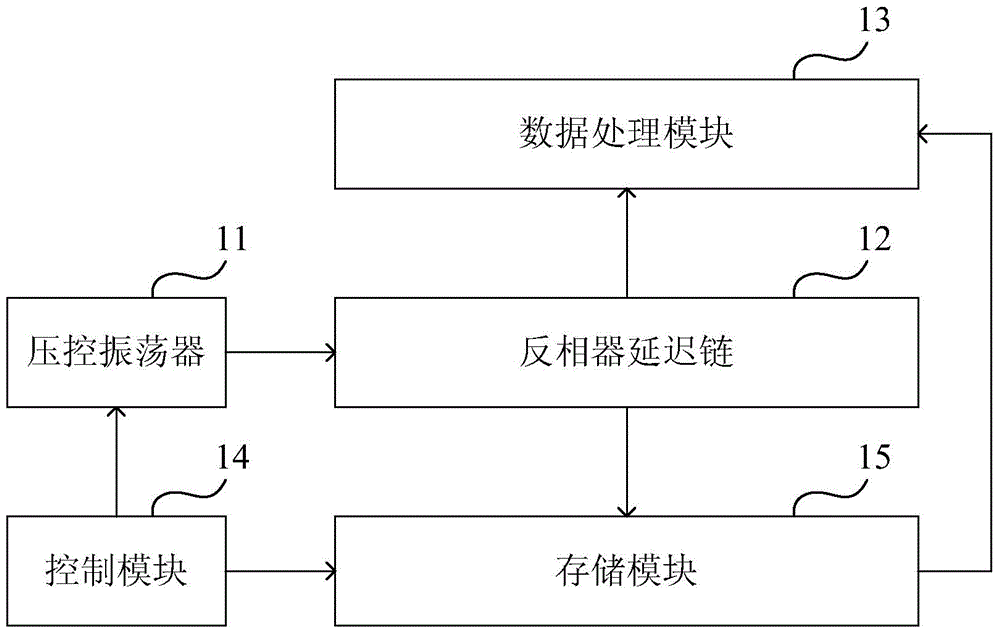

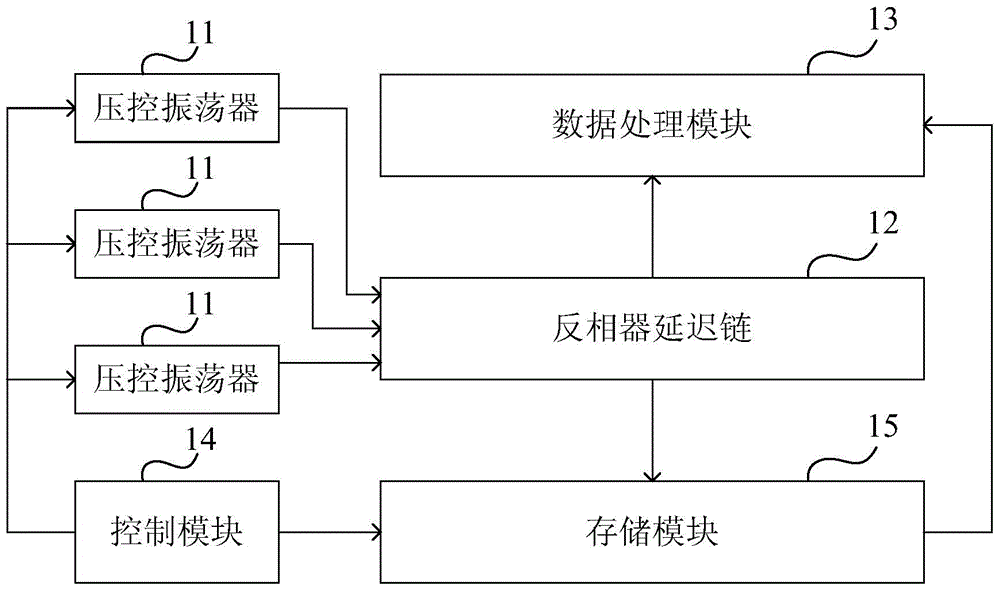

[0068] figure 2 It is a schematic structural diagram of a device for measuring the voltage drop of a chip provided in the second embodiment of the present invention. In the above figure 1 On the basis of the device shown, in the measuring device provided in this embodiment, the inverter delay chain 12 is also used to measure the voltage-controlled oscillator 11 generated by the chip at different operating voltages when the chip is not in operation. The frequency of the clock signal to obtain the curve model of the frequency of the clock signal and the operating voltage; correspondingly, the data processing module 13 is also used to obtain the frequency of the clock signal and the curve according to the current measurement of the inverter delay chain 12 Model to obtain the chip voltage drop at the current frequency.

[0069] In this embodiment, the reference value of the chip voltage drop can be measured in advance to obtain the true value of the chip voltage drop when measuring ...

Embodiment 3

[0094] Figure 4 This is a flowchart of a method for measuring the voltage drop of a chip provided in the third embodiment of the present invention. The measurement method provided in this embodiment is suitable for measuring the internal voltage drop of a chip. The method can be performed by a device for measuring the voltage drop of a chip provided in the chip. The device is usually implemented by hardware and software methods, including interconnected The voltage controlled oscillator and inverter delay chain can be integrated in the processor of the terminal device, for example, set in the processor chip to measure the internal voltage drop of the processor chip. Such as Figure 4 As shown, the measurement method of this embodiment may include:

[0095] S110: The voltage controlled oscillator generates a clock signal whose frequency changes with the voltage drop of the chip according to the change of the voltage drop of the chip.

[0096] The voltage-controlled oscillator that...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com