Packaging structure comprising interconnected embedded chips and flip chips and manufacturing method of packaging structure

A flip-chip, packaging structure technology, applied in semiconductor/solid-state device manufacturing, electrical components, electrical solid-state devices, etc., can solve the problems of incomplete utilization of packaging space, limited number of chip packages, and increased number of chip packages

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

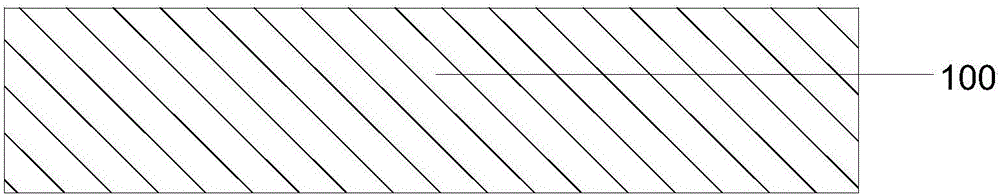

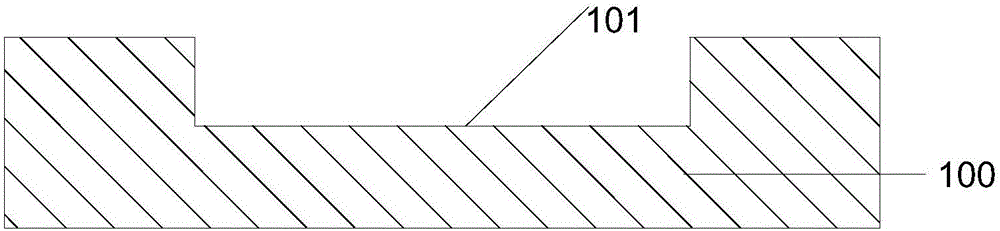

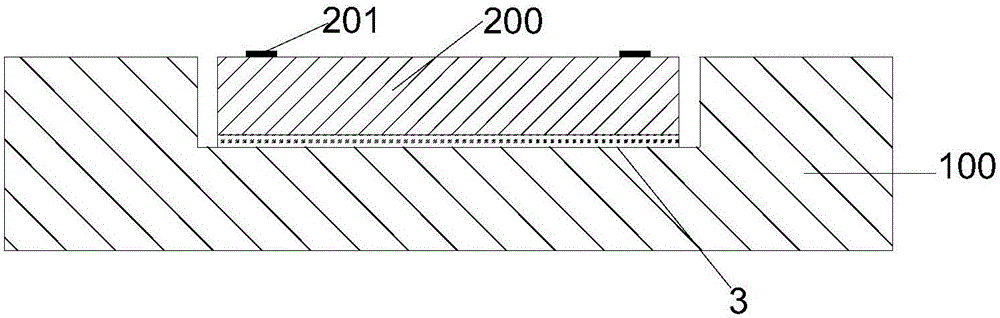

[0047] Such as Figures 1 to 10 As shown, it is the process flow of the manufacturing method of the packaging structure including embedded chips and flip-chip interconnections of the present invention. Such as Figure 10 As shown, a schematic diagram of a packaging structure including embedded chips and flip-chip interconnection in the present invention, the packaging structure includes a silicon substrate 100, and at least one groove 101 is formed on the silicon substrate 100, at least one chip and one The function side of 200 is buried in the groove 101 facing upward. The embedded chip 1 200 forms a plane close to the surface of the silicon substrate 100, and an insulating layer 103 is formed on the plane, and at least one rewiring layer 204 is formed on the insulating layer 103, and at least one chip 2 300 is flip-chip interconnected. On the plane, a first conductive structure 206 is also formed on the plane. The advantage of this is that the packaging volume is small, t...

Embodiment 2

[0063] Such as Figure 11 The structure diagram of another embodiment of the present invention is different from Embodiment 1 in that the flip-chip that is electrically interconnected with the embedded chip and the silicon substrate is two chips: chip three 400 and chip four 500 .

[0064] Preferably, the functions of the chips to be bonded may be the same or different, or not completely the same.

Embodiment 3

[0066] Such as Figure 12 The structure schematic diagram of an embodiment of the present invention is different from the above embodiment in that the groove embedded in the chip is not rectangular.

PUM

Login to view more

Login to view more Abstract

Description

Claims

Application Information

Login to view more

Login to view more - R&D Engineer

- R&D Manager

- IP Professional

- Industry Leading Data Capabilities

- Powerful AI technology

- Patent DNA Extraction

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic.

© 2024 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap