A kind of floating gate flash memory and its preparation method

A floating gate type, floating gate technology, applied in semiconductor devices, electrical components, circuits, etc., can solve the problems affecting the isolation of floating gate and word line, affecting the performance of the device, and achieve the effect of reducing thickness and improving programming efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0039] In the following description, numerous specific details are given in order to provide a more thorough understanding of the present invention. Of course, the present invention can also have other embodiments besides these detailed descriptions.

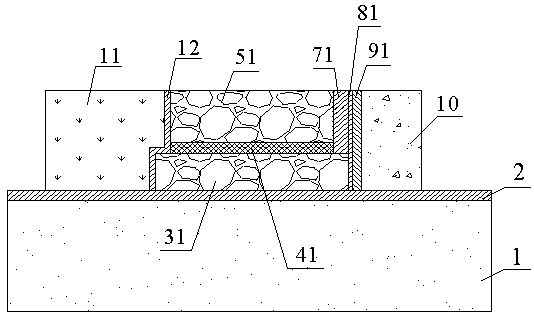

[0040] Floating gate flash memory provided by the present invention can refer to figure 1 shown, including:

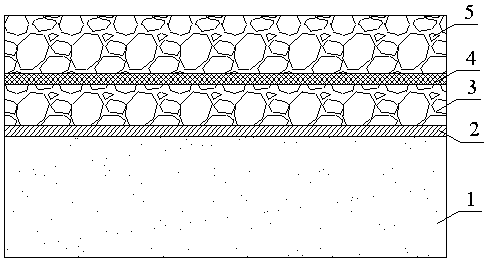

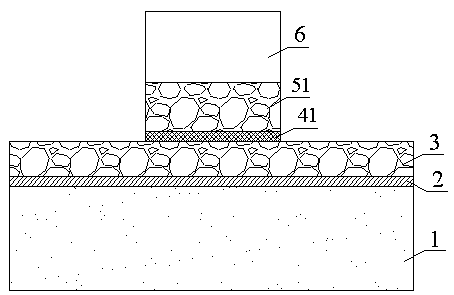

[0041] Substrate 1 (preferably silicon substrate) and tunnel oxide layer 2, floating gate (FG) 31, insulating layer (preferably silicon oxide / nitrogen Silicon oxide / silicon oxide insulating layer, that is, ONO layer) 42 and control gate (CG) 51; the drain (as the word line WL of the floating gate flash memory) 10, which is arranged on the tunnel oxide layer 2 adjacent to the floating gate 31 , and a silicon nitride isolation film 91 is provided between the drain 10 and the floating gate 31; the erasure gate (EG) 11 is provided on the tunnel oxide layer 2 and is located on the side of the floating gate 31 away from the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More