A Programmable Trimming Circuit of Output Port of Multiplexing Chip

An output port and circuit trimming technology, which is applied in the fields of logic circuit coupling/interface, logic circuit, logic circuit connection/interface layout, etc. using field effect transistors, can solve minor problems, save packaging costs and improve parameters The effect of precision and product yield

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

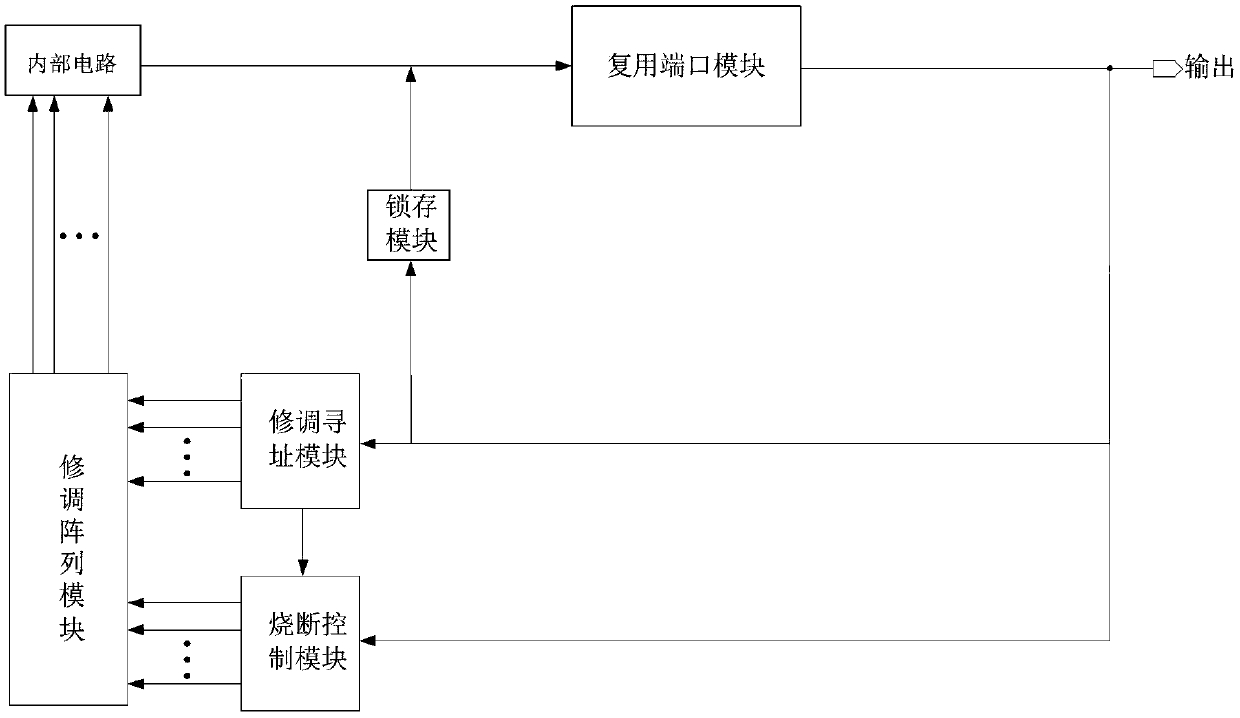

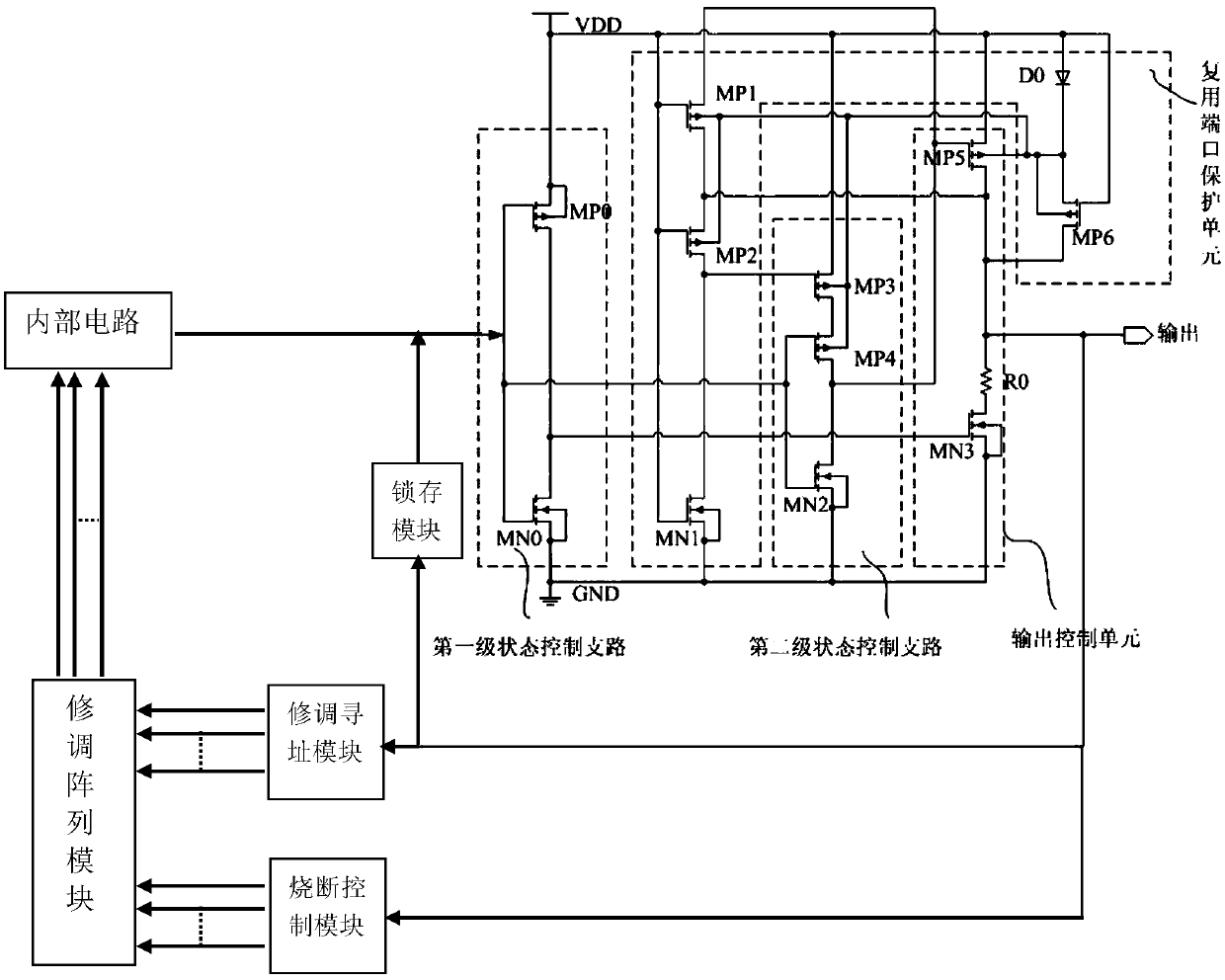

[0043] Such as figure 1 As shown, a programmable trimming circuit for output port of multiplexing chip, including internal circuit, multiplexing port module, latch module, trimming addressing module, burnout control module, trimming array module;

[0044] The internal circuit is the main circuit used to realize the function and performance of the chip, and the output terminal of the internal circuit is connected to the multiplexing port module;

[0045] The output ports of the multiplexing port module are respectively connected to the latch module, the trimming addressing module and the burnout control module, and are used to multiplex the output port of the chip as a trimming input port for outputting addressing signals and blown out signals , and respectively transmit the addressing signal to the latch module and the trimming addressing module, and transmit the blown signal to the blown control module;

[0046] The output terminal of the latch module is connected to the out...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More