Instruction prefetching method based on Cortex-M series processor and circuit

An instruction prefetching and processor technology, applied in CAD circuit design, electrical digital data processing, special data processing applications, etc., can solve the problems of poor NVM memory performance and low instruction execution efficiency of processors, and achieve instruction execution. The effect of improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] Specific embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings.

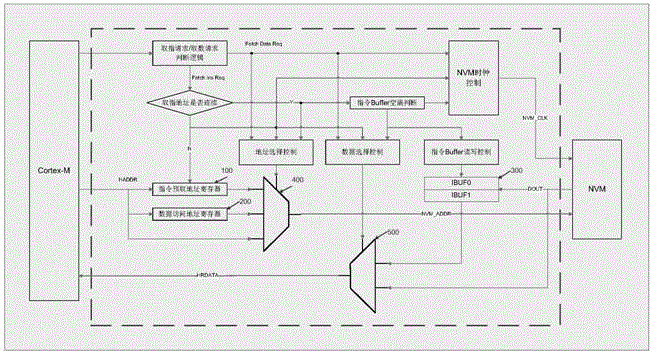

[0019] Such as figure 1 As shown in the schematic diagram of the hardware circuit, 100 represents the instruction prefetch address register, 200 represents the data access address register, 300 represents two sets of 32Bit instruction buffers (IBUF0 and IBUF1), 400 represents the address path selector, and 500 represents the data path selector .

[0020] figure 1 100 in represents the instruction prefetch address register, which is reset to all zeros when the chip is powered on, and the register is in an invalid state. When the instruction fetch address of the processor is not continuous with the address of the previous instruction fetch operation, the instruction prefetch address register should be updated with the new address, and the instruction buffer corresponding to 300 should be cleared at the same time.

[0021] figure 1 The 200...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More