A Method of Accelerating Routing

A wiring method and wiring technology, applied in the FPGA field, can solve problems such as wasting time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0029] The technical solutions of the present invention will be described in further detail below with reference to the accompanying drawings and embodiments.

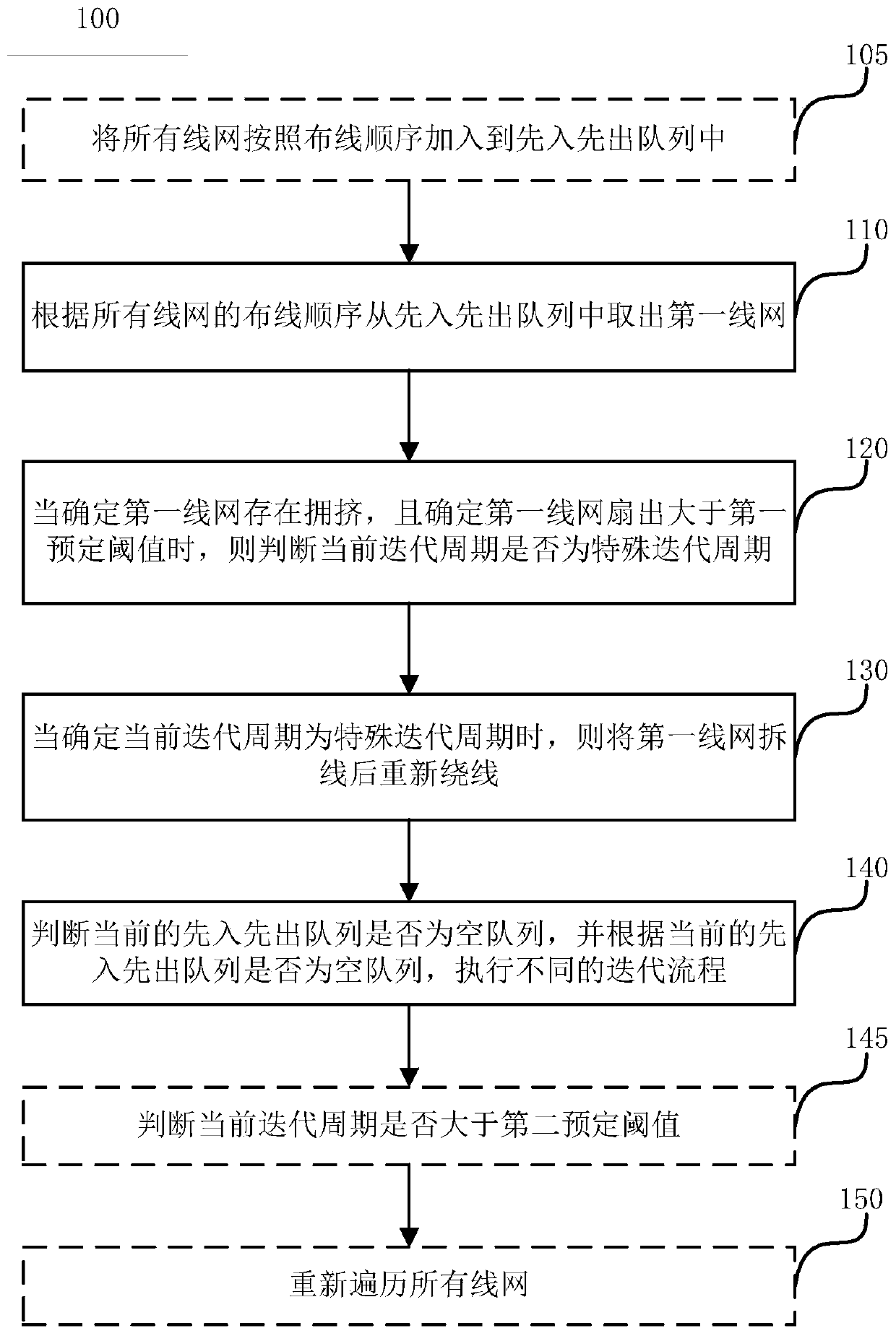

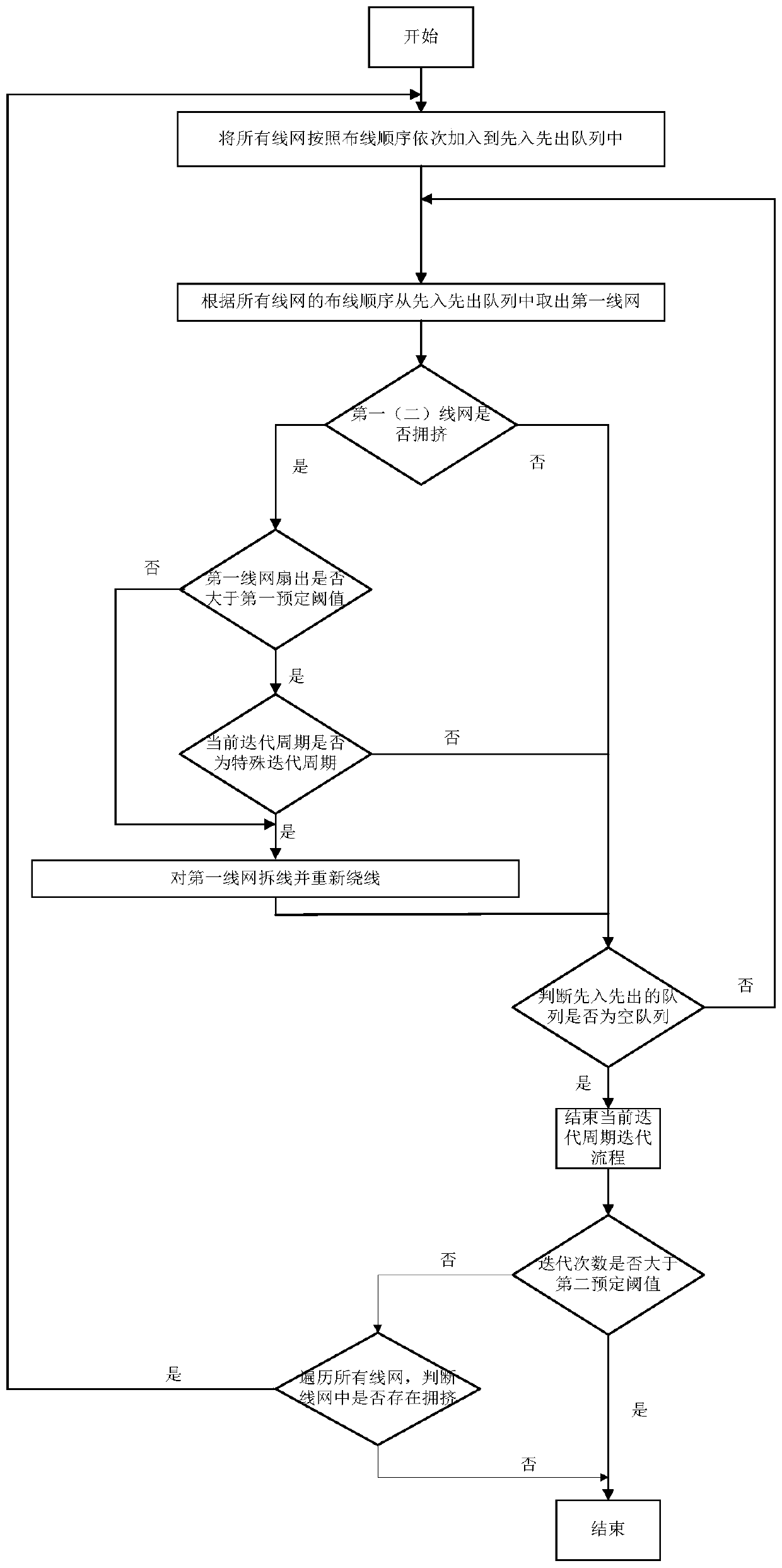

[0030] figure 1 A schematic flowchart 100 of a method for accelerating wiring provided by an embodiment of the present invention. As shown in Figure 1, the method includes:

[0031] Step 110, taking out the first net from the first-in-first-out queue according to the wiring sequence of all nets.

[0032] Specifically, the first net is taken out from the first-in-first-out queue according to the wiring sequence. It should be understood that the first net here does not specifically refer to the first net added to the queue in terms of order. Rather, it is the net whose routing order is prioritized relative to other nets contained in the current FIFO queue.

[0033] Optionally, before step 110, the method may actually include step 105, adding all wire nets to a first-in-first-out queue sequentially according to the wi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More