Shift register and driving method thereof, gate driving circuit, and display device

A shift register and driving signal technology, applied in static memory, digital memory information, instruments, etc., can solve problems such as abnormal display, keeping low potential, and unstable pull-up nodes

- Summary

- Abstract

- Description

- Claims

- Application Information

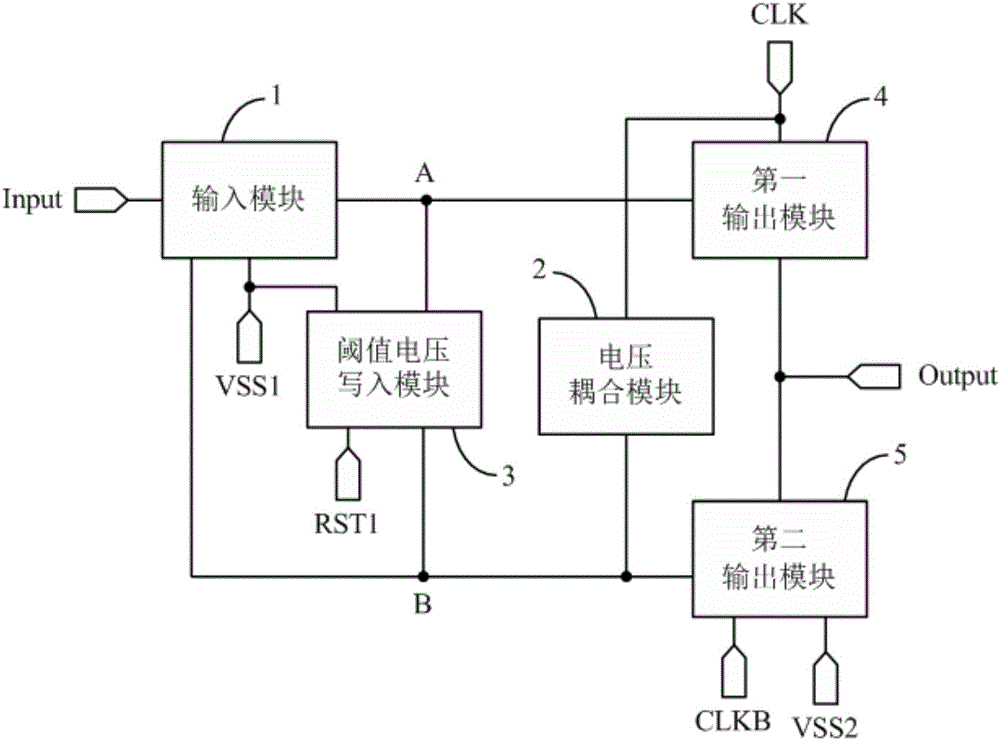

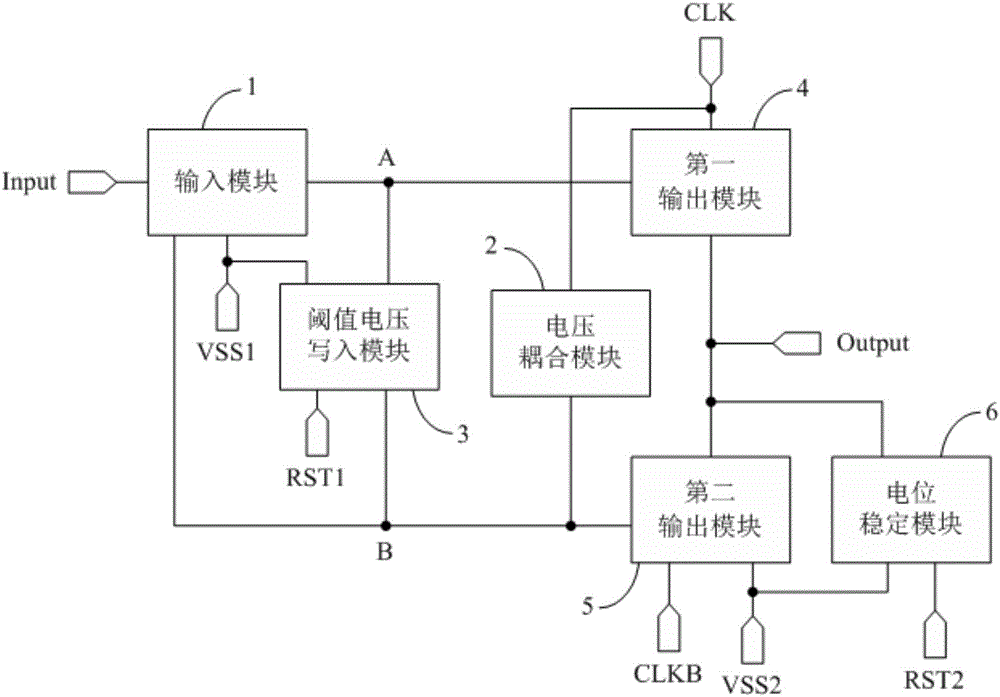

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

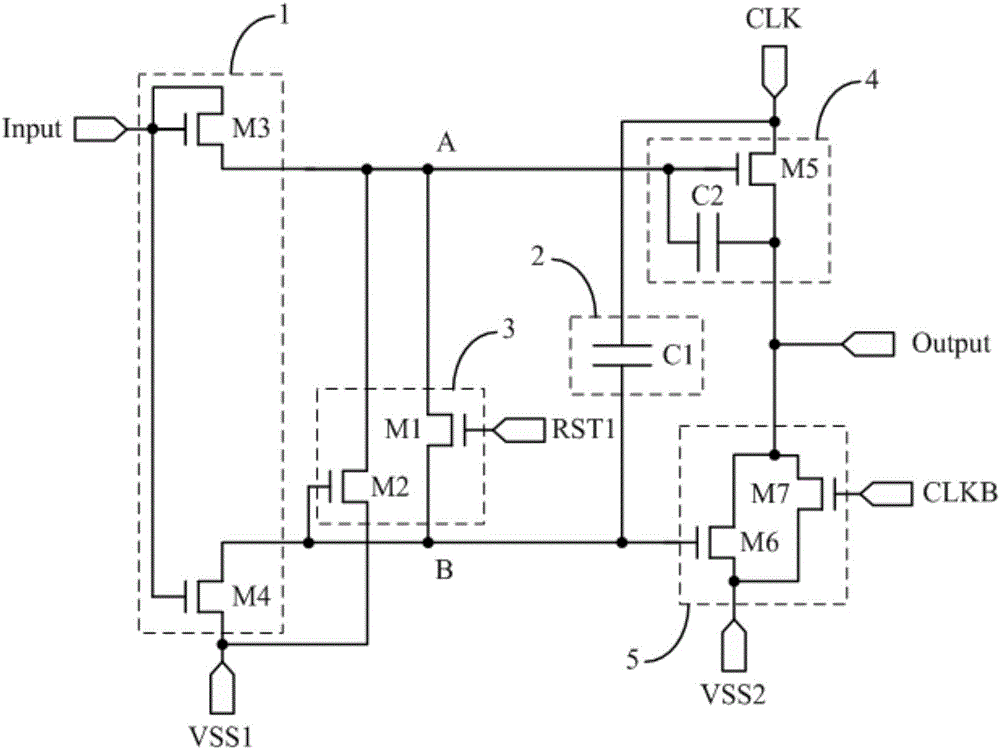

Embodiment 1

[0108] by Figure 2a The structure of the shift register shown is taken as an example to describe its working process, wherein, in Figure 2a In the shift register shown, all the switch transistors are N-type switch transistors, and each N-type switch transistor is turned on under the action of a high potential, and is turned off under the action of a low potential; the potential of the first reference signal terminal VSS1 is a low potential, The corresponding input and output timing diagrams are as follows Figure 3a Shown, specifically, select as Figure 3a There are six stages in the shown input-output timing diagram: the first stage T1 , the second stage T2 , the third stage T3 , the fourth stage T4 , the fifth stage T5 and the sixth stage T6 .

[0109] In the first stage T1, Input=1, RST1=0, CLK=0, CLKB=1.

[0110] Since Input=1, both the third switch transistor M3 and the fourth switch transistor M4 are turned on. Since the third switching transistor M3 is turned on ...

Embodiment 2

[0123] by Figure 2b The structure of the shift register shown is taken as an example to describe its working process, wherein, in Figure 2bIn the shift register shown, all the switch transistors are N-type switch transistors, and each N-type switch transistor is turned on under the action of a high potential, and is turned off under the action of a low potential; the potential of the first reference signal terminal VSS1 is a low potential, The corresponding input and output timing diagrams are as follows Figure 3b Shown, specifically, select as Figure 3b There are six stages in the shown input-output timing diagram: the first stage T1 , the second stage T2 , the third stage T3 , the fourth stage T4 , the fifth stage T5 and the sixth stage T6 .

[0124] In the first stage T1, Input=1, RST1=0, RST2=0, CLK=0, CLKB=1. Since RST2=0, the eighth switching transistor M8 is turned off. The rest of the specific working process is the same as the working process of the first stag...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More