Apparatus and method for improving threshold voltage distribution of nonvolatile storage apparatus

A non-volatile storage and voltage distribution technology, applied in static memory, read-only memory, information storage, etc., can solve the problems of difficult control of programming time and insufficient programming efficiency of programming time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

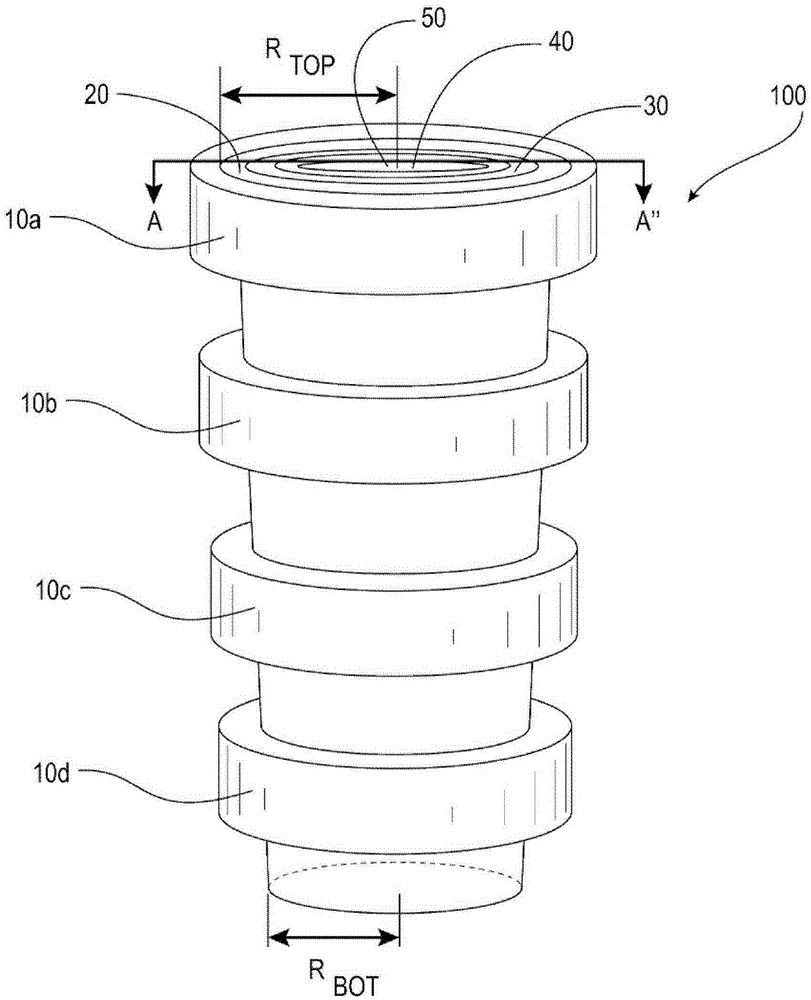

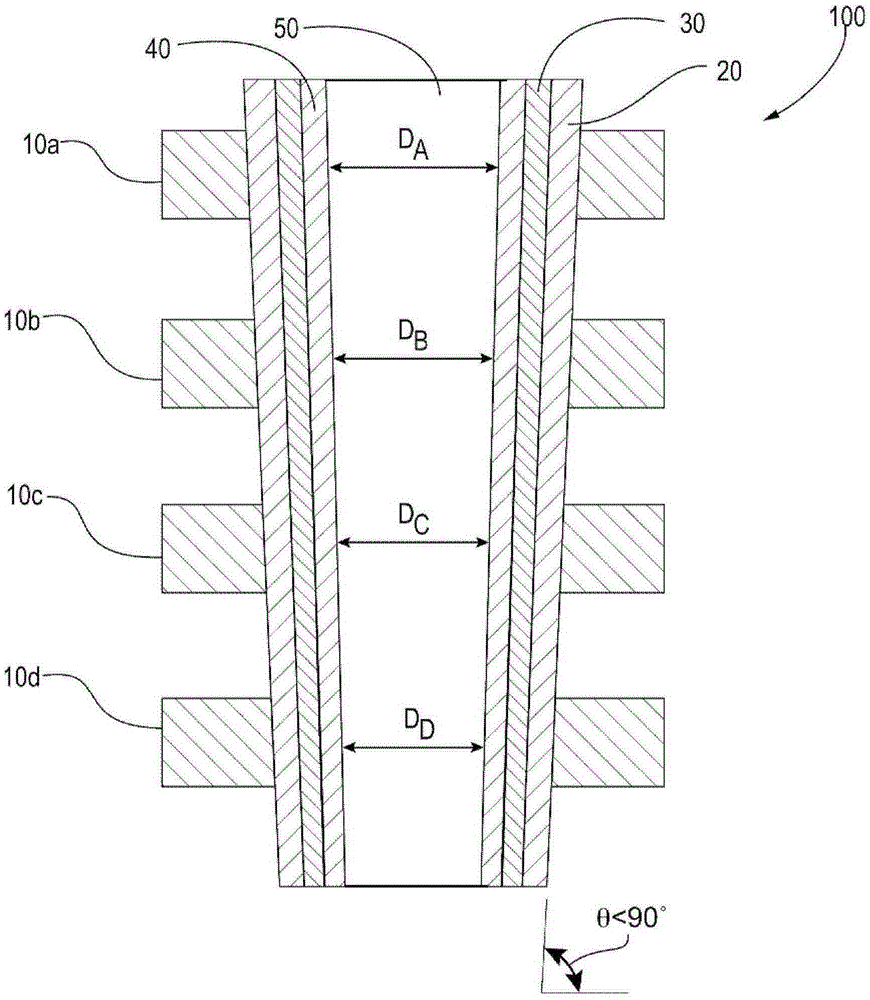

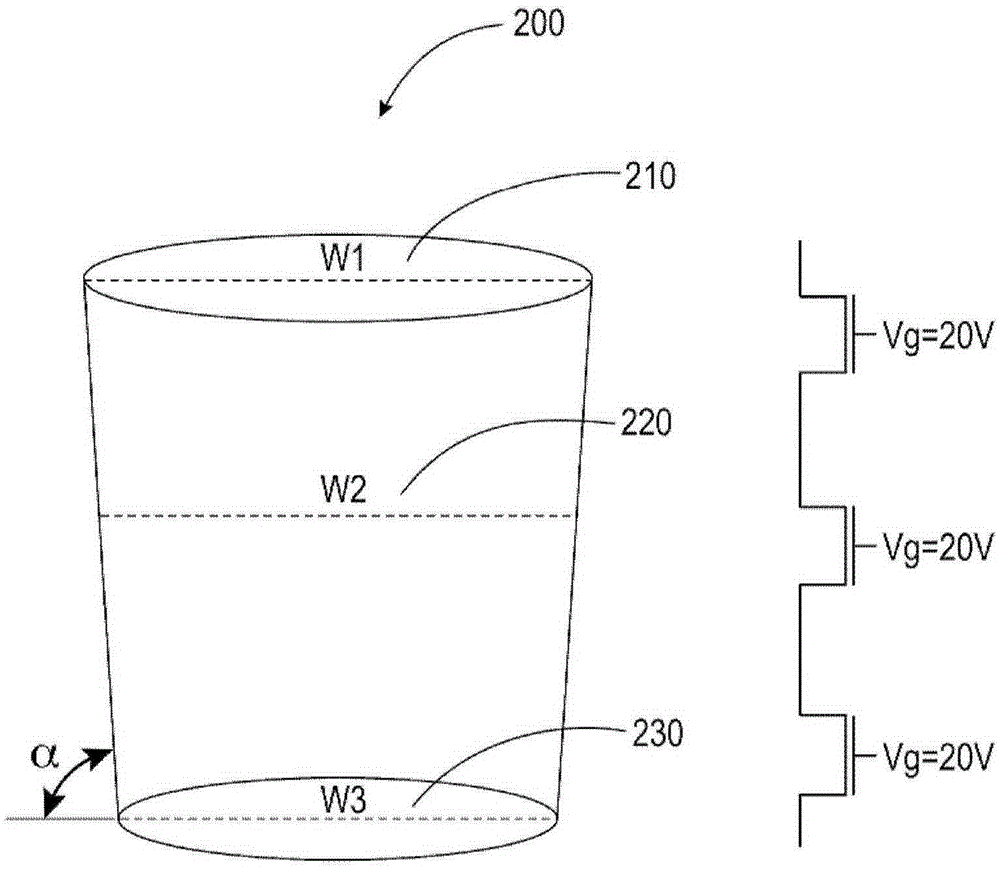

[0036] Herein, some embodiments of the present invention are described in detail with reference to the accompanying drawings, but not all embodiments are shown in the drawings. Indeed, these inventions can use many different variations and are not limited to the examples herein. Rather, the present invention provides these embodiments to meet the statutory requirements of the application. The same reference symbols are used in the drawings to designate the same or similar elements.

[0037] Although specific terms are employed herein, they are used in a generic and descriptive sense only and not for purposes of limitation. Unless defined otherwise, all terms used herein including technical and scientific terms have the same meaning as commonly understood by one of ordinary skill in the art of the invention. It will be further understood that terms such as those defined in commonly used dictionaries should be interpreted to have meanings as commonly understood by those of ord...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com