Emulator that supports eeprom power down test

An emulator and electrical testing technology, which is applied in the field of emulators, can solve the problems that the program power-down protection code cannot be debugged and tested, and cannot simulate the power-down of the product chip EEPROM, so as to improve development efficiency, facilitate development, and ensure the overall service life Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

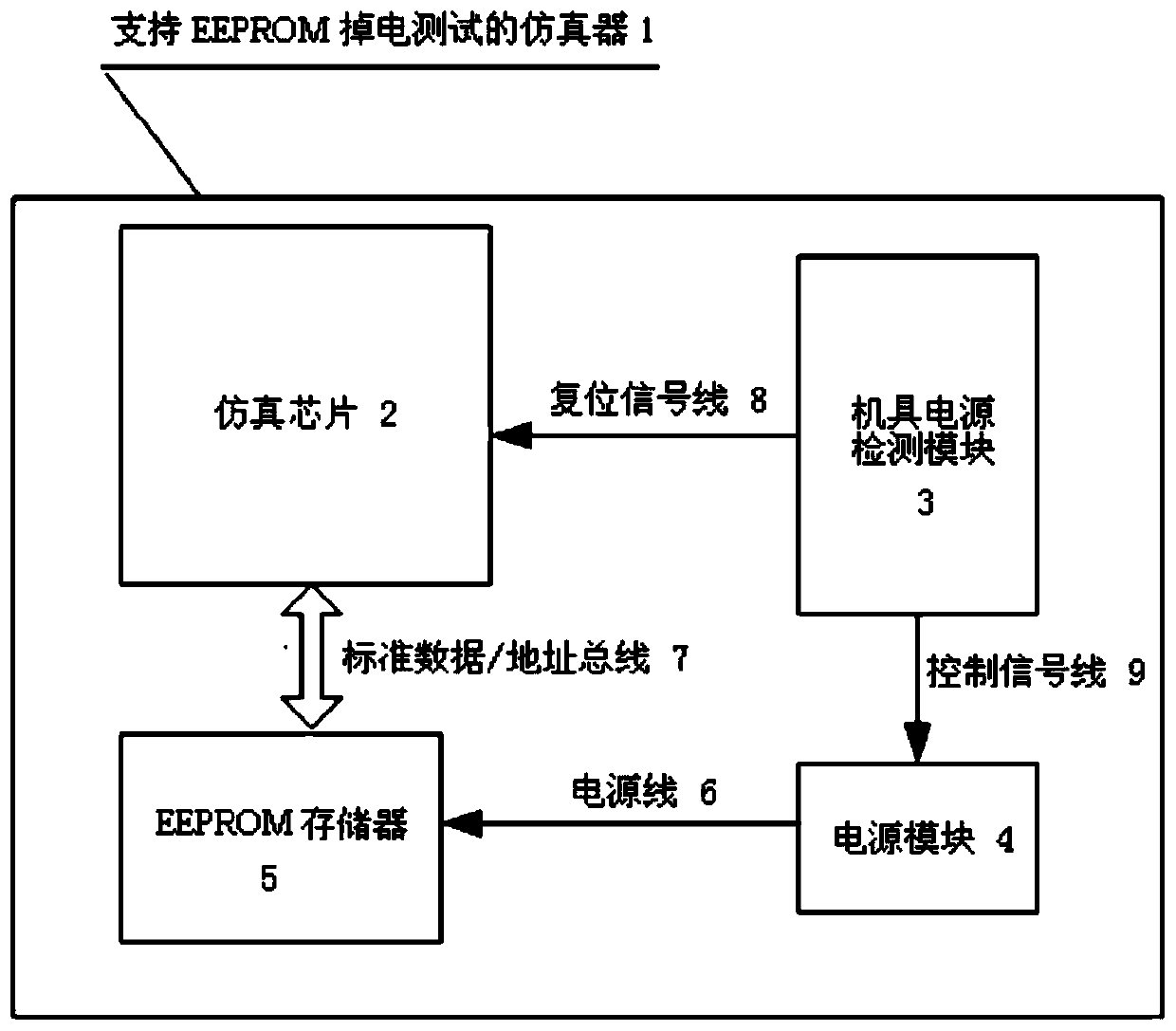

[0017] Such as figure 1 As shown, the emulator 1 supporting the EEPROM power-down test includes an emulation chip 2 , an implement power detection module 3 , a power module 4 , and an EEPROM memory 5 in the following embodiments. The emulation chip 2 is connected with the EEPROM memory 5 through the standard data / address bus 7, and is connected with the machine tool power detection module 3 through the reset signal line 8. The power supply module 4 is connected to the EEPROM memory 5 through the power line 6 , and is connected to the implement power detection module 3 through the control signal line 9 . EEPROM memory 5 is an independent chip and can be replaced.

[0018] During program debugging and testing, the emulation chip 2 can perform all EEPROM operations such as reading, writing, page erasing, chip erasing, etc. to the EEPROM memory 5 through the standard data / address bus 7, which can completely simulate the operation of the EEPROM in the product chip. various operat...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More