Patents

Literature

41 results about "SimulTrain" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

SimulTrain is a Project Management Simulator used in project management training programs. SimulTrain is a simulation of the planning and execution phases of a medium-sized project, that involves all of the events that occur.

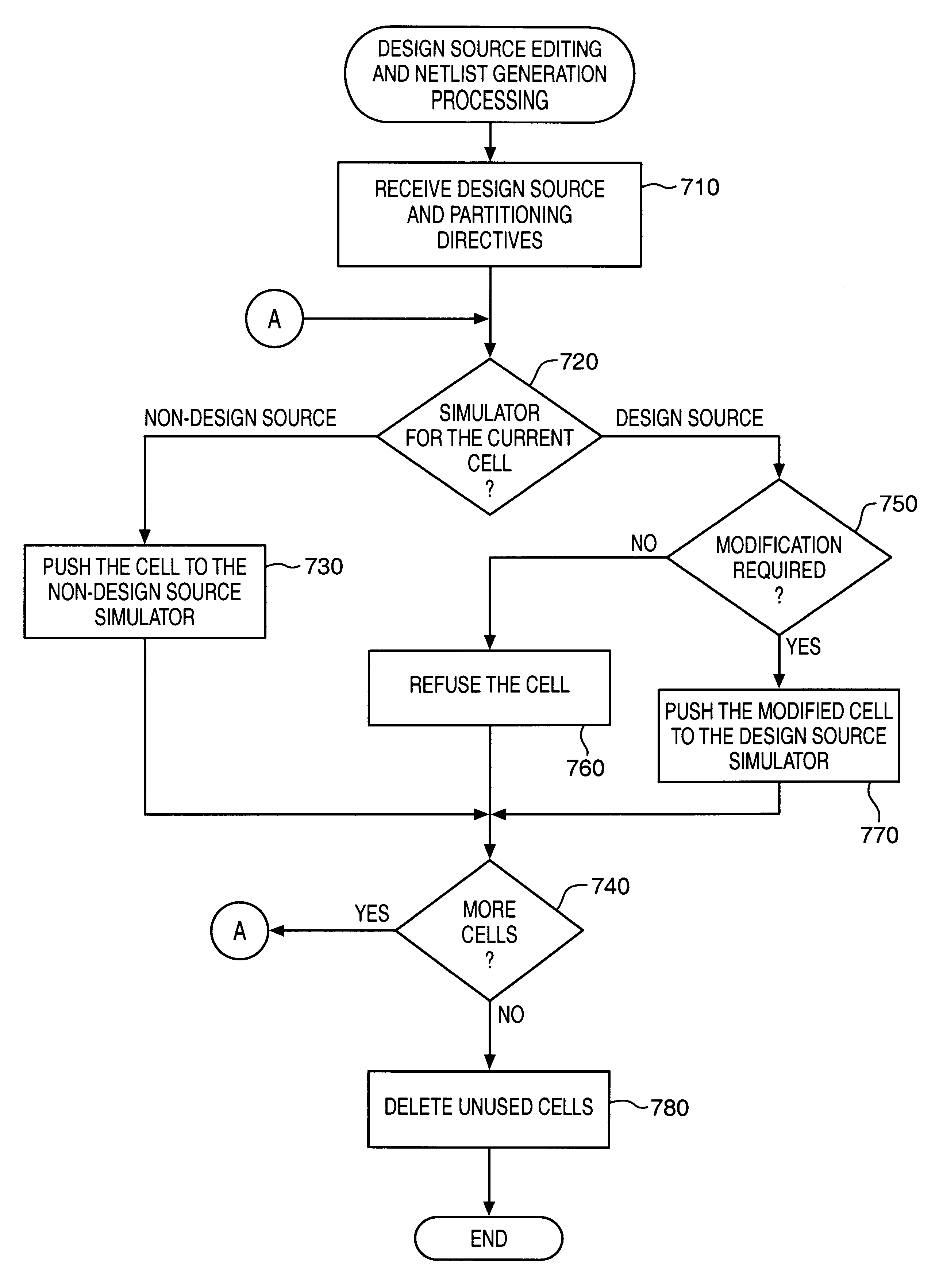

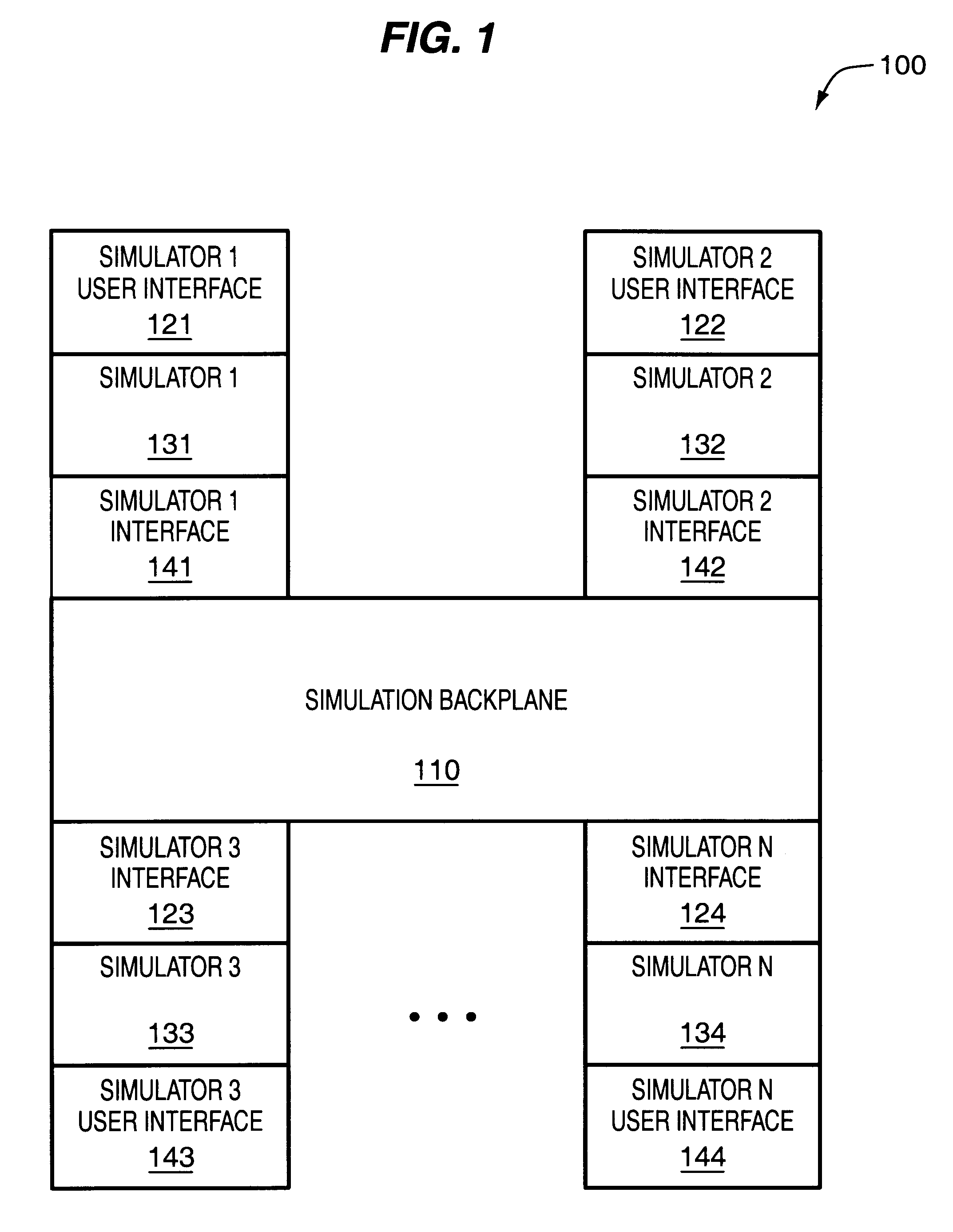

Automated design partitioning

InactiveUS6339836B1Detecting faulty computer hardwareCAD circuit designTheoretical computer scienceNetlist

A flexible and extensible automated design partitioning mechanism that facilitates simulation sessions employing two or more simulators is provided. A simulation backplane includes partitioning logic that identifies the design blocks of an overall design pertaining to each of a plurality of simulators. Once the partitions have been identified, nets that cross simulator boundaries (e.g., mixed nets) are determined and inter-simulator connectivity information is generated for the simulators. According to one aspect of the present invention, the partitioning logic is able to accomodate arbitrary (e.g., instance-based) partitioning. A design source expressed in a design representation upon which a first simulator may operate is received. Design blocks to be partitioned to each of a plurality of solvers are identified based upon one or more partitioning directives and the design source. A first instance of a cell is assigned to a first solver and a second instance of the cell is assigned to a second solver. Netlist like information is generated for those of the design blocks that are partitioned to a non-design source solver. To accomodate a folded representation of a design block containing the first or second instance of the cell, one or more additional cells are created. According to another aspect of the present invention, name space mapping is retained across all simulators. A design source upon which a first simulator may operate is read. Based upon a set of rules, a primary partition that is to be simulated by a first solver is identified. The primary partition includes a top cell of the design representation. Additionally, a secondary partition that is to be simulated by a second solver is identified. Subsequently, netlist information is generated for the second solver while retaining name space mapping in the secondary partition by adding one or more levels of hierarchy so as to include information about the top cell in the secondary partition.

Owner:MENTOR GRAPHICS CORP

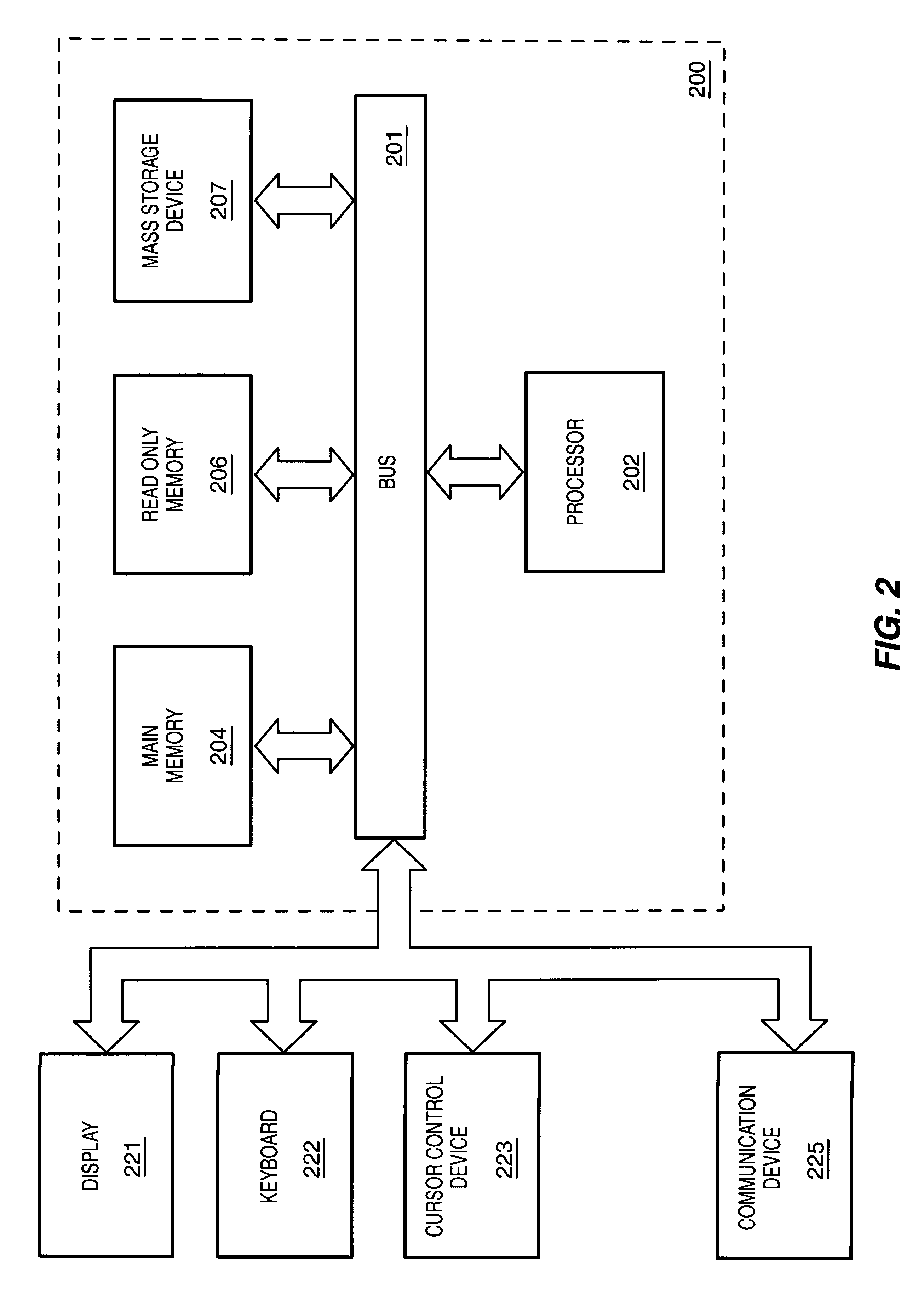

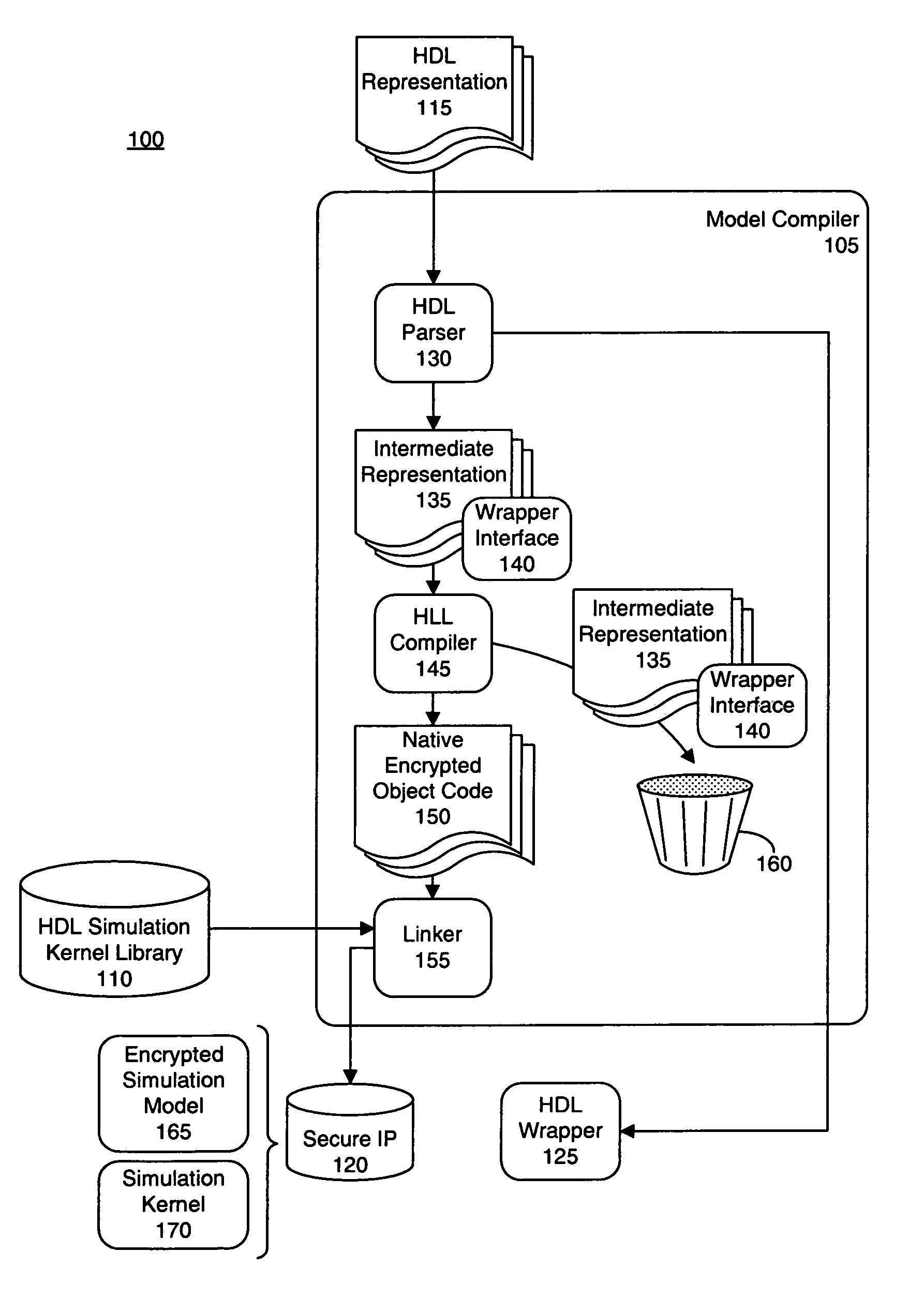

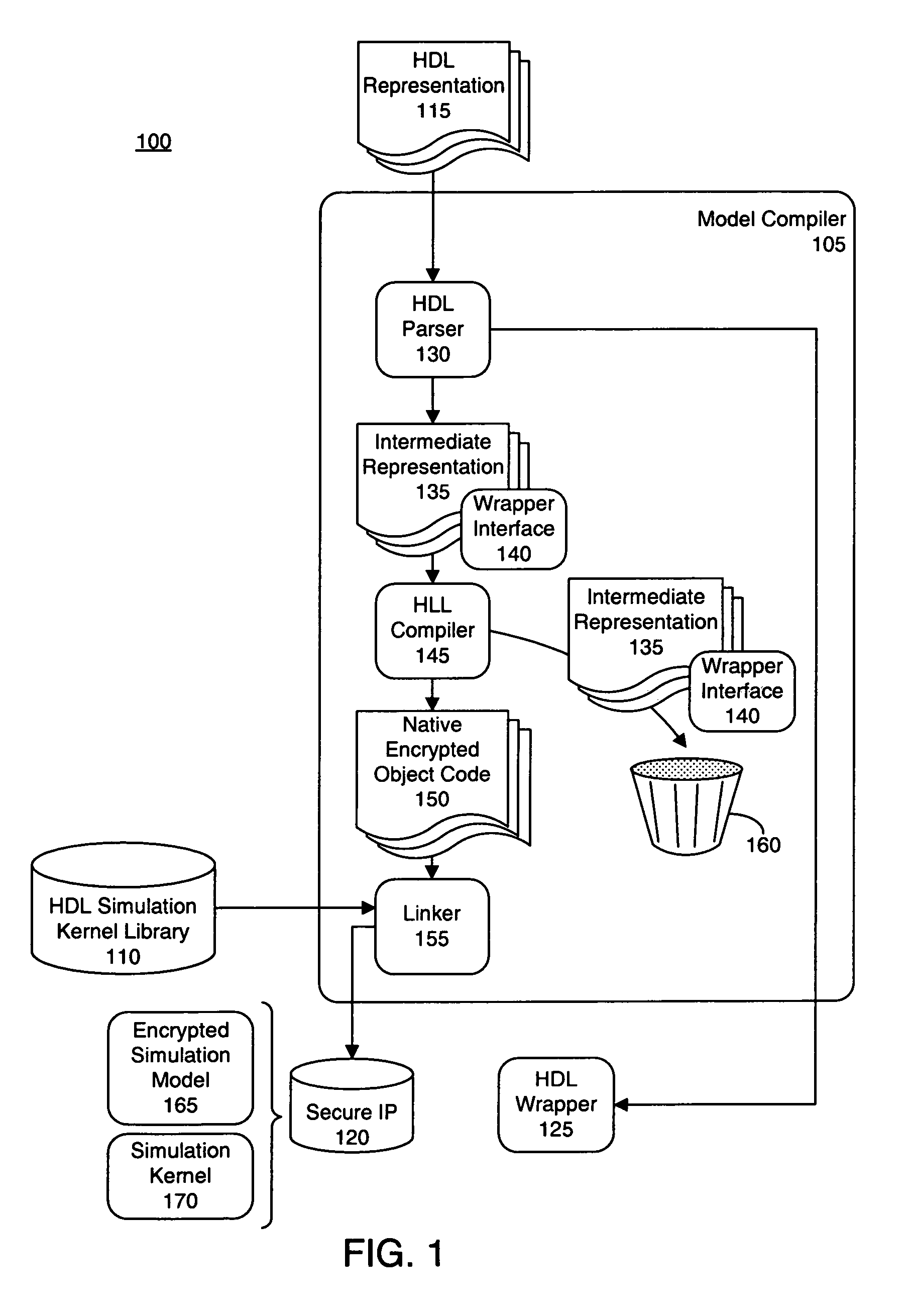

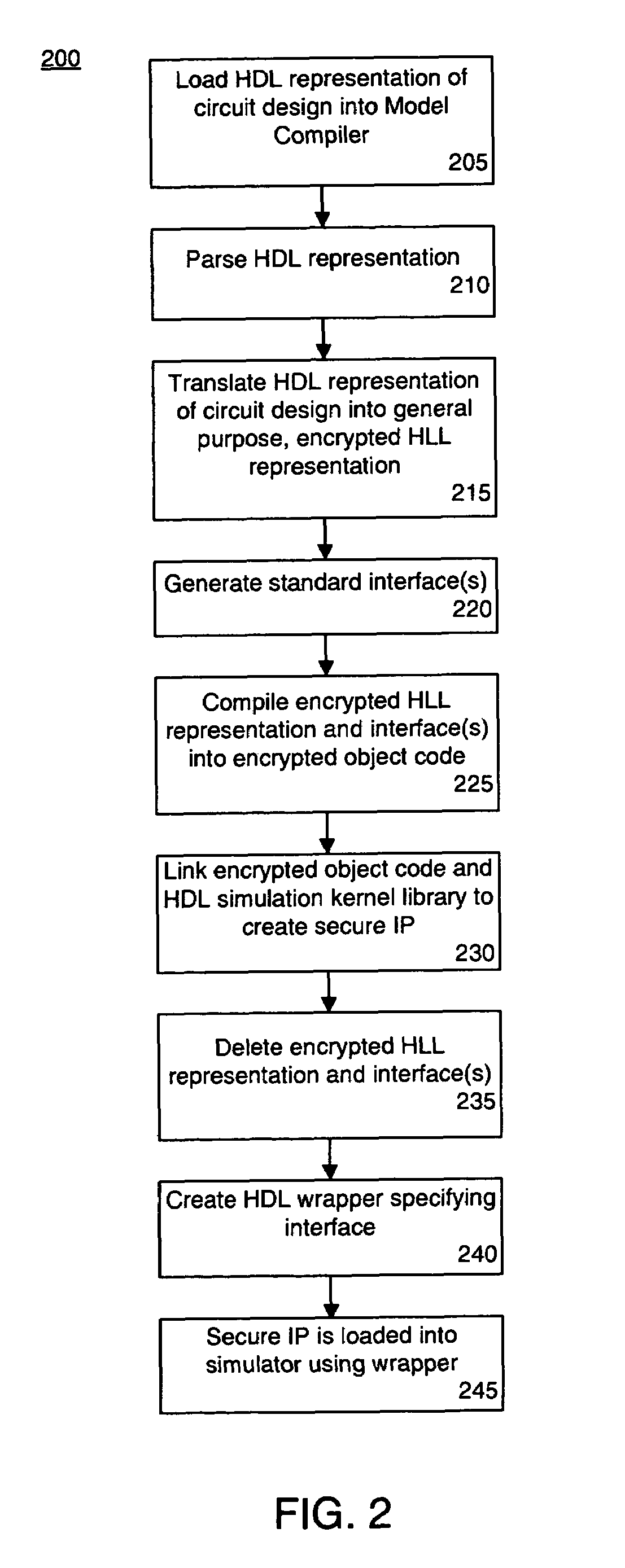

Event-driven simulation of IP using third party event-driven simulators

InactiveUS7721090B1Analogue computers for electric apparatusUnauthorized memory use protectionComputer hardwareThird party

A method of creating a secure intellectual property (IP) representation of a circuit design for use with a software-based simulator can include translating a hardware description language representation of the circuit design into an encrypted intermediate form and compiling the intermediate form of the circuit design to produce encrypted object code. The method further can include linking the encrypted object code with a simulation kernel library thereby creating the secure IP representation of the circuit design. The secure IP can include an encrypted simulation model of the circuit design and a simulation kernel configured to execute the encrypted simulation model.

Owner:XILINX INC

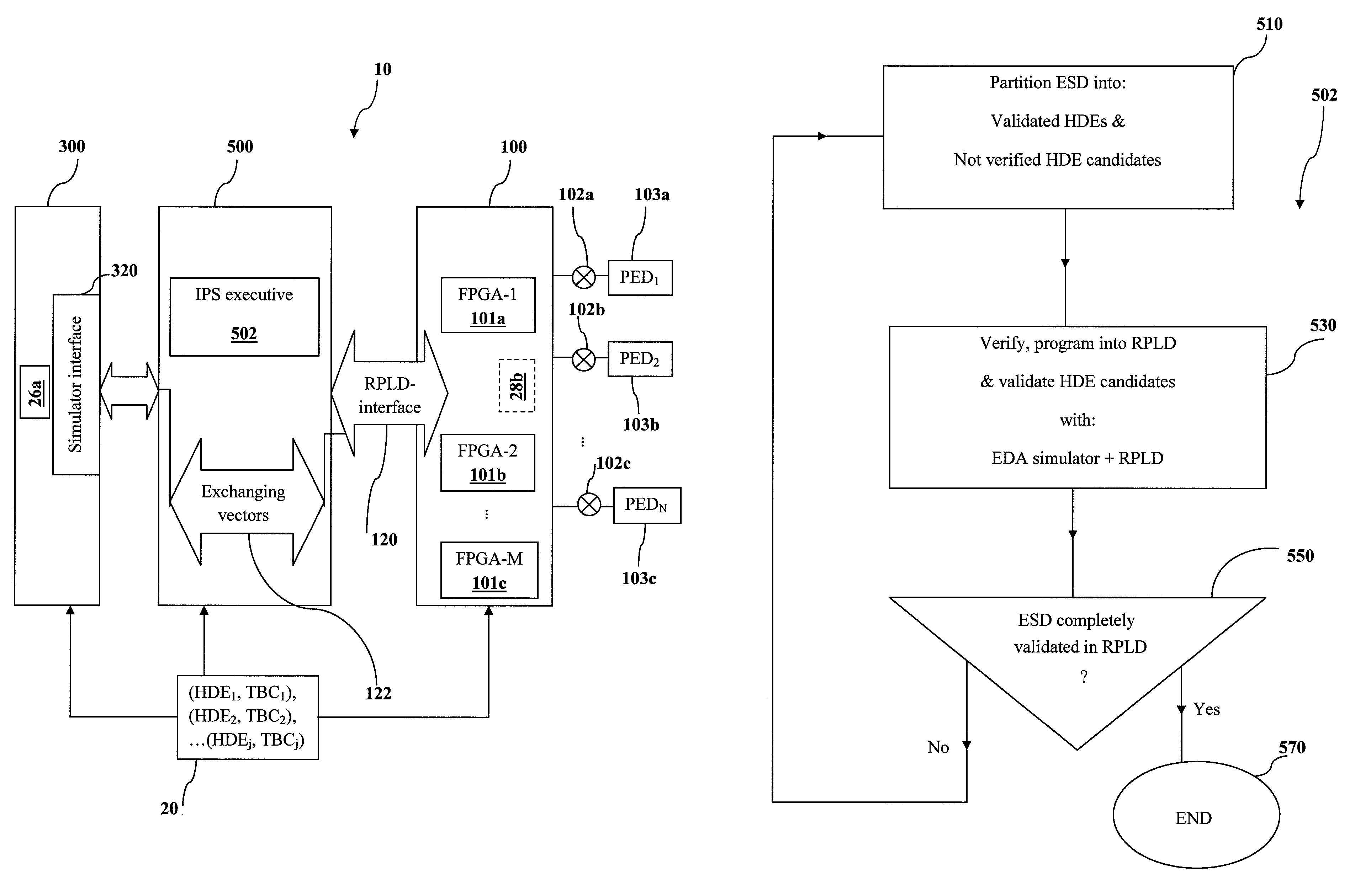

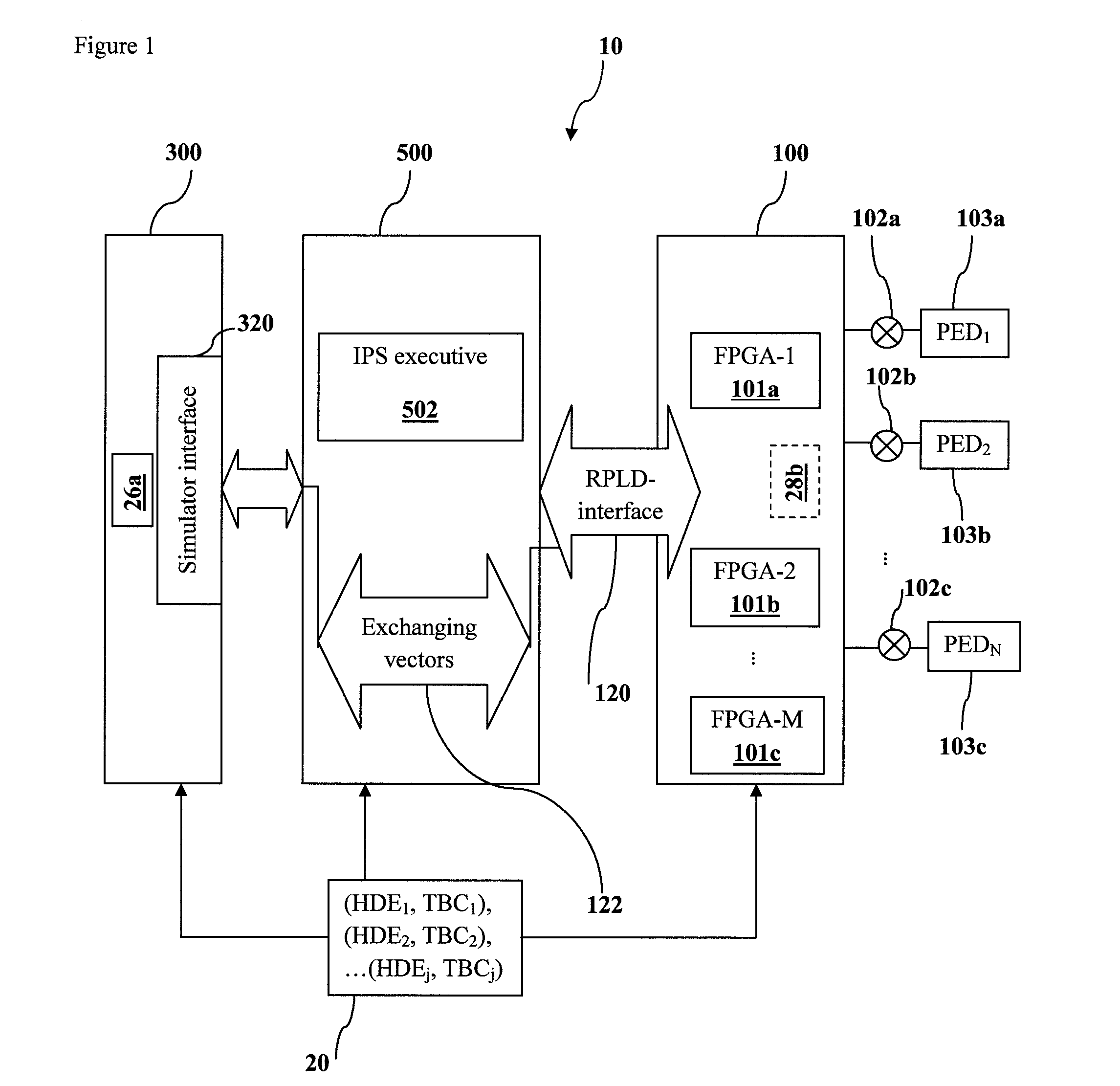

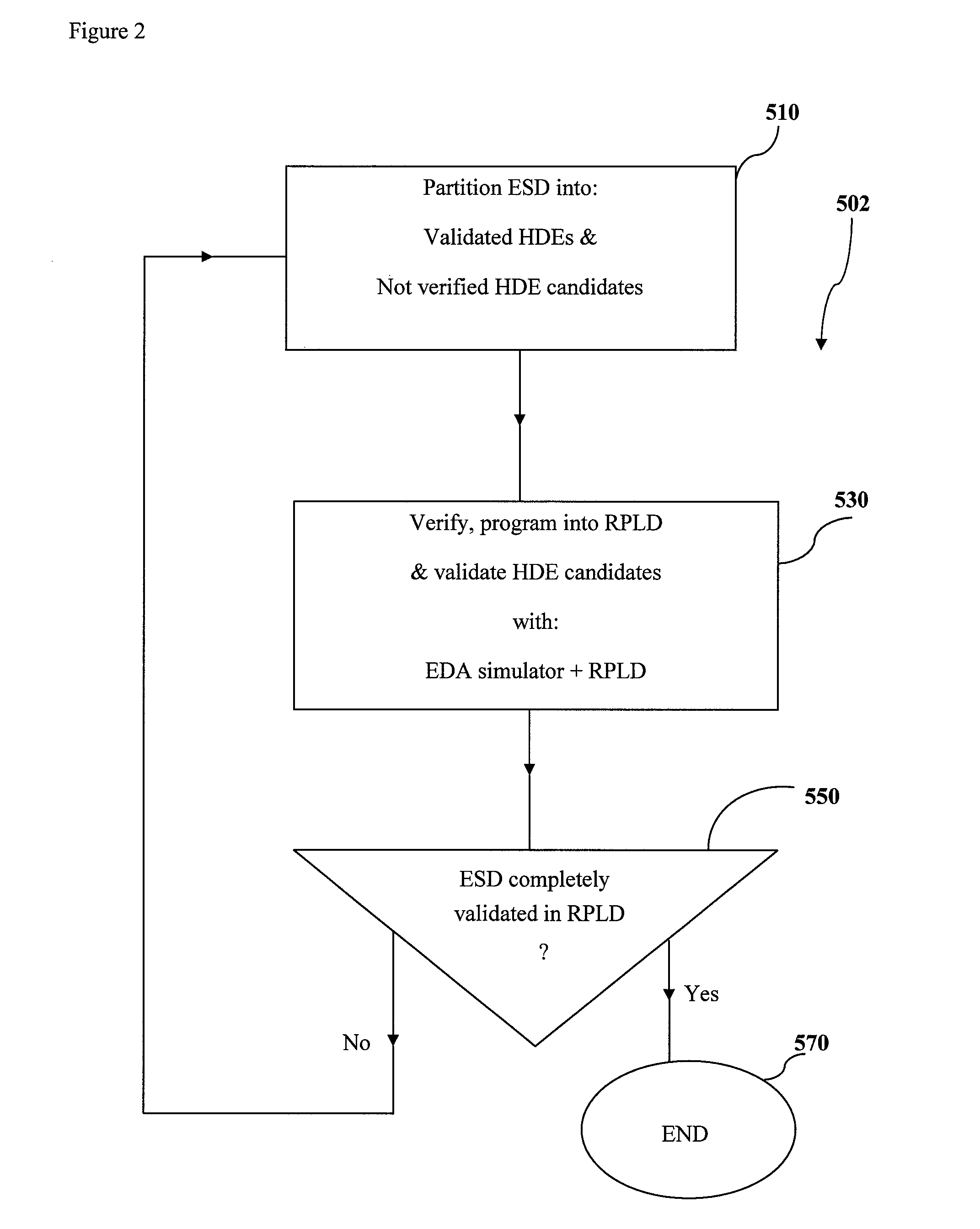

Integrated prototyping system for validating an electronic system design

InactiveUS8136065B2Improve throughputEnhanced authenticationDetecting faulty computer hardwareCAD circuit designElectronic systemsSimulTrain

An integrated prototyping system (IPS) is proposed for verifying and validating an electronic system design (ESD) with hierarchical design elements (HDEs). The IPS has: a) A reprogrammable logic device (RPLD) having an emulation timing base and an RPLD-interface for programming and simulating HDEs under validation while transacting exchanging vectors. The RPLD is also switchably coupled to numerous external peripheral electronic devices (PED), b) An EDA simulator for simulating then verifying selected HDEs while transacting exchanging vectors. The EDA simulator also has a simulator interface; and c) An IPS controller bridging the RPLD and the EDA simulator. The IPS controller has an IPS executive for progressively verifying and validating the ESD. The IPS executive further includes a co-emulation software for jointly and simultaneously running the RPLD and the EDA simulator with an event-based synchronization scheme for interchanging exchanging vectors on demand between the RPLD and the EDA simulator.

Owner:INPA SYST

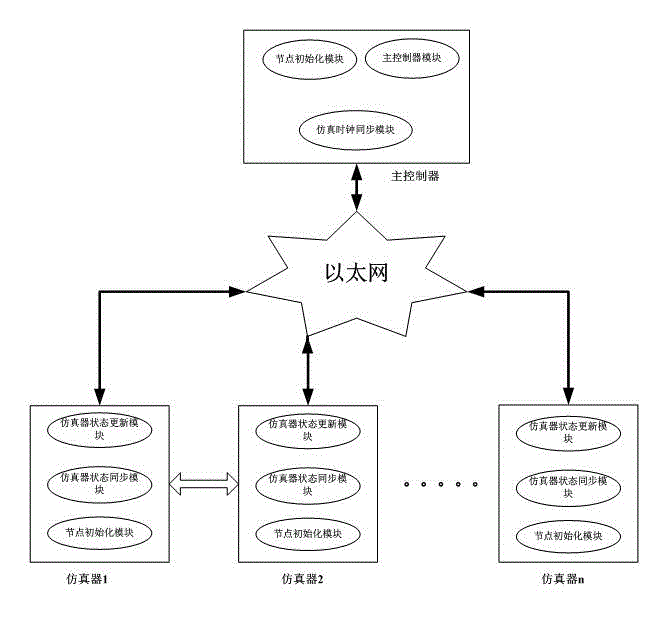

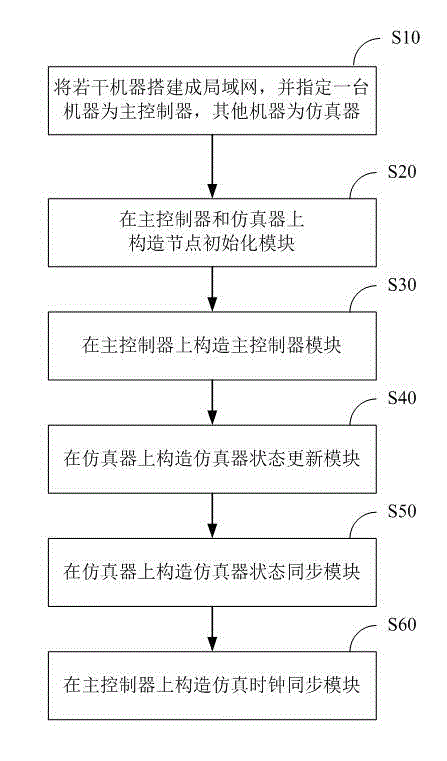

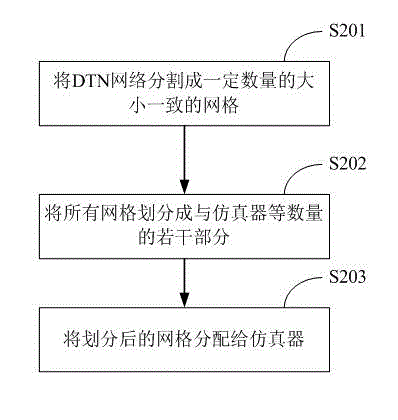

Distributed simulation system and method supporting large-scale complicated delay tolerant network (DTN)

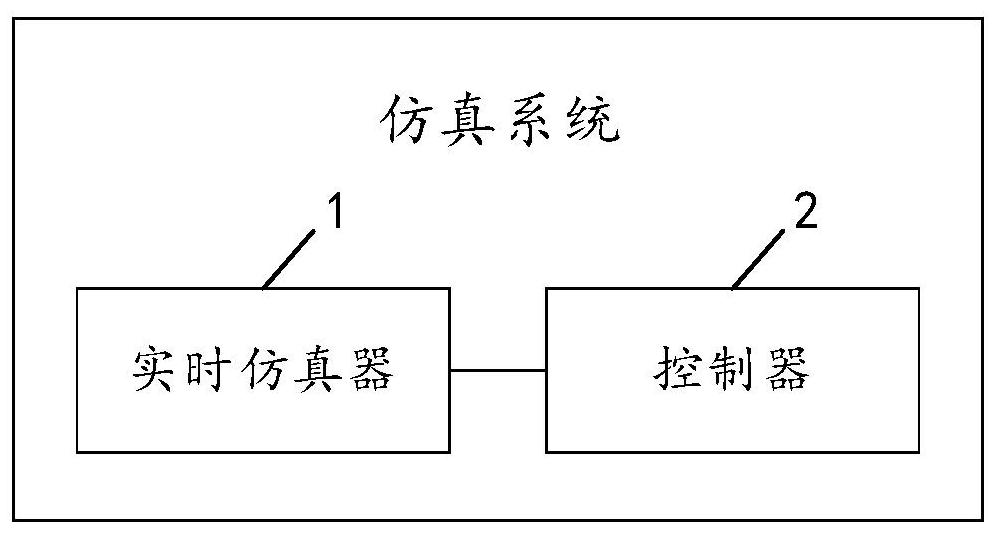

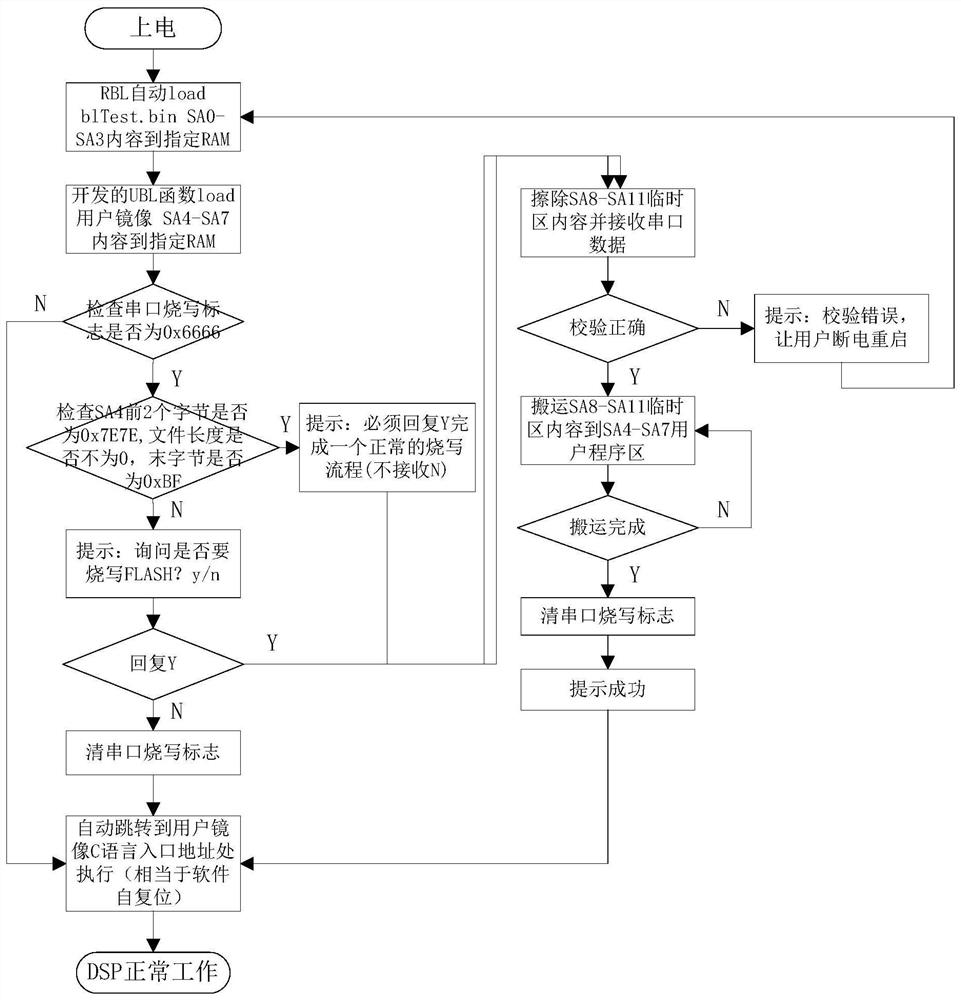

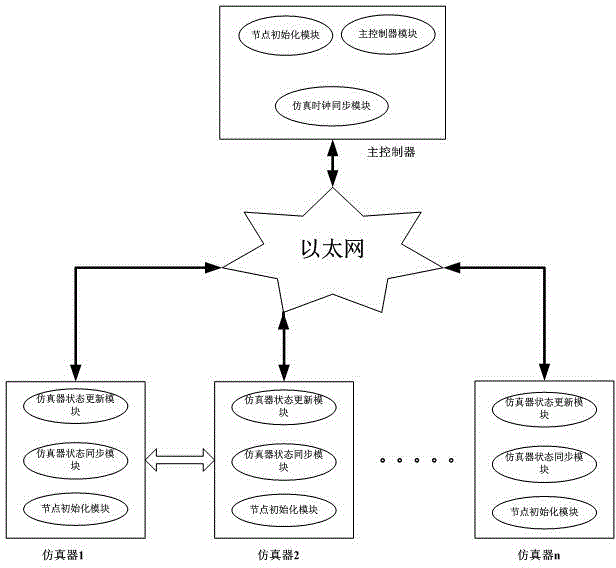

InactiveCN102752173AImprove simulation speedEasy to addData switching networksSimulTrainMaster controller

The invention relates to a distributed simulation system and method supporting a large-scale complicated delay tolerant network (DTN). The conventional DTN simulation tool can only run on a single machine, is limited in operation capacity and low in simulation performance and can support a small scale of simulation nodes. The system comprises a main controller and a plurality of simulators which are positioned in the same local area network; the DTN is partitioned into grids, and an administration region is distributed to each simulator; and the main controller processes a simulation event by promoting a simulation clock and manages simulation of the simulators to be synchronous with the states. By the distributed simulation system and the distributed simulation method, a great number of calculation demands in simulation of the DTN are distributed to different simulators, so that the simulation speed is obviously increased; by adopting a basic network topological structure with one main controller and a plurality of simulators, the expandability is high; the requirement on a DTN network simulation scheme is low; distribution simulation can be realized by the system and the method only when the simulation scheme supports linear partitioning of a simulation network; and the generality is high.

Owner:XIDIAN UNIV

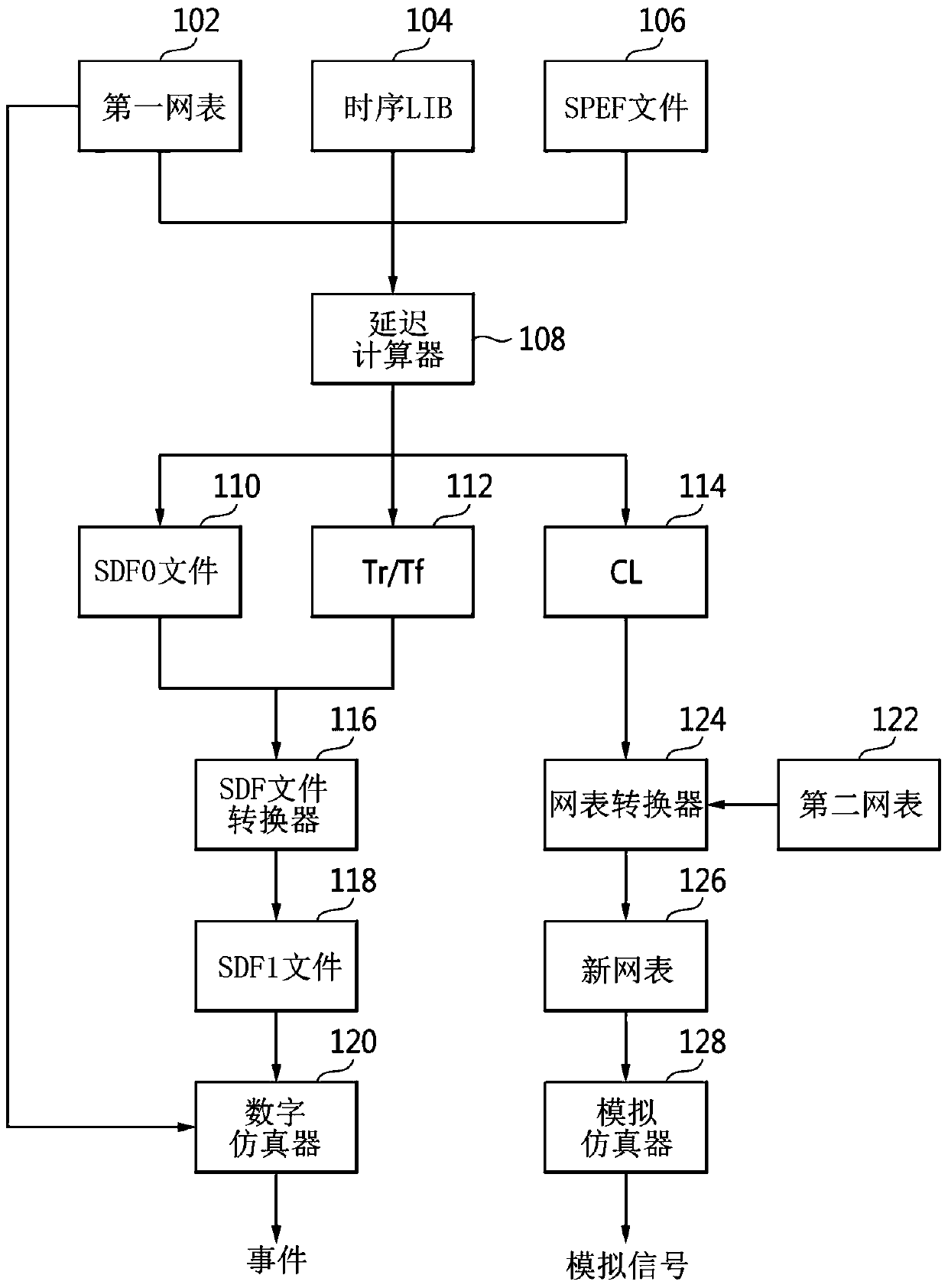

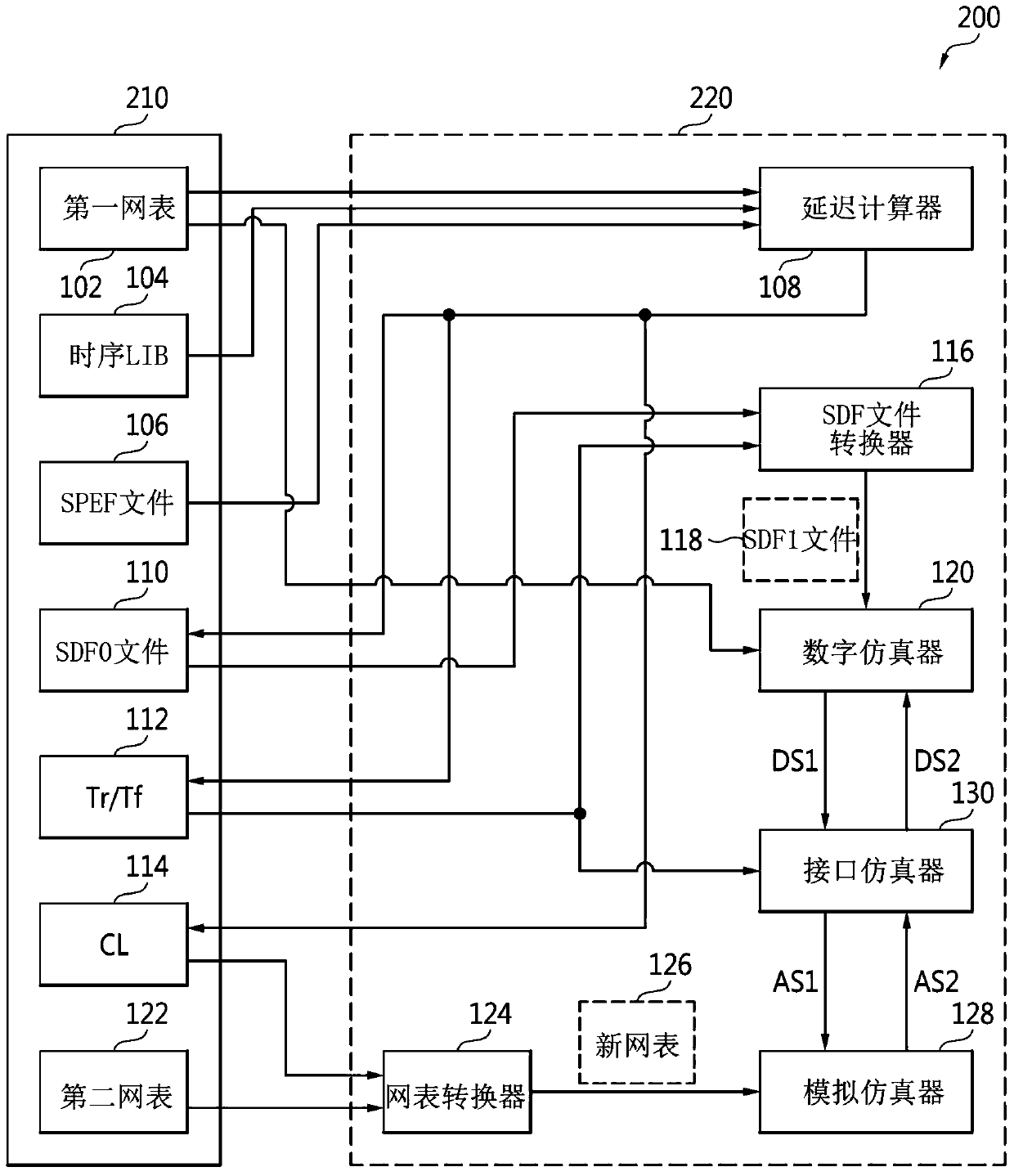

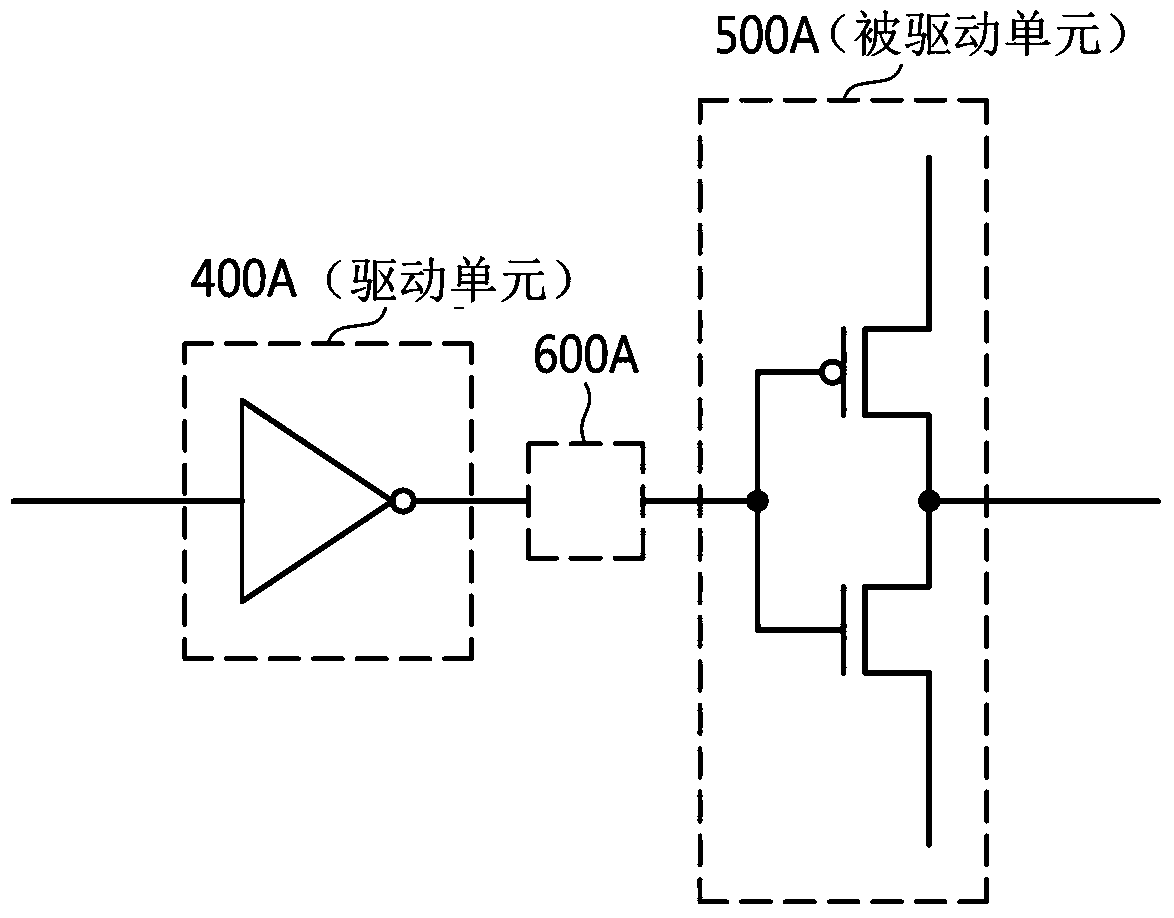

Method of operating simulator compensating for delay and device for perofmring the same

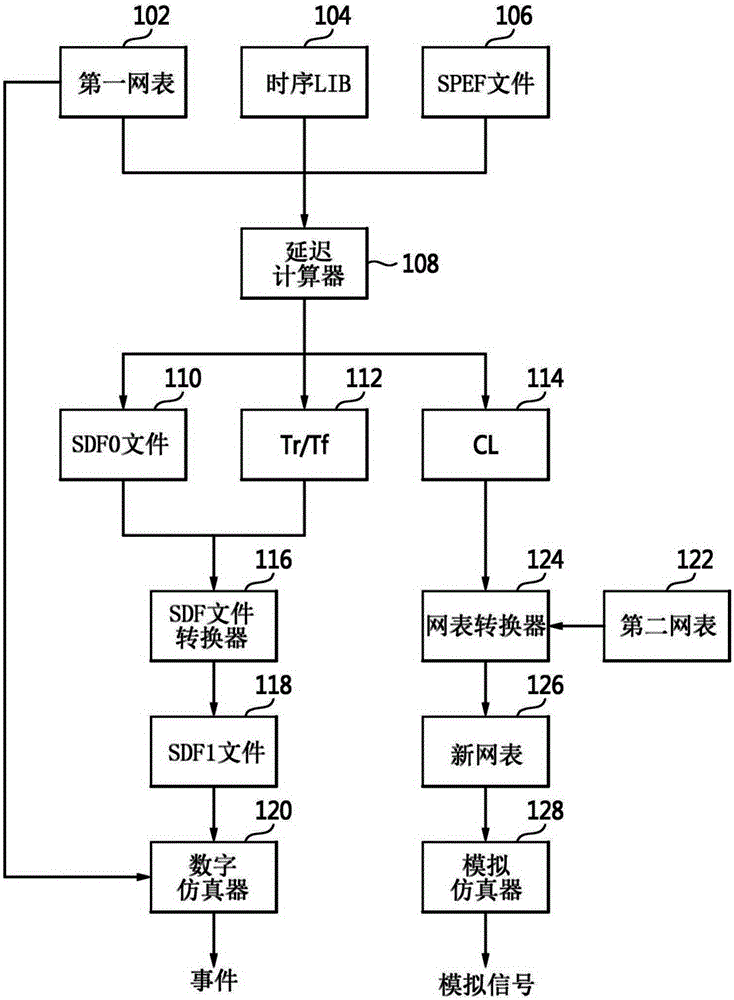

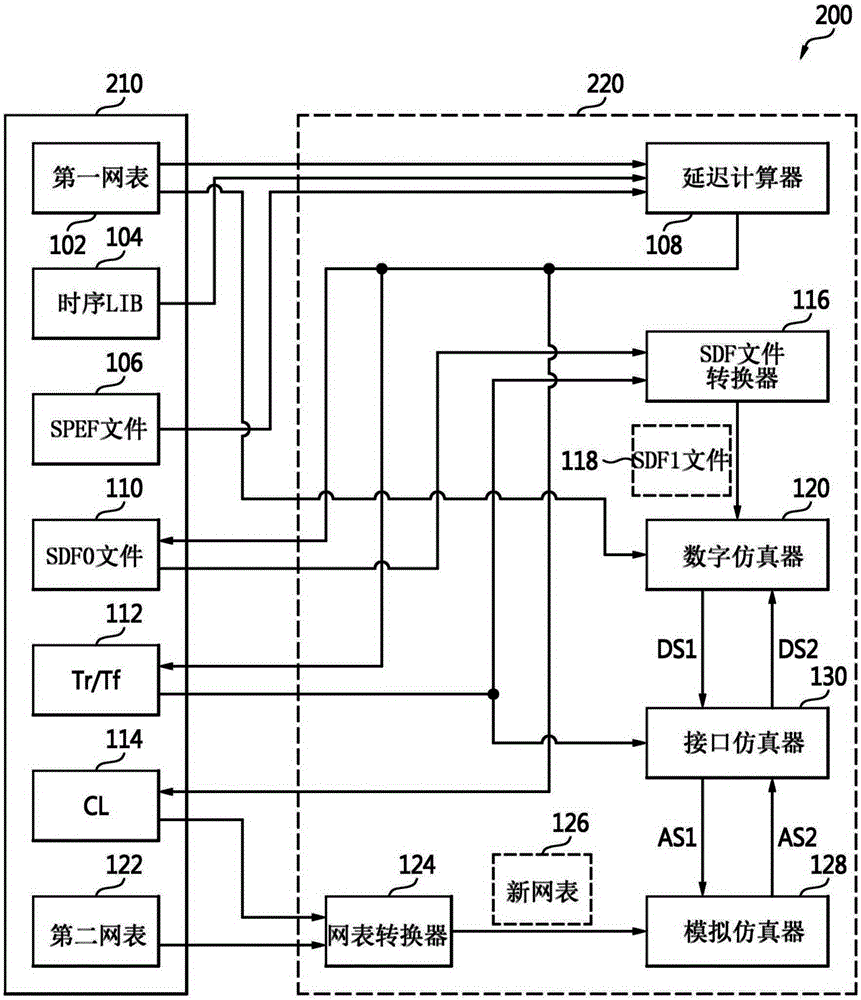

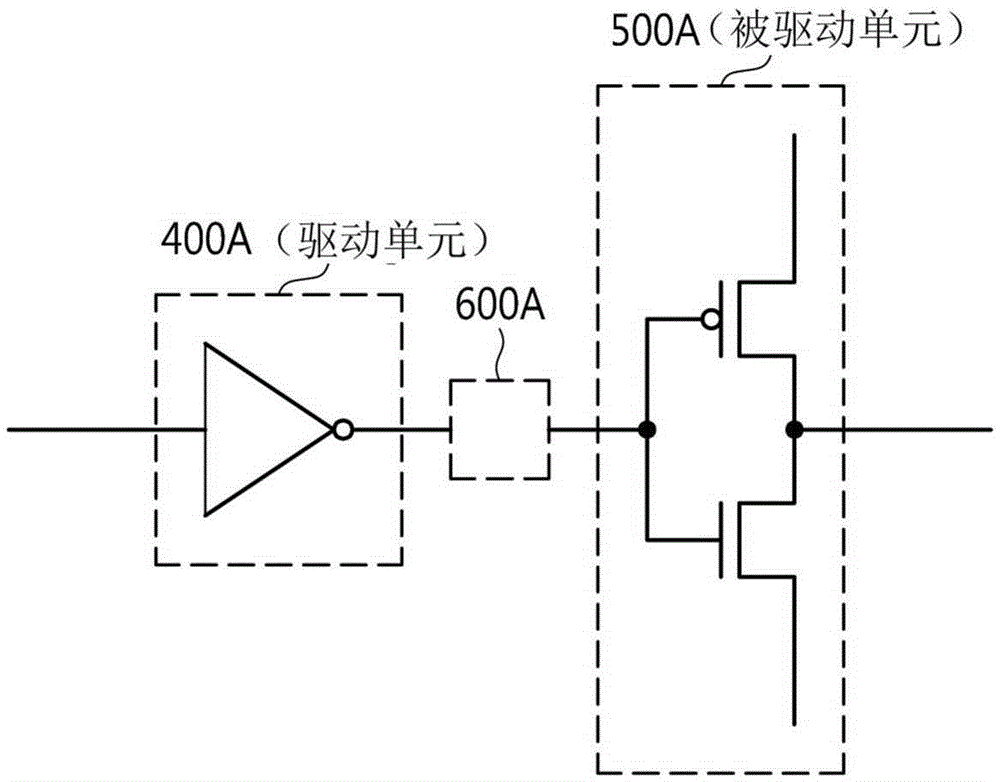

A simulator includes a memory for storing a first netlist, a timing library, and a standard parasitic exchange format (SPEF) file; and a processor configured to compensate for delay to synchronize digital and analog signals. The processor includes a delay calculator module for generating one of a rising time and a falling time and a standard delay format (SDF) file using the first netlist, the timing library, and the SPEF file; an SDF file converter module for adjusting an interconnect delay description included in the SDF file to compensate for delay using the one of the rising time and the falling time; and a digital simulator module for generating an event using a first driving cell according to a compensated interconnect delay description.

Owner:SAMSUNG ELECTRONICS CO LTD

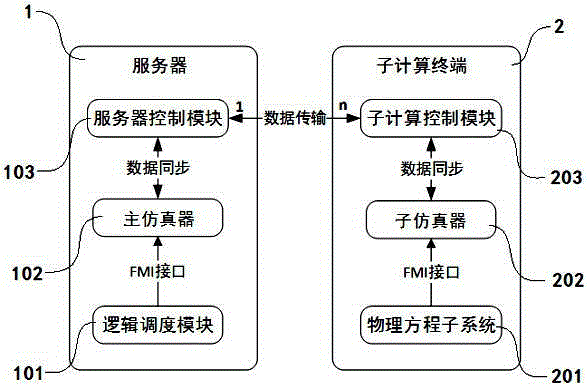

Distributed combined simulation system based on FMI and construction method

The invention discloses a distributed combined simulation system based on an FMI and a construction method. The distributed combined simulation system based on the FMI comprises a server, a master control terminal software, a sub-calculation terminal, a terminal software and an emulator. The emulator utilizes FMI combined simulation ports which are imported by various kinds of heterogeneous platforms to perform model calculation according to the FMI port logic; the master control terminal software finishes variable connection relation configuration between a system dispatching model and a sub-system calculation model; and the terminal software finishes subsystem network configuration. In the system operation process, the emulator operation system in the server operates the system dispatching model and is synchronized with the system data, and the emulator in the sub-calculation terminal operates the sub-system model. The distributed combined simulation system based on the FMI divides the system simulation into the system dispatching and system calculation, which reduces the coupling between the sub-systems, can fast realize the cooperation and combined simulation between the heterogeneous platforms, can fully utilize the calculation resource, and can solve the problems that the mass simulation system construction process is complex and the calculation efficiency is low.

Owner:苏州同元软控信息技术有限公司

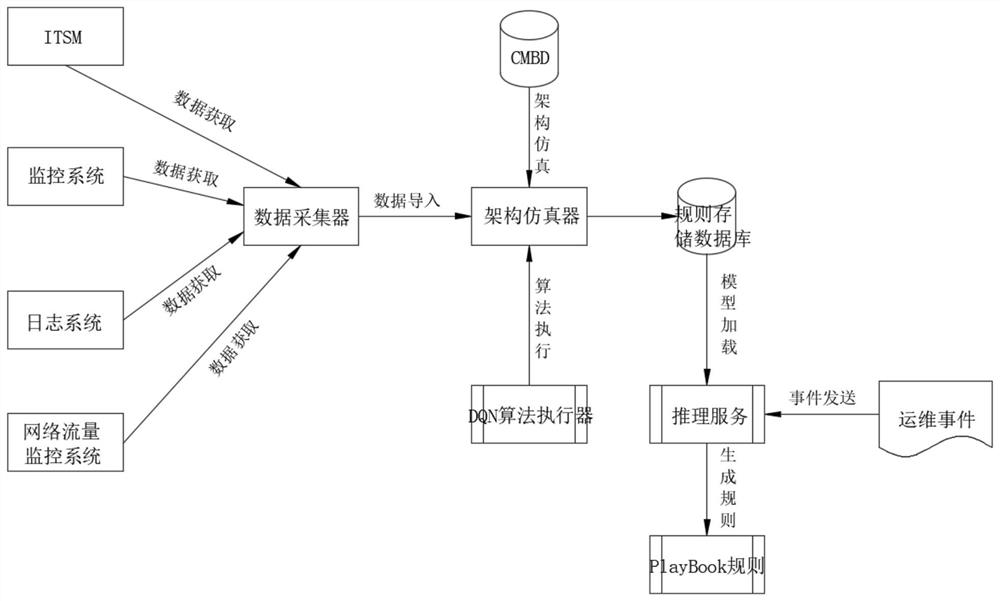

Intelligent operation and maintenance method based on deep reinforcement learning

InactiveCN112766599AImprove accuracyImprove effectivenessForecastingHardware monitoringData informationData acquisition

The invention discloses an intelligent operation and maintenance method based on deep reinforcement learning, and relates to the technical field of automatic operation and maintenance, and the method comprises the following steps: collecting data information in advance, and importing the data information into an architecture simulator through a data collector; constructing an operation and maintenance digital twin environment for data information acquired by the data acquisition unit; loading the model from the rule storage database by the reasoning service; and after an operation and maintenance event occurs, performing reasoning through reasoning service, obtaining a matched PlayBook file suitable for being used by the Ansible, and triggering an operation and maintenance action. According to the method, various operation and maintenance data are used, the training environment of deep reinforcement learning is kept consistent with the production environment, the reliability and the real-time performance are enhanced, the operation and maintenance rules are trained by adopting the deep reinforcement learning method, manpower and material resources of rule maintenance are reduced, the accuracy and the effectiveness of the operation and maintenance rules are improved. Automatic operation and maintenance rules are found intelligently, the operation and maintenance rules are updated fully automatically, and the condition of rule aging in automatic operation and maintenance is greatly reduced.

Owner:广州源创动力科技有限公司

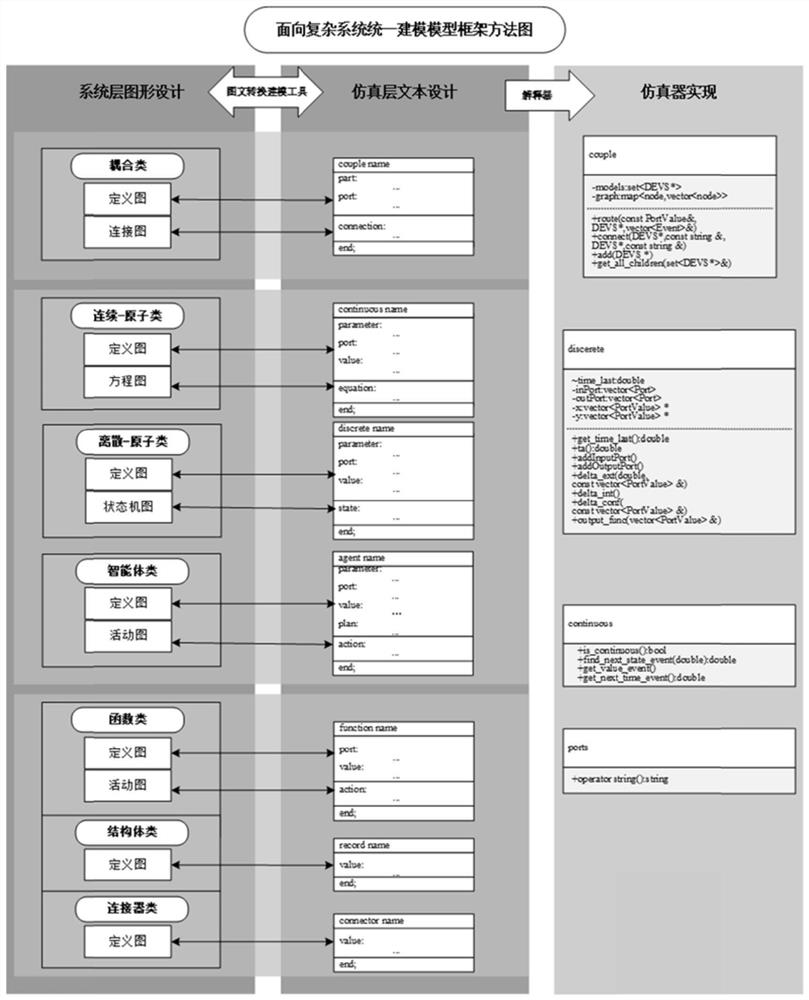

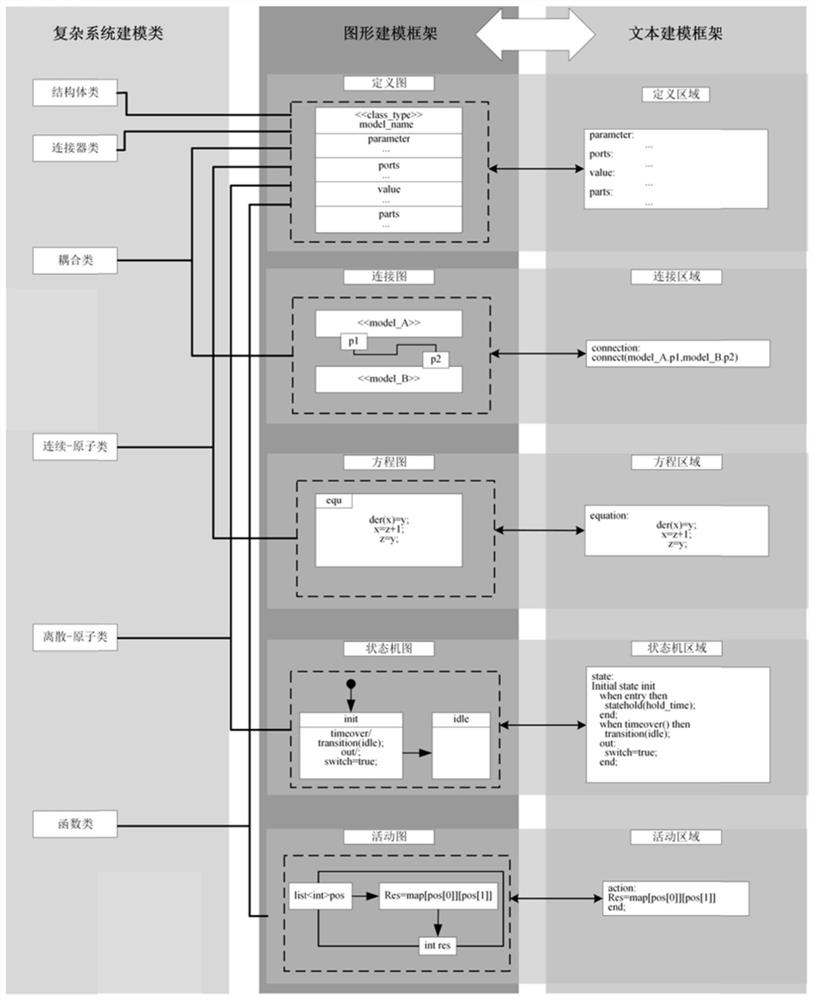

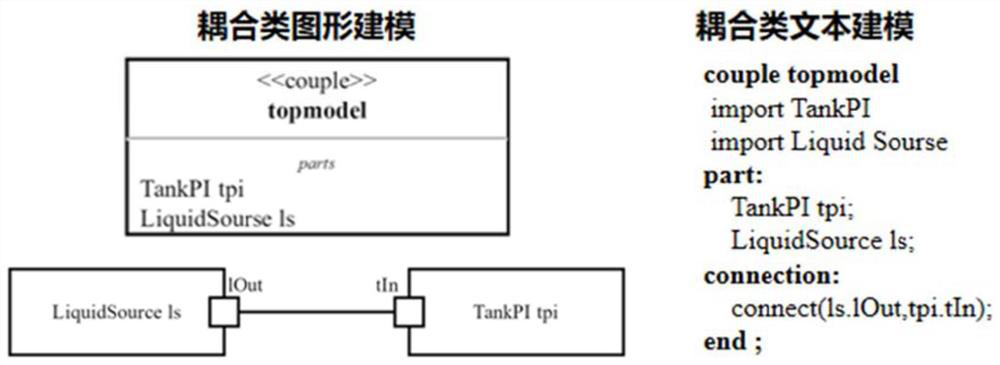

Unified modeling method supporting design and simulation of complex system

PendingCN113642147AImprove the efficiency of the R&D processAvoid difficulties such as design changes and difficulty in ensuring consistencyDesign optimisation/simulationSpecial data processing applicationsGraphicsText modeling

Disclosed is a unified modeling method supporting design and simulation of a complex system. Two forms of models of the complex system are established according to a preset graph and text modeling framework, mutual conversion of the two forms of the complex system model is achieved through an image-text conversion modeling tool, and finally the code is explained into a C++ code through an interpreter, and simulation runs in a DEVS simulator environment. System design and simulation verification of a complex system model are integrated through two modeling forms of graphs and texts, the efficiency of the research and development process of the complex system is improved, the learning cost of modeling personnel is reduced, the difficulty in changing the design of the complex system model is avoided, and the consistency is difficult to guarantee.

Owner:BEIHANG UNIV

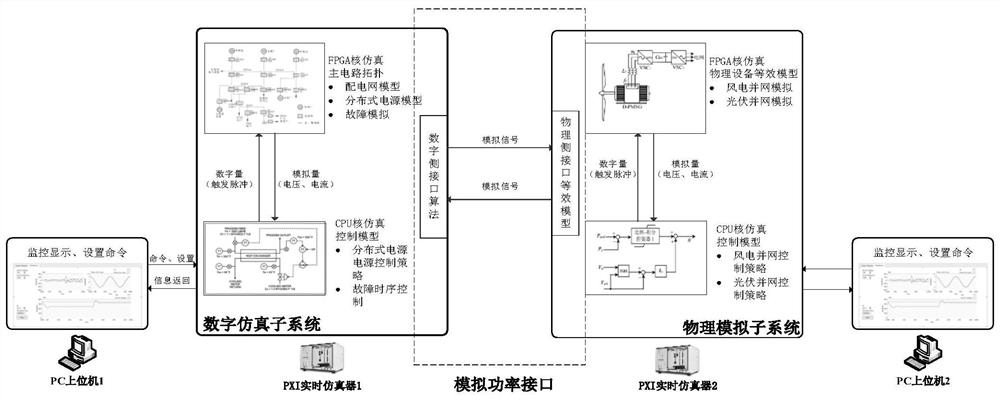

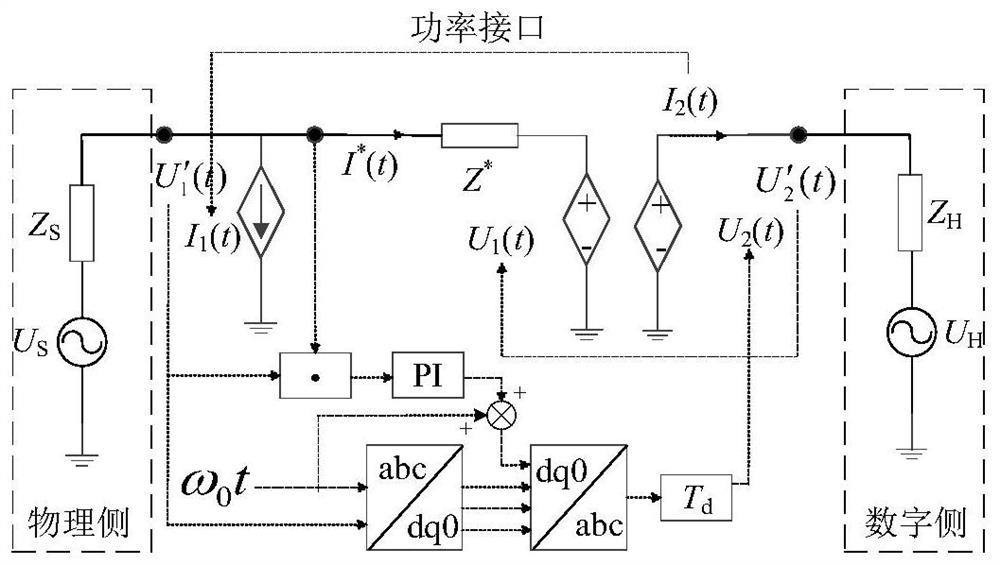

Digital-analog hybrid simulation interface test platform based on multiple real-time simulators

The invention belongs to the technical field of digital physical hybrid simulation, and particularly provides a digital-analog hybrid simulation interface test platform based on double real-time simulators. The platform comprises two real-time simulators respectively simulating a digital side and a physical side, the simulators run in parallel, and the actual working condition of the hybrid simulation system is simulated through real physical interface connection. The test platform is closer to the actual working condition of the hybrid simulation system than off-line simulation, the verification of the validity of the simulation interface under different working conditions can be quickly realized through the platform, the parameters can be set on line, and the research and development process is greatly accelerated. The platform solves the problems of lack of actual working condition verification and difficulty in parameter setting in interface algorithm research.

Owner:NORTH CHINA ELECTRIC POWER UNIV (BAODING) +1

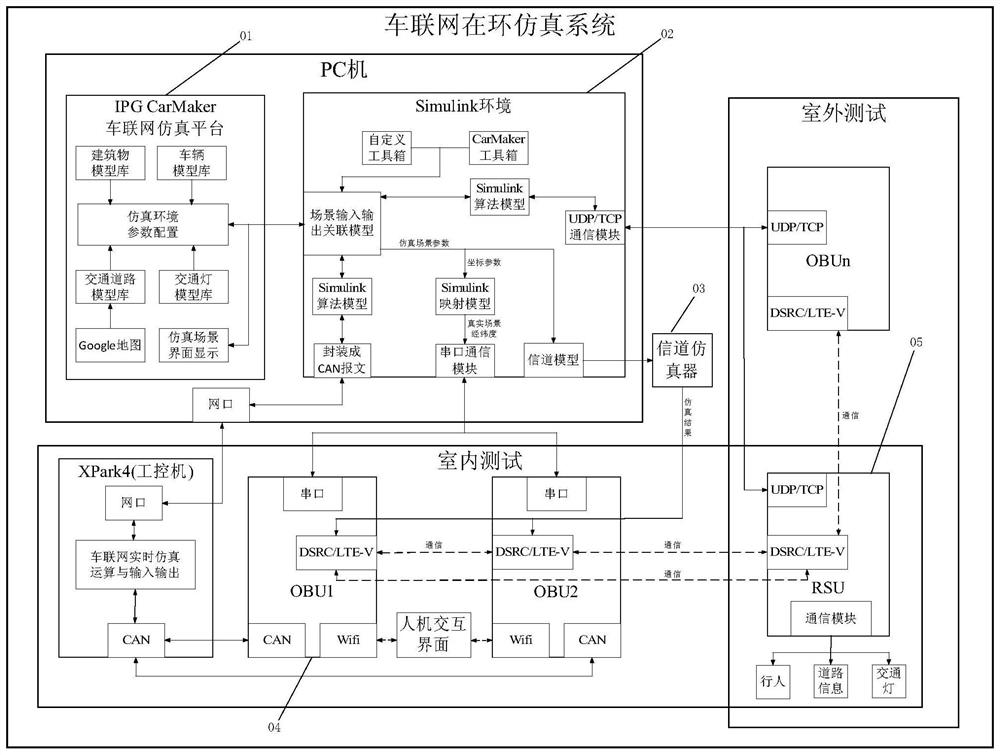

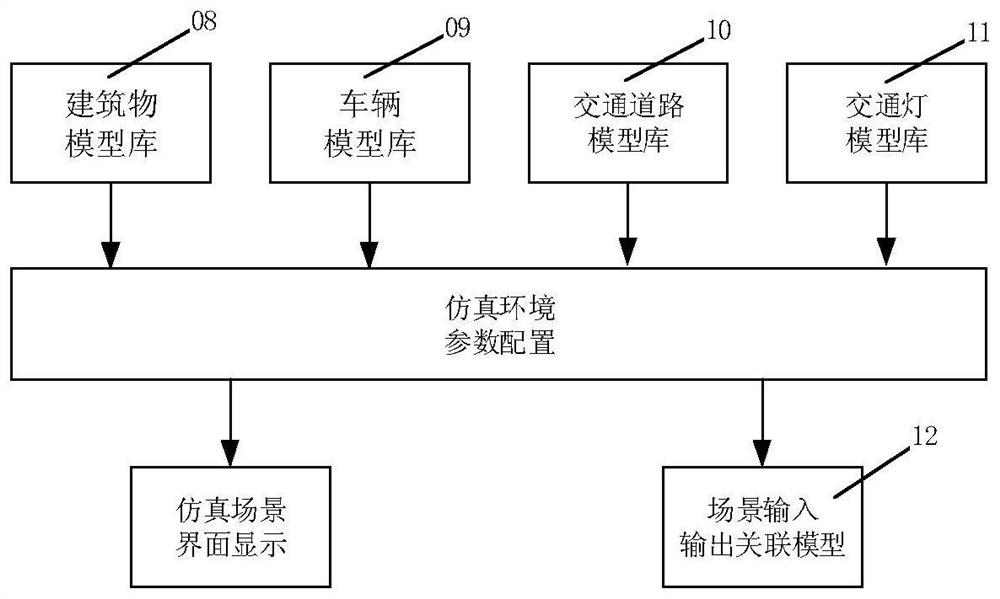

A v2x vehicle networking in-the-loop simulation system

ActiveCN107728491BImprove securityImprove traffic efficiencySimulator controlSimulTrainReal-time computing

The invention discloses a V2X Internet of Vehicles (IoV) on-loop simulation system, and belongs to the field of IoV. The system is mainly composed of an IPG carmaker IoV simulation platform (01), a Simulink environment module (02), a channel simulator (03), a V2X communication terminal (04) and a V2X road side device (05), wherein the IPG carmaker simulation tool is responsible for building a simulation scene and configuring simulating parameters, the Simulink environment module is responsible for building a channel model, a simulation scene and real scene mapping model, a control model and acommunication model, the channel simulator is used for conducting performance test on LTE-V, 802. 11p communication protocol, the V2X communication terminal is connected with the Simulink communication model to obtain the scene information and realize on-loop simulation, and the V2X road side device imports the obtained information of the real scene into a simulation scene to achieve an outdoor test function. All the modules supplement each other to form a perfect on-loop simulation system and provide a good testing and verifying platform for the IoV application.

Owner:CHONGQING UNIV OF POSTS & TELECOMM

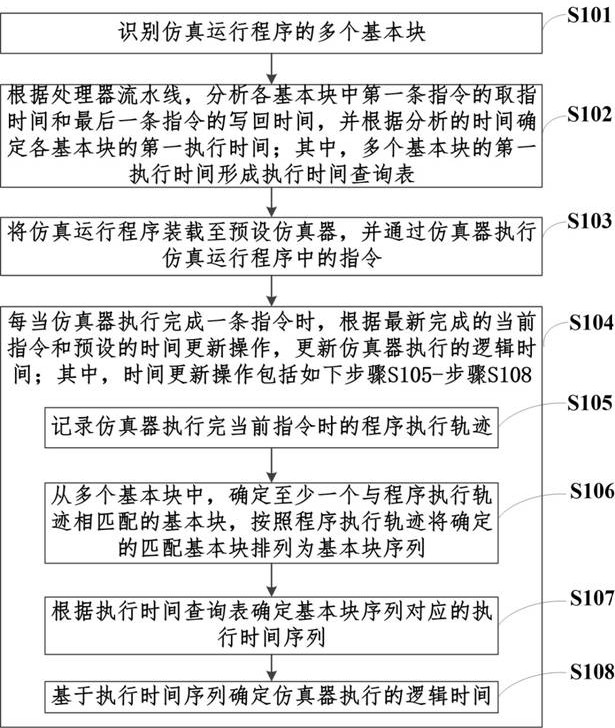

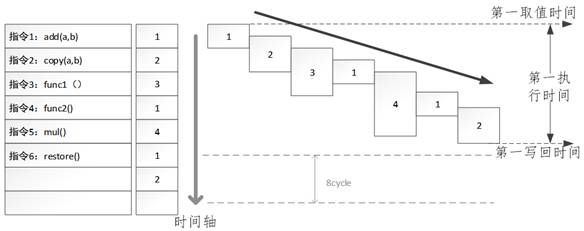

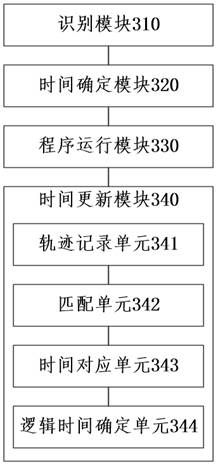

A time and timing calibration method and device based on processor pipeline analysis

ActiveCN113254084BReduce time errorImprove accuracyConcurrent instruction executionSoftware simulation/interpretation/emulationSimulTrainLogisim

The disclosure relates to a time and timing calibration method and device based on processor pipeline analysis, the method includes: identifying multiple basic blocks of a simulation running program; analyzing the first execution time of each basic block according to the processor pipeline, multiple The first execution time of the basic block forms an execution time lookup table; the simulation running program is loaded into the preset emulator, and whenever the emulator completes an instruction, the logic executed by the emulator is updated according to the latest completed current instruction and time update operation Time, the time update operation includes: recording the program execution track; determining the basic blocks that match the program execution track, and arranging the determined matching basic blocks into a basic block sequence according to the program execution track; determining the basic block sequence according to the execution time lookup table Corresponding execution time series; determine the logical timing of simulator execution based on the execution time series. The present disclosure can reduce timing errors between simulated time and actual time.

Owner:航天中认软件测评科技(北京)有限责任公司

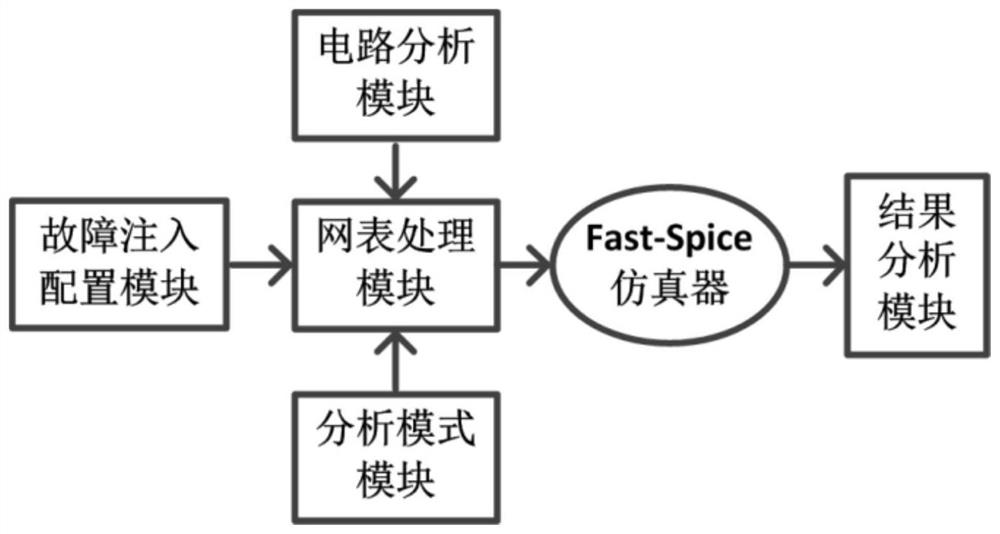

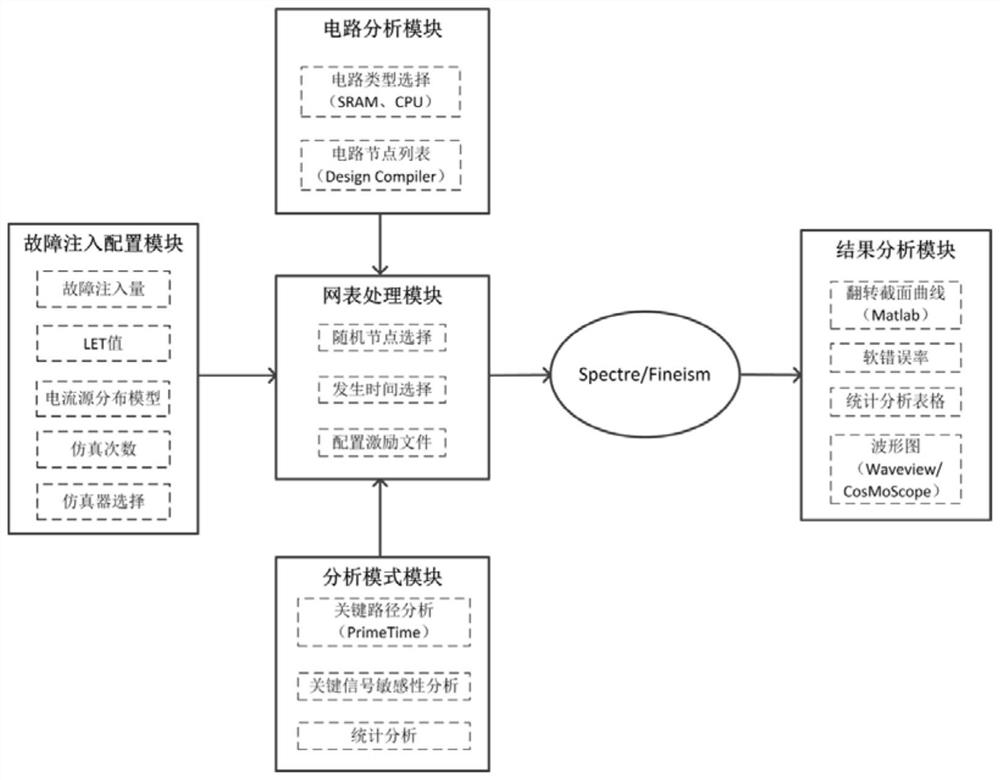

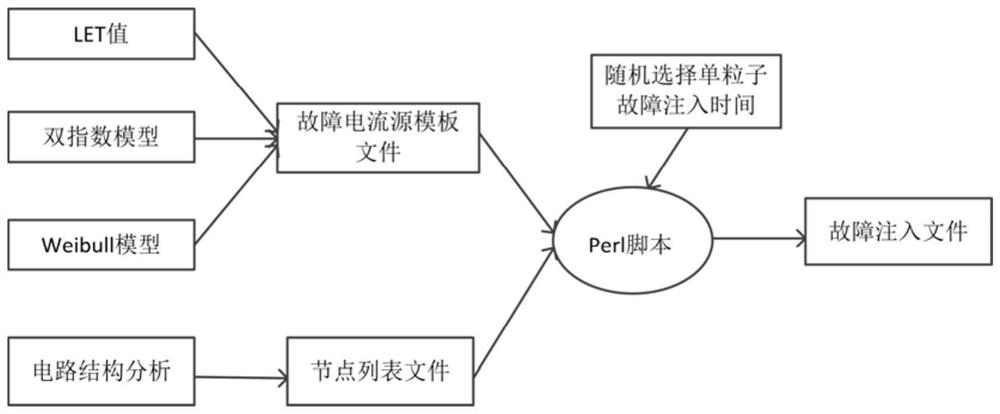

A circuit-level single event effect simulation platform

ActiveCN108363894BPrecise positioningLow costDesign optimisation/simulationCAD circuit designSimulTrainEngineering

The invention provides a circuit-level single-event effect simulation platform, which can support large-scale circuits of more than ten thousand gates to carry out single-event effect simulation analysis. The circuit-level single event effect simulation platform includes a circuit analysis module, a fault injection configuration module, an analysis mode module, a netlist processing module, and a result analysis module. The circuit analysis module extracts all sensitive nodes in the circuit and generates a circuit node list file; The injection configuration module combines the circuit node list file and the relevant parameters of the fault current source to be injected into the circuit by the user, writes a script to randomly select the circuit node and fault injection time, and generates a fault injection file; the netlist processing module writes a script to obtain the result detection file, and then Combining the analysis mode and the fault injection file to generate a stimulus file and provide it to the Fast-Spice simulator; the result analysis module saves and extracts the simulation results, and forms different result icons according to different analysis modes.

Owner:陕西欣微绘通科技有限公司

A debugging method of vxworks operating system

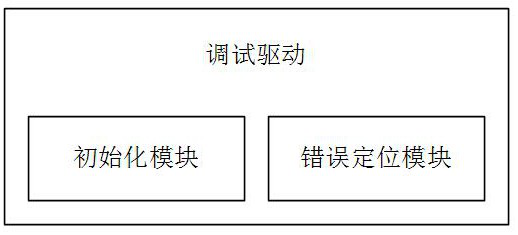

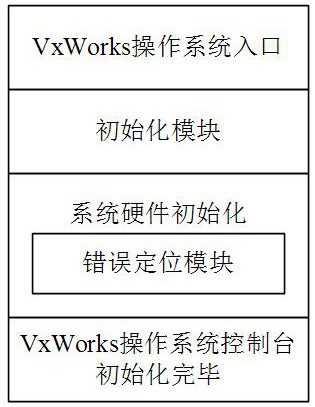

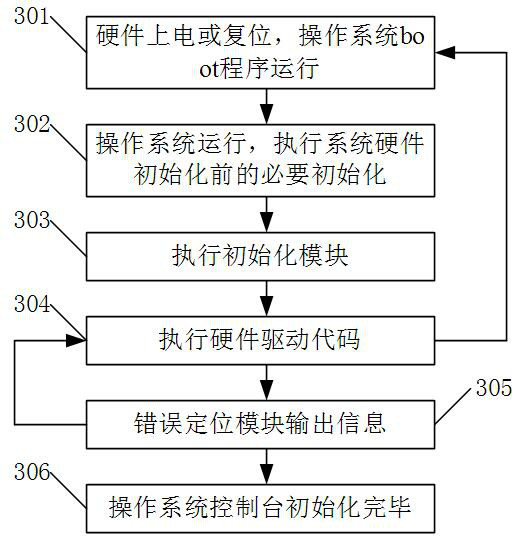

ActiveCN108121627BReduce design costCompact designDetecting faulty hardware by configuration testSoftware testing/debuggingComputer architectureOperational system

The invention discloses a VxWorks operating system debugging method, comprising the following steps: adding a debugging driver to the BSP code of the VxWorks operating system, compiling with the VxWorks operating system, and calling the debugging driver at the first C language code of the VxWorks operating system After the BSP code that needs to be debugged, add the error location module of the debugging driver, and the error location module reflects the execution result of the corresponding BSP code; modify the errors in the BSP code until all errors are closed, and the VxWorks operation is completed System debugging. The invention can be applied to the debugging of VxWorks operating systems of different CPU types, and the method is simple. Adopting the present invention does not require extra emulator overhead and reduces design cost. After debugging without using an emulator, the hardware single board can reduce the design of the JTAG interface, which is conducive to the development of product miniaturization.

Owner:SUZHOU CHANGFENG AVIATION ELECTRONICS

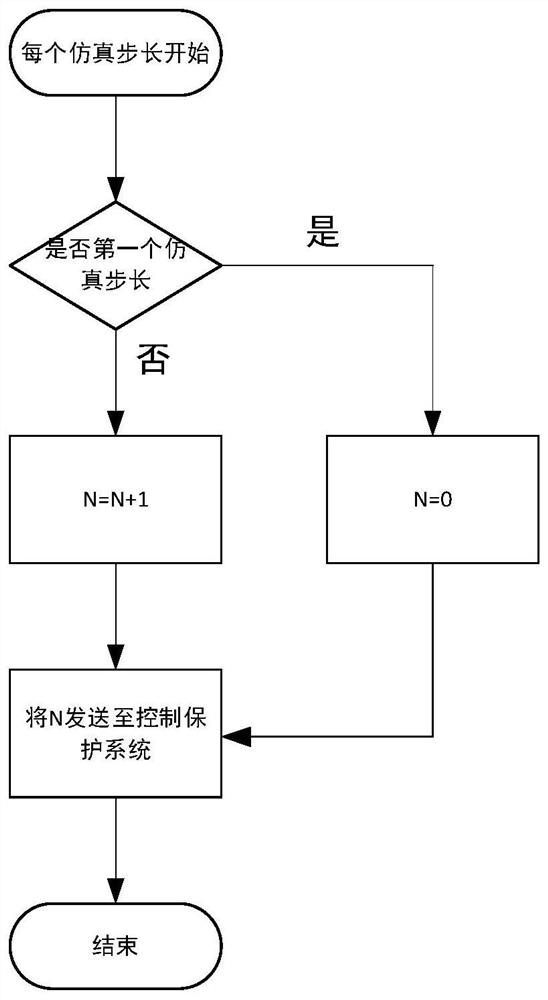

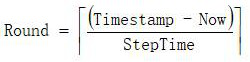

A simulation system clock synchronization method, device, equipment and storage medium

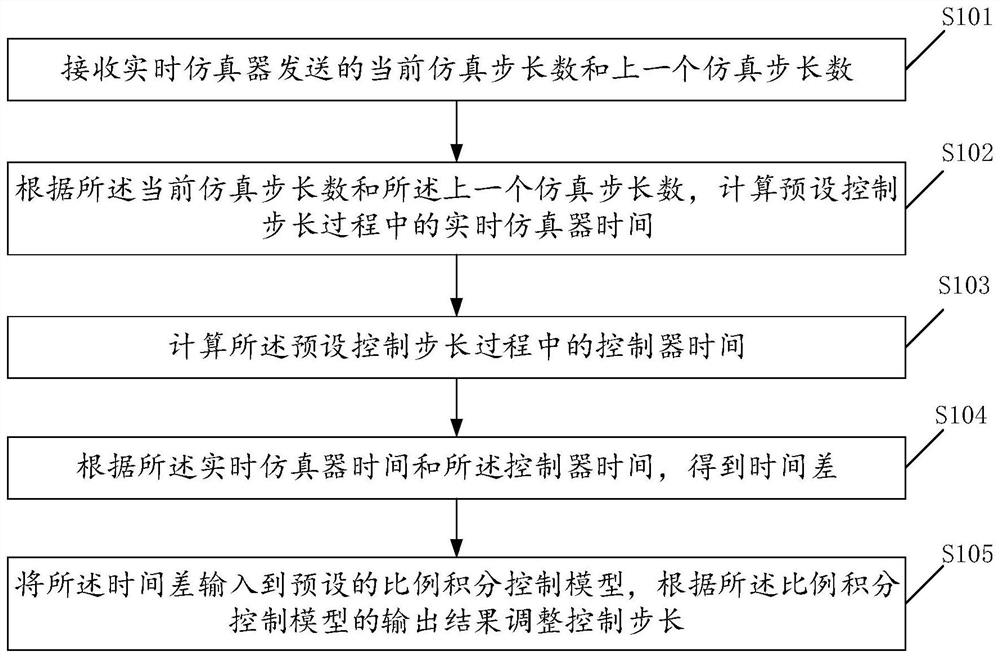

ActiveCN111290477BAchieving Clock SynchronizationImprove stabilityGenerating/distributing signalsSoftware simulation/interpretation/emulationSynchronizerReal-time simulation

The invention discloses a clock synchronization method for a simulation system, comprising: receiving the current simulation step number and the last simulation step number sent by a real-time simulator; according to the current simulation step number and the last simulation step number , calculating the real-time simulator time in the preset control step process; calculating the controller time in the preset control step process; obtaining a time difference according to the real-time simulator time and the controller time; The time difference is input to a preset proportional-integral control model, and the control step size is adjusted according to the output result of the proportional-integral control model. The invention also discloses a simulation system clock synchronization device, equipment and storage medium, which can effectively realize the clock synchronization of the simulator and the controller in the simulation system, thereby greatly improving the stability of the simulation system.

Owner:ELECTRIC POWER RESEARCH INSTITUTE, CHINA SOUTHERN POWER GRID CO LTD +1

Method of operating simulator compensating for delay and device for performing the method

A method of operating a delay-compensated simulator and an apparatus for performing the method are provided. The emulator includes: a memory for storing a first netlist, a timing library, and a standard parasitic exchange format (SPEF) file; and a processor configured to compensate for delays to synchronize digital and analog signals. The processor includes: a delay calculator module for generating one of rise time and fall time and a Standard Delay Format (SDF) file using the first netlist, timing library, and Standard Parasitic Exchange Format (SPEF) file; the SDF file a converter module for adjusting an interconnection delay description included in the SDF file to compensate for the delay using said one of the rise time and the fall time; and a digital simulator module for utilizing the compensated interconnection delay description based on the compensated interconnection delay description The first drive unit generates an event.

Owner:SAMSUNG ELECTRONICS CO LTD

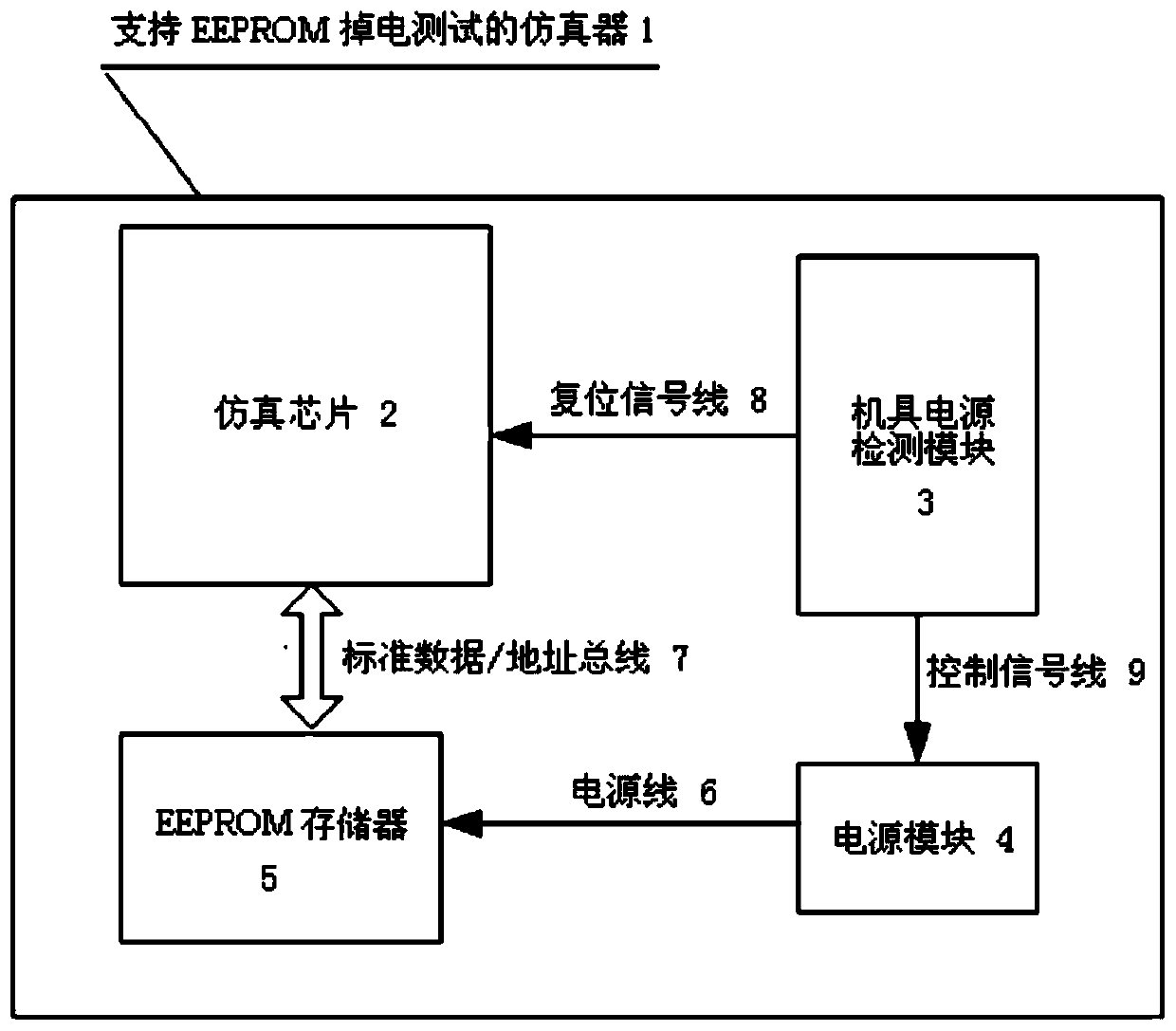

Emulator that supports eeprom power down test

ActiveCN106610862BGuaranteed service lifeImprove development efficiencyFault responseSoftware simulation/interpretation/emulationControl signalSimulTrain

The invention discloses a simulator supporting an EEPROM power failure test. The simulator comprises an EEPROM, a simulation chip, a machine tool power supply detection module, and a power supply module; the machine tool power supply detection module can automatically detect a power supply state of a contact type or non-contact type machine tool, and controls the simulation chip to be in a non-reset state, namely, a normal working state, through a reset signal line when the machine tool is powered; the machine tool power supply detection module controls the power supply module to supply power to the EEPROM by a power supply line through a control signal; the machine tool power supply detection module controls the simulation chip to enter the reset state through the reset signal line when the machine tool is not powered, namely, the machine tool loses the power, so as to enable the simulation chip not to work; and the machine tool power supply detection module controls the power supply module to no longer supply the power to the EEPROM by the power supply line through the control signal, namely, the EEPROM loses the power. According to the simulator, the development, debugging and testing of user programs can be facilitated and the code development efficiency is improved.

Owner:SHANGHAI HUAHONG INTEGRATED CIRCUIT

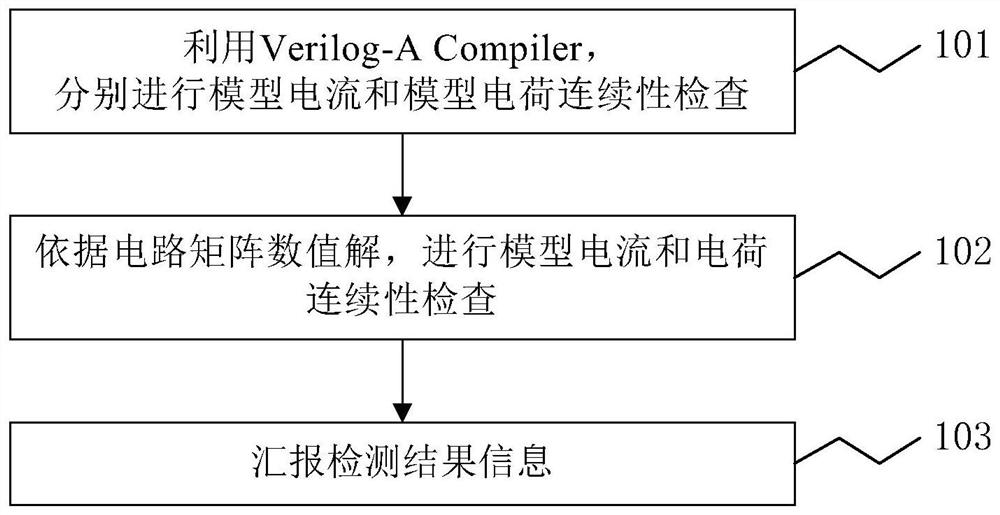

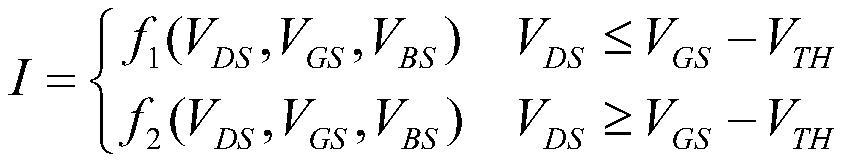

Model continuity checking method

InactiveCN112651202ACheck continuityImprove development efficiencyComputer aided designSpecial data processing applicationsAlgorithmSimulTrain

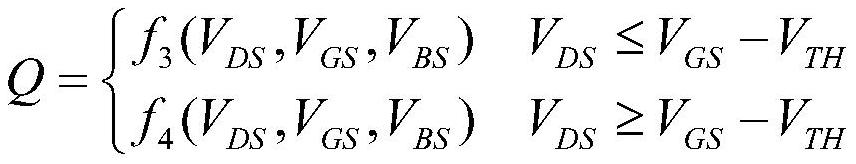

The invention relates to a model continuity checking method, which comprises the following steps of: respectively checking the continuity of a model current and a model charge by using Verilog-A Compeller; performing model current and charge continuity check according to the circuit matrix numerical solution; and reporting inspection result information. According to the method for checking the continuity of the model, an analytical formula of the model is analyzed by utilizing Verilog-A Compiler, so that the continuity of a segmented bias part can be quickly checked; dynamically checking the current and charge values in the simulation process; quickly checking discontinuous bias points through dynamic checking, reporting discontinuous point information, providing insight for problem analysis for simulator developers, and improving software development efficiency. Static inspection is performed first and then dynamic inspection is performed so that excessive inspection steps can be avoided.

Owner:北京华大九天科技股份有限公司

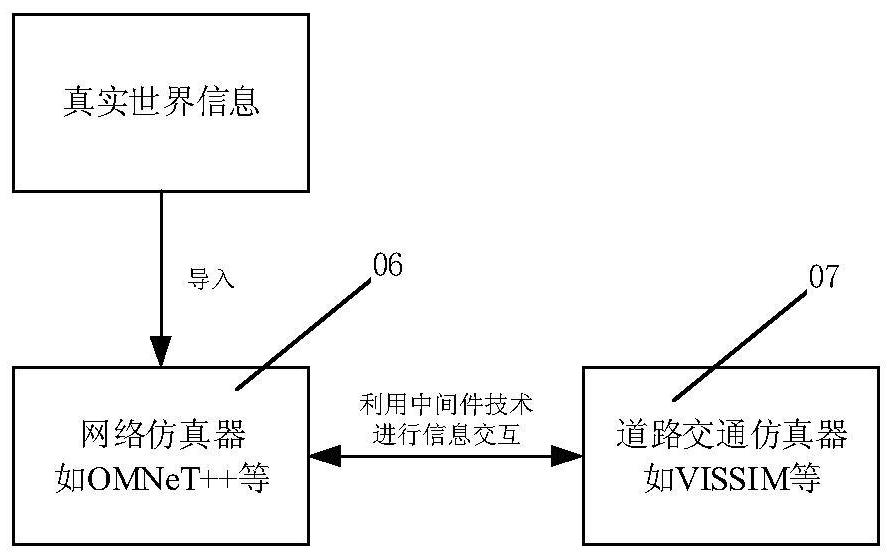

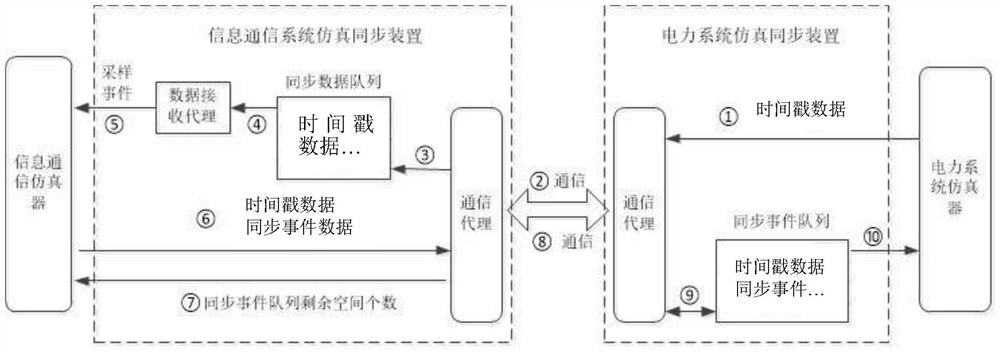

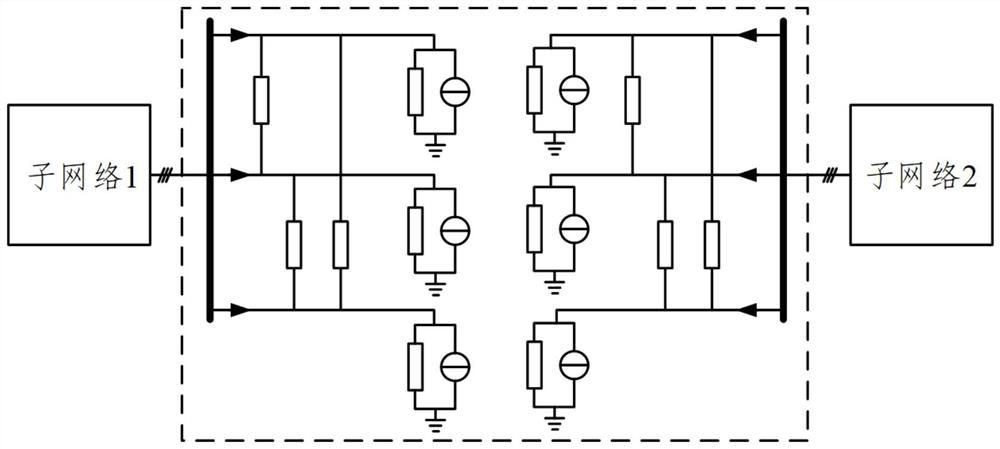

A device and method for time synchronization and data exchange for co-simulation of power system and information communication system

InactiveCN105930580BFlexible and proactive sendingGuaranteed accuracyDatabase updatingData processing applicationsStart timeCommunications system

A device and method for time synchronization and data exchange for co-simulation of power and information communication systems, including an information communication system simulation synchronization device and a power system simulation synchronization device, the present invention adopts a "peer-to-peer" synchronization system architecture, Both the telematics simulator and the power system simulator can transmit data flexibly and proactively. An event queue is set on both sides to forward time-stamped data and event start time, and it also serves as a "synchronized timeline" to keep the two simulation platforms time-synchronized while transmitting data. During the simulation process, both simulators advance their respective simulation tasks in parallel with reference to the "synchronized timeline" on their own side, and wait for each other by suspending themselves when the speeds of the two sides do not match.

Owner:STATE GRID CORP OF CHINA +2

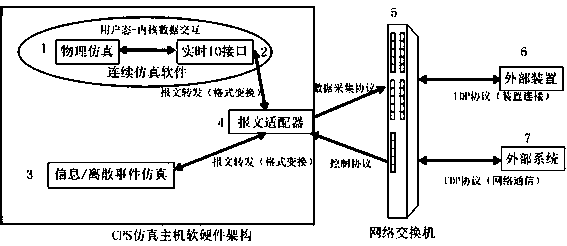

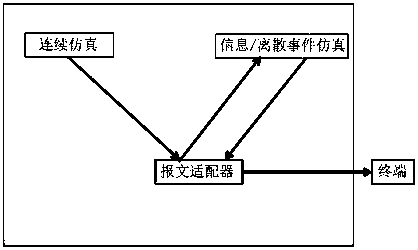

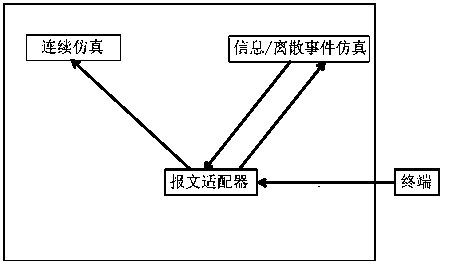

Panoramic information physical fusion system simulation architecture and working method thereof

PendingCN111077803ARealize Information-Physical Simulation InteractionEasy maintenanceSimulator controlNetwork socketSoftware emulation

The invention discloses a panoramic information physical fusion system simulation architecture and a working method thereof. The system comprises a software simulator and an external device system which are connected with each other. The method comprises the steps of obtaining state information data of a physical system through the software simulator; and sending the state information data to theexternal device system according to a data acquisition protocol. The software simulator is connected with an external device through a network socket interface, interaction between a CPS simulation device and the external device / system is achieved through UDP protocol interaction, information-physical simulation interaction is achieved, system maintenance is convenient, and a simulation scale canbe increased or decreased at any time.

Owner:NARI TECH CO LTD +3

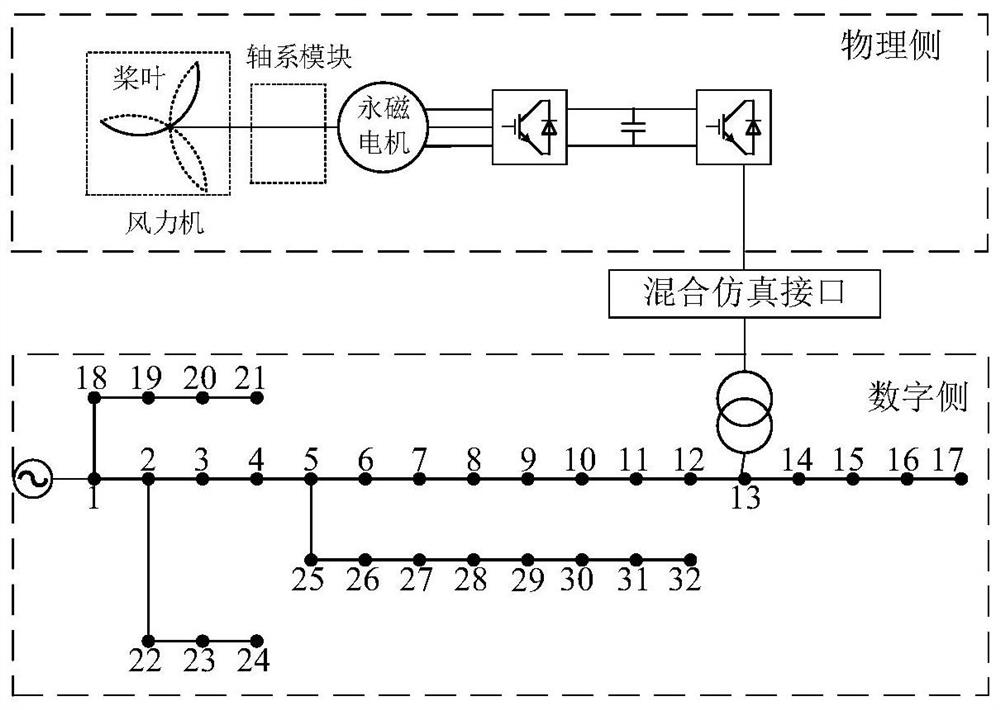

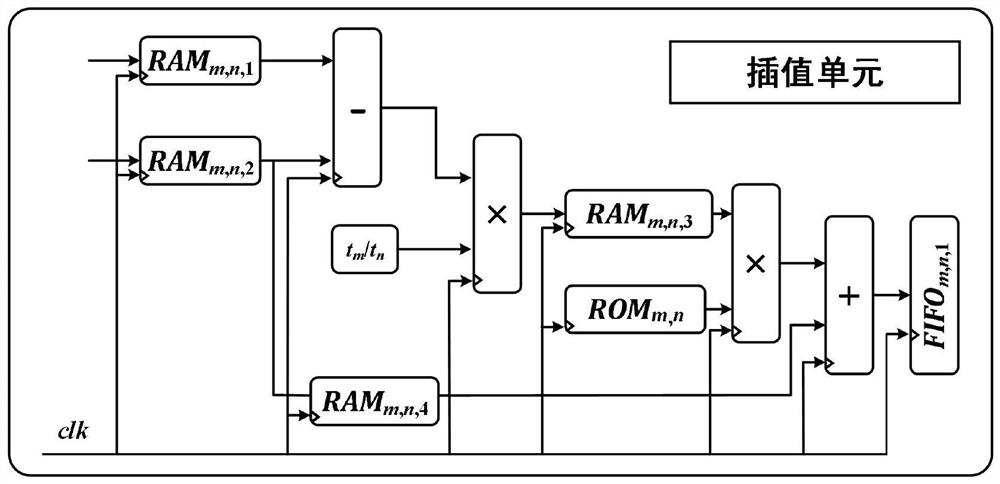

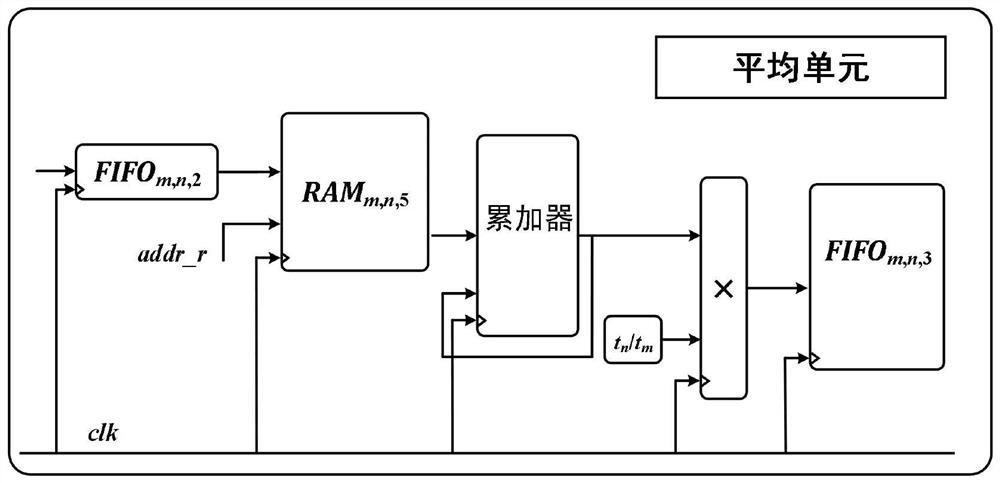

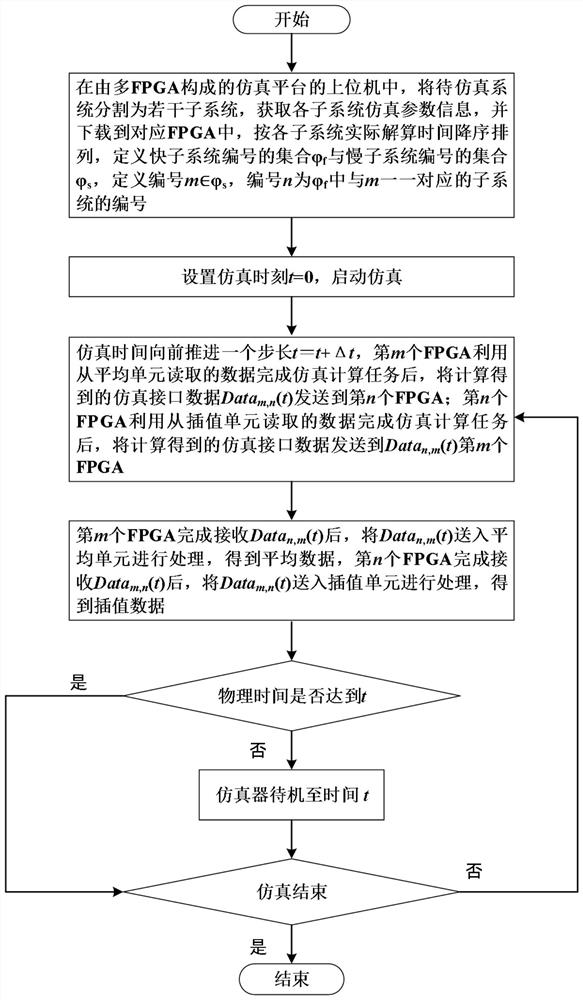

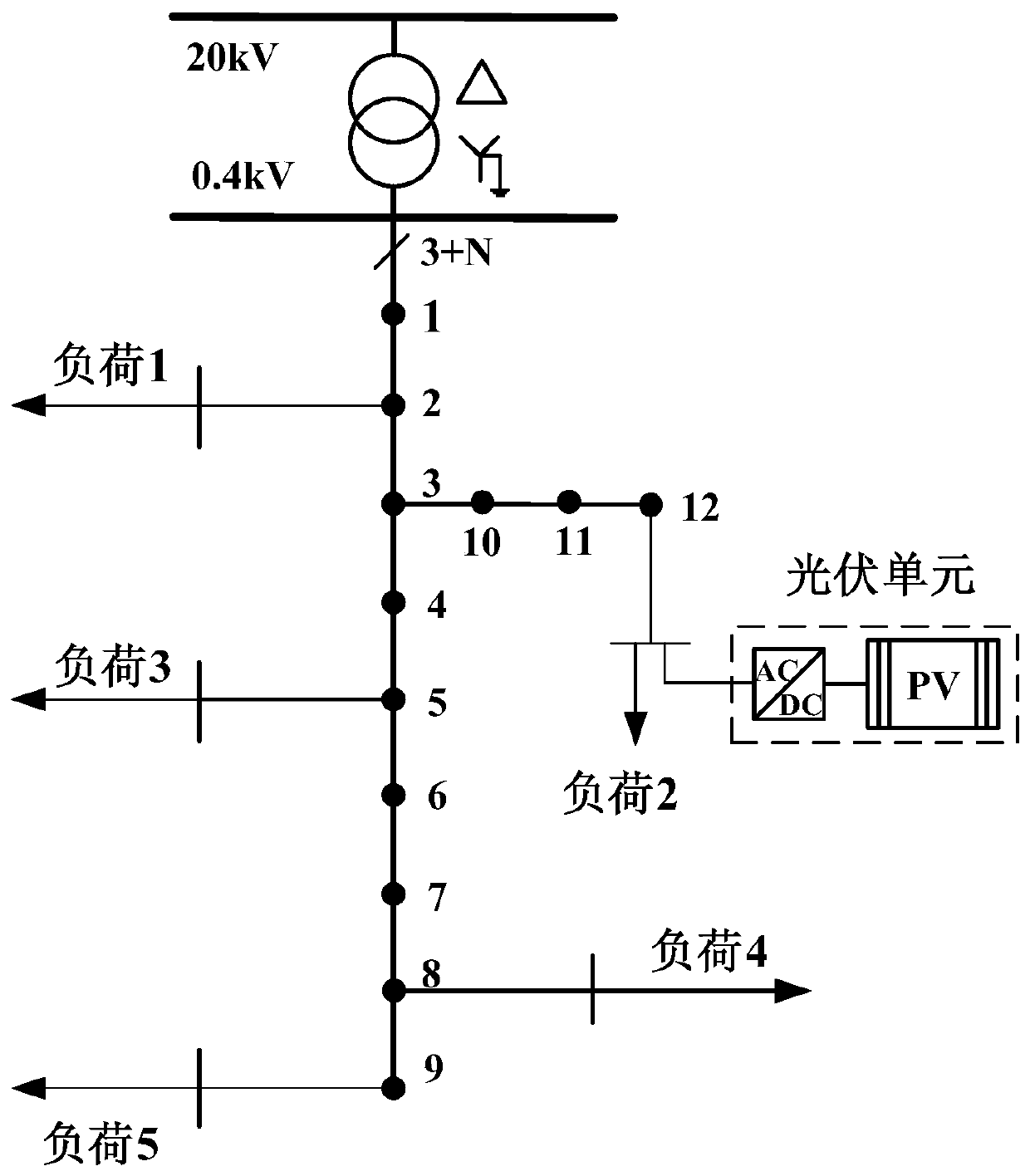

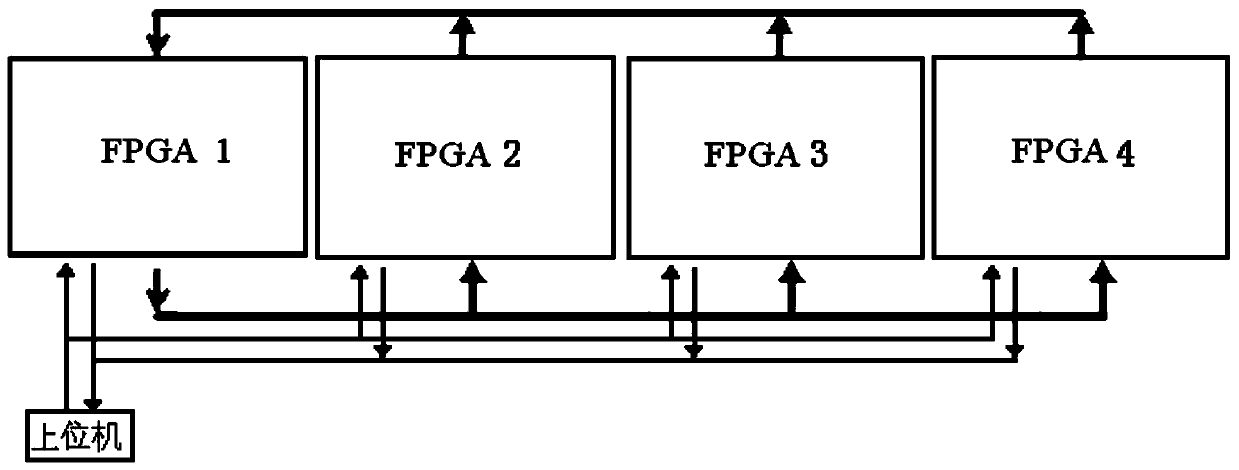

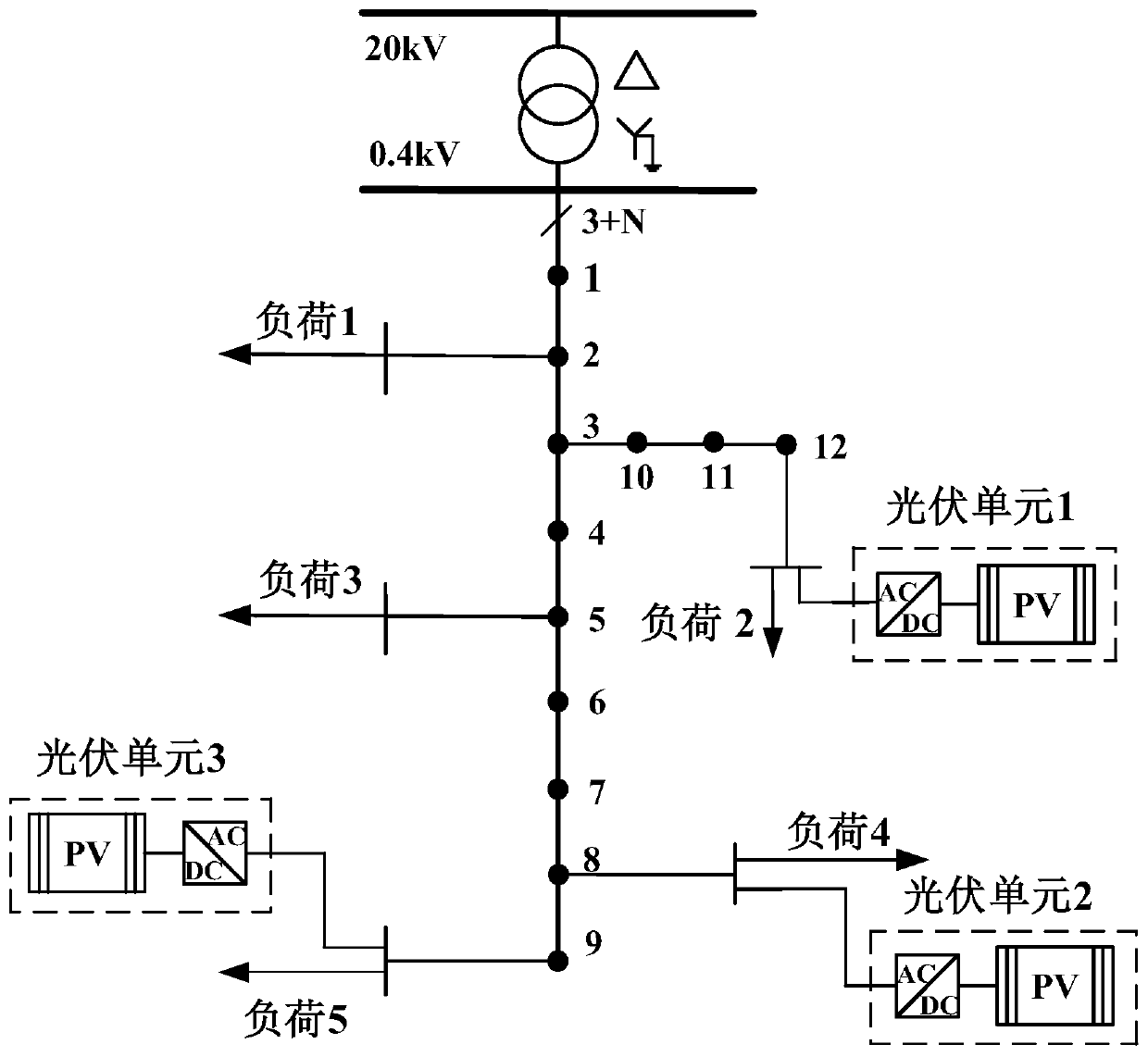

Design method of multi-rate interface for real-time simulator of active distribution network based on fpga

Owner:TIANJIN UNIV

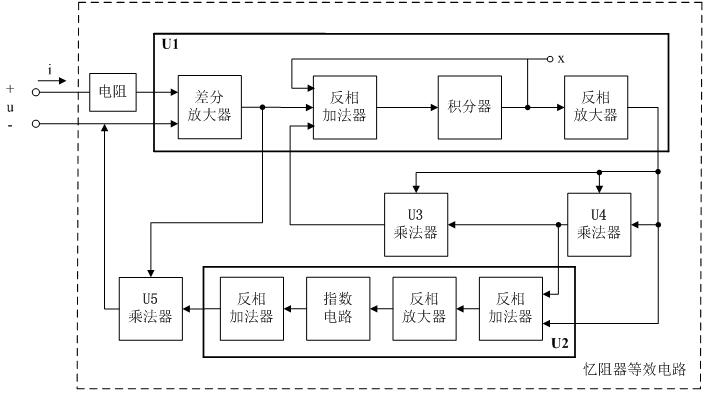

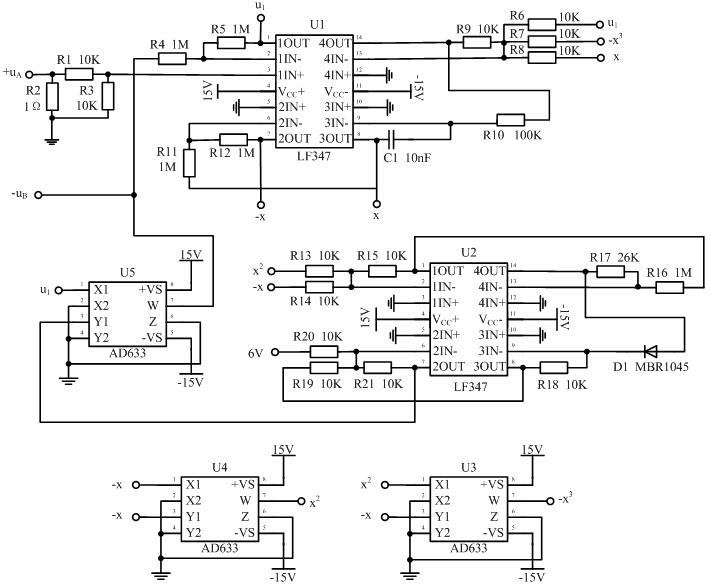

An Exponential Local Active Memristor Simulator

ActiveCN108718190BImplement multiplicationNetwork simulating reactancesBinary multiplierMathematical model

The invention discloses an exponential local active memristor emulator. The present invention designs a partial active memristor emulator circuit according to a mathematical model, and the emulator circuit includes an integrated operational amplifier U1, an integrated operational amplifier U2, a multiplier U3, a multiplier U4, and a multiplier U5, and the integrated operational amplifier U1 is used to realize differential Amplification operation, inverting addition operation, integral operation and inverting amplification operation; integrated operational amplifier U2 is used to realize inverting addition operation, inverting amplification operation and exponential operation; multipliers U3, U4, U5 are used to realize signal multiplication . Under the circumstances that the actual memristor device cannot be obtained at present and in the future, the present invention can replace the actual memristor to realize the circuit design, experiment and application related to the memristor, and has important practical significance for the characteristics and application research of the memristor .

Owner:HANGZHOU DIANZI UNIV

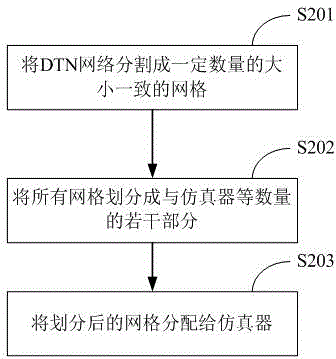

TMS32C6748 program burning method based on serial port high reliability

InactiveCN112346746AQuick to useSave the steps of frequent disassemblyBootstrappingSoftware deploymentSimulTrainDependability

The invention relates to a TMS32C6748 program burning method based on serial port high reliability. The TMS32C6748 program burning method is technically characterized by comprising the steps: planning18 sectors of Flash planned; generating a user bootstrap program; and pre-burning a user bootstrap program UBL at the planned Flash storage address; when the user bootstrap program UBL is started, judging a burning mark of the SA18 sector pair; if the burning mark is the burning mark, carrying out burning, and otherwise, loading a working program. The functions of achieving communication and completing FLASH writing by rapidly using a debugging interface of the system in real time without disassembling or assembling a simulator are achieved. Compared with direct programming by using an emulator, the method has the advantages that the step of frequent disassembly is omitted; and meanwhile, programming inquiry is actively sent to each serial port address when a program is started, and the programming inquiry can be directly used in each project without debugging different modification codes of the serial ports for each project, so that the universality and the code security are improved.

Owner:TIANJIN NAVIGATION INSTR RES INST

Distributed simulation system and method supporting large-scale complicated delay tolerant network (DTN)

InactiveCN102752173BImprove simulation speedEasy to addData switching networksController (computing)Network emulation

The invention relates to a distributed simulation system and simulation method supporting large-scale and complex DTN networks. Existing DTN network emulation tools can only run on a single machine, with limited computing power, small emulation ability, and small scale of emulation nodes that can be supported. The present invention builds a main controller and several emulators in the same local area network; divides the DTN network into grids, and assigns jurisdiction areas to each emulator; the main controller processes simulation events by advancing the simulation clock, Manages simulation and state synchronization for individual simulators. The present invention distributes the huge calculation requirements during DTN network simulation to different simulators, and the simulation speed is significantly improved; the basic network topology structure of one main controller and multiple simulators is adopted, and the scalability is strong; there are few requirements for the DTN network simulation scheme , the present invention can be used to realize distributed simulation only if the simulation scheme supports the linear division of the simulation network, and has strong versatility.

Owner:XIDIAN UNIV

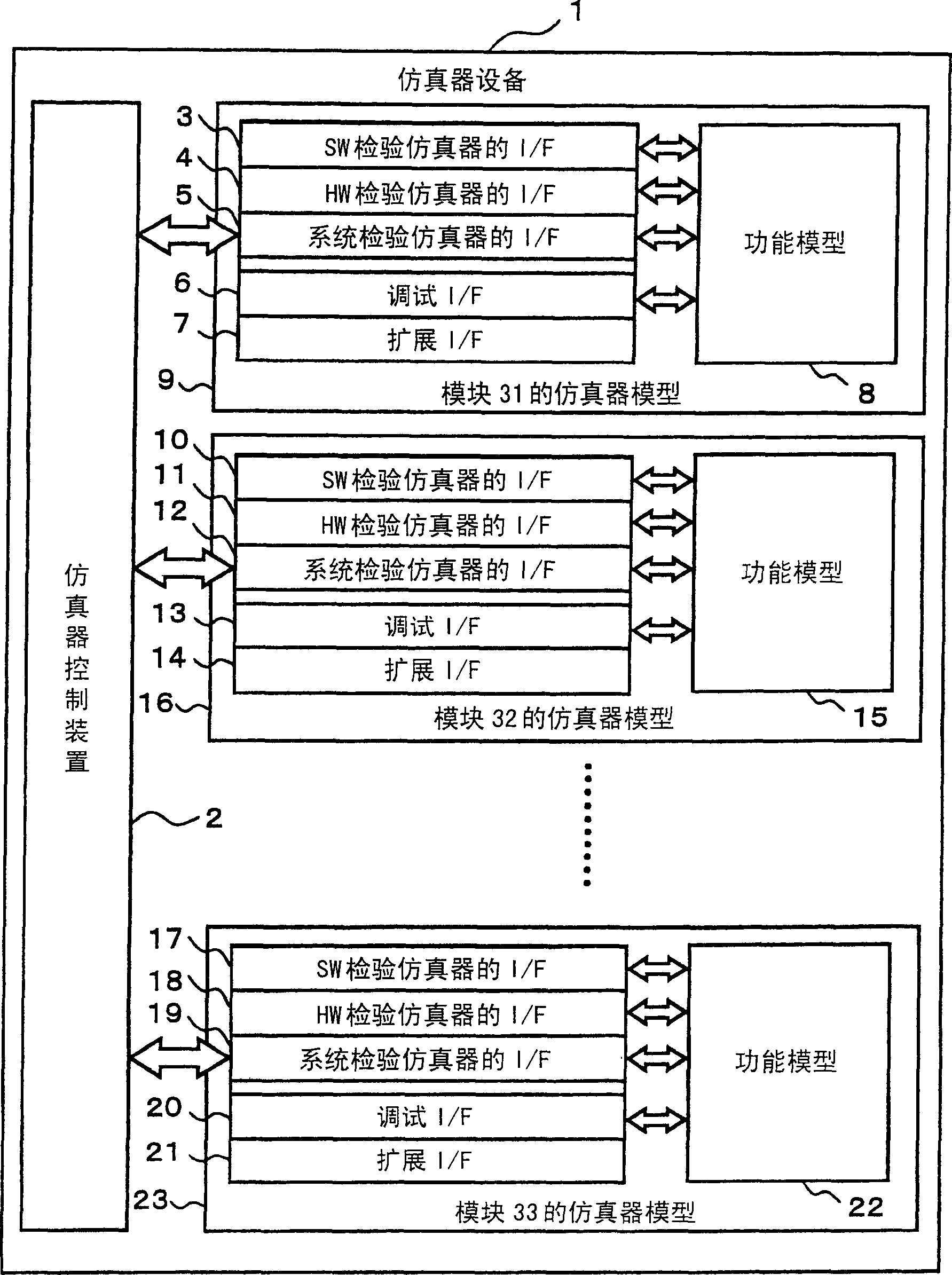

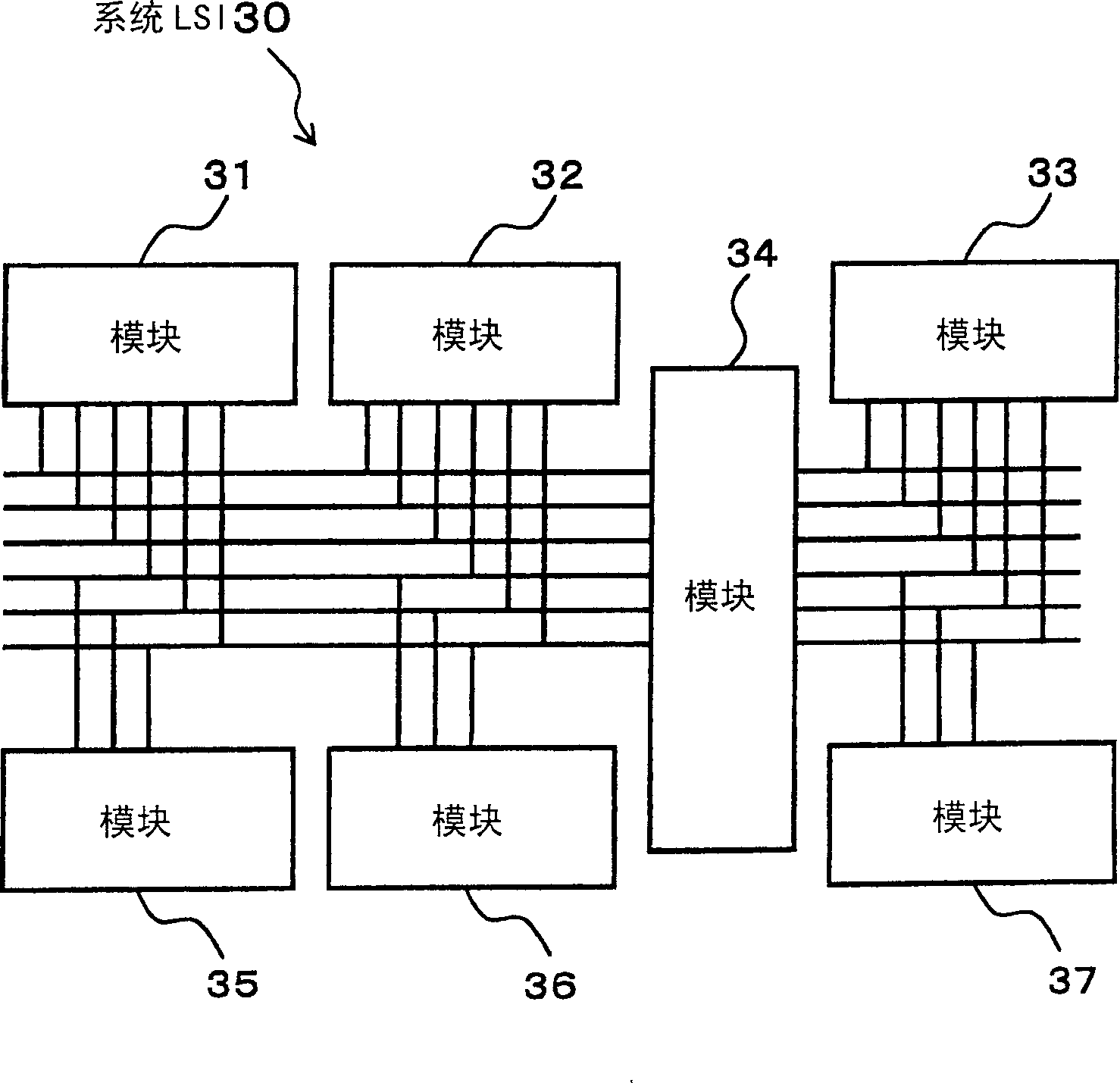

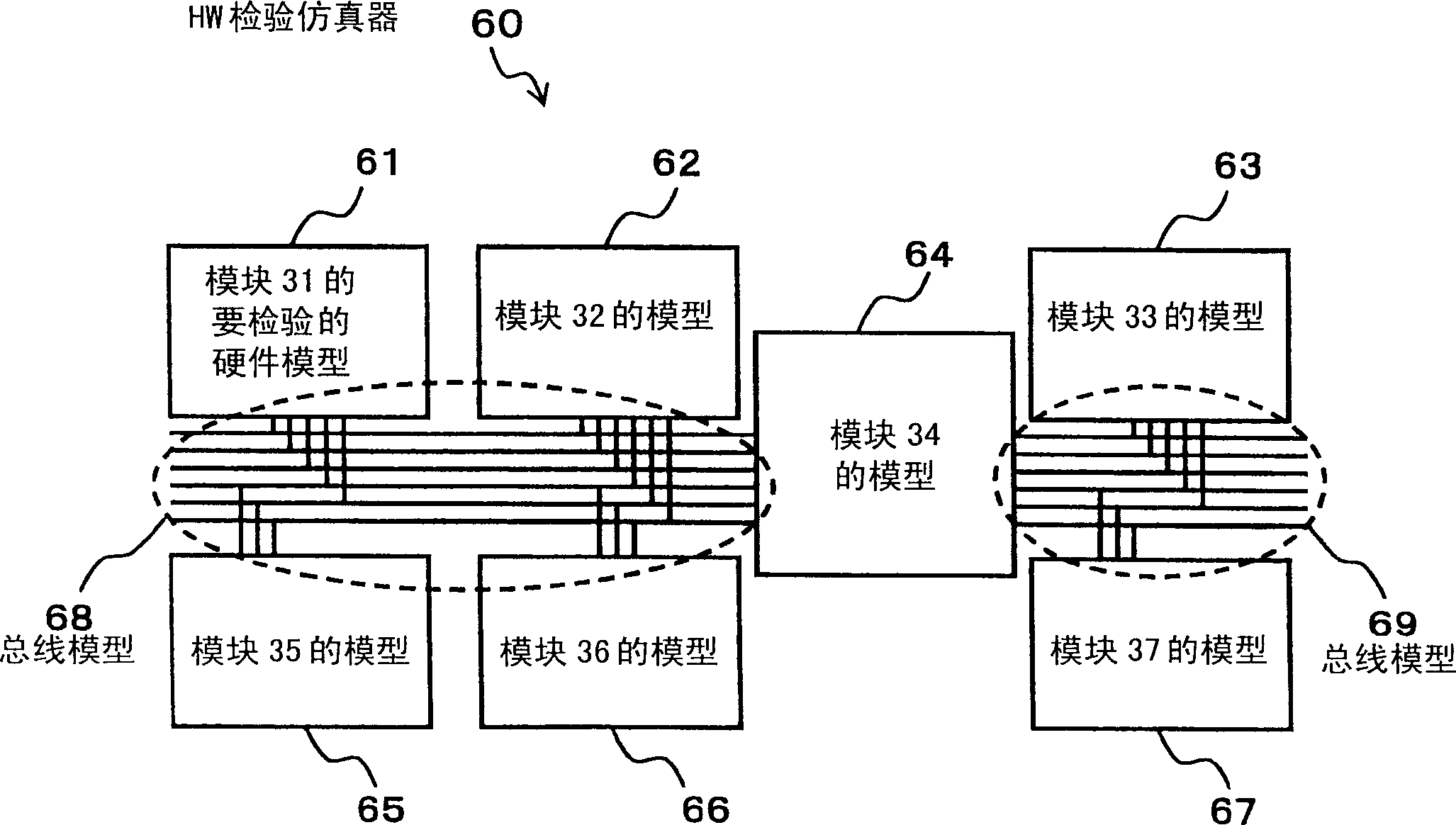

Emulator equipment and correlation technique

InactiveCN1278237CEfficient designAnalogue computers for electric apparatusSoftware testing/debuggingSimulTrainSimulation

A simulator apparatus comprises a simulator model including a functional model for CPU constituting a system to be simulated and a simulator model including a functional model for hardware to be connected to buses linked to the CPU. The respective simulator models include plural types of interfaces. The plural types of the interfaces enable plural types of simulators for different uses to access the functional models. The simulator apparatus further comprises a simulator controlling device for selecting any of the plural types of the interfaces and accessing the respective functional models via the selected interfaces.

Owner:PANASONIC CORP

A multi-simulator co-simulation method and system

ActiveCN113128073BOvercoming the "clock skew" problemEffective decouplingData processing applicationsDesign optimisation/simulationAlgorithmSimulTrain

Owner:清鸾科技(成都)有限公司

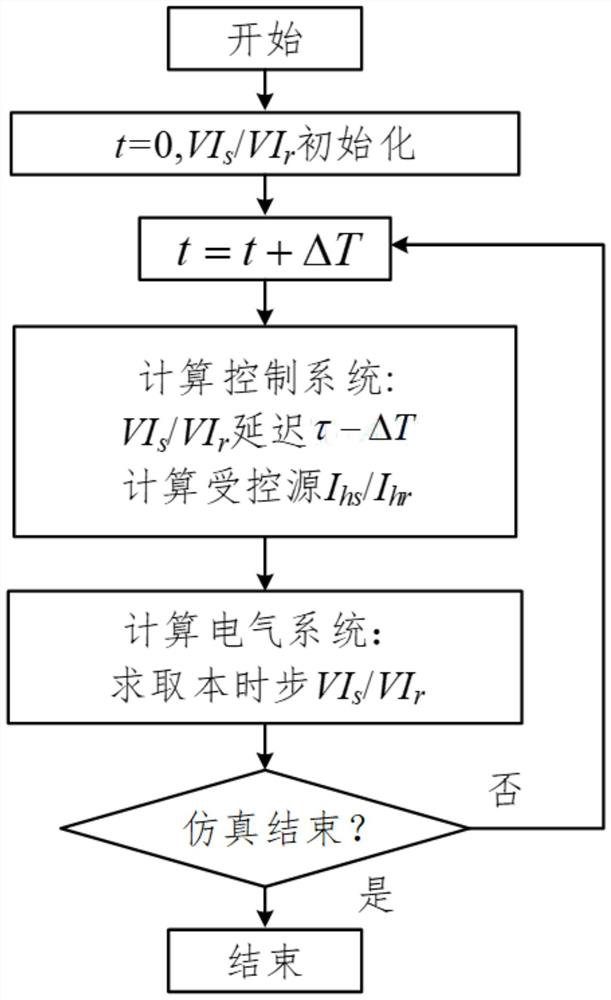

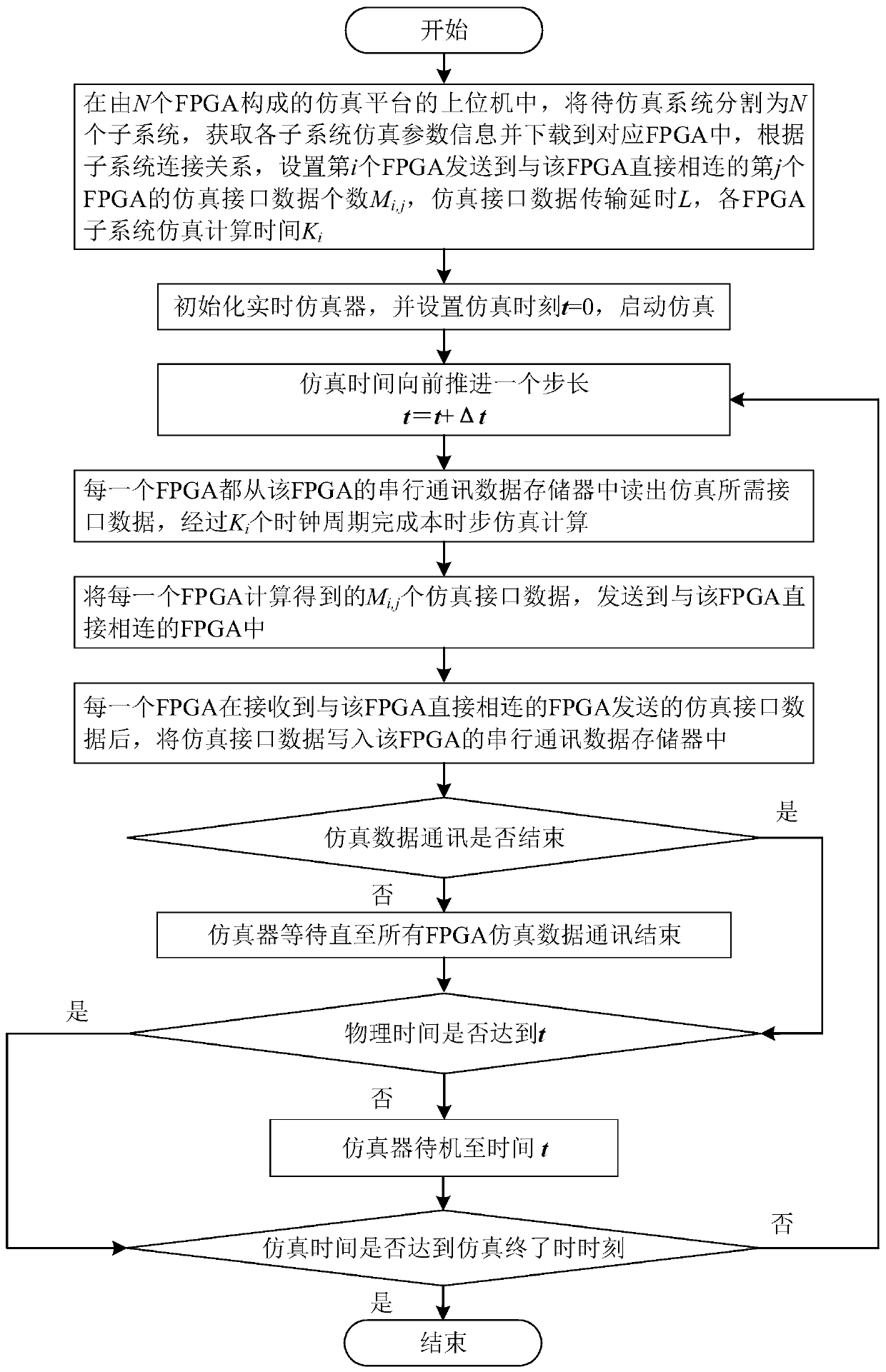

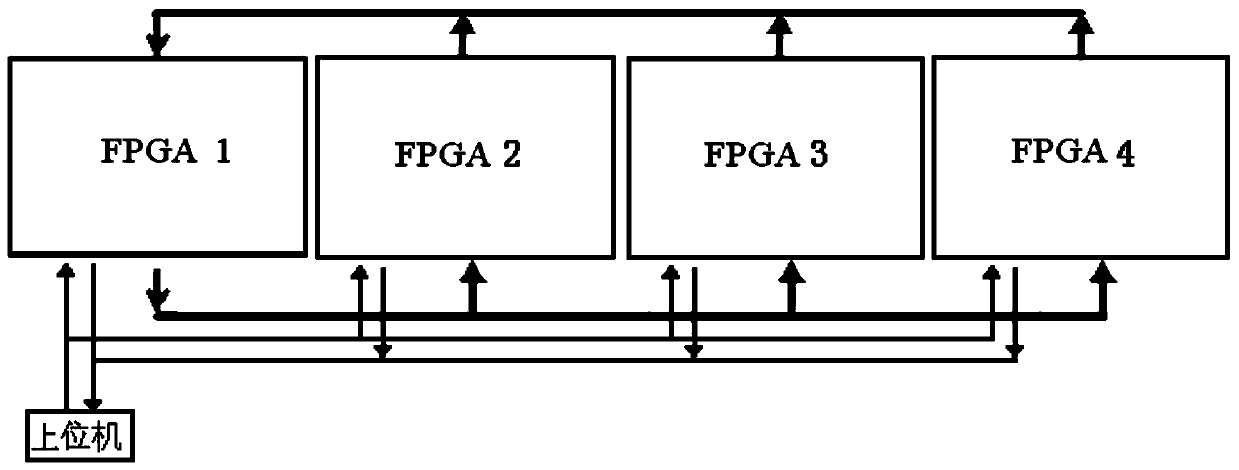

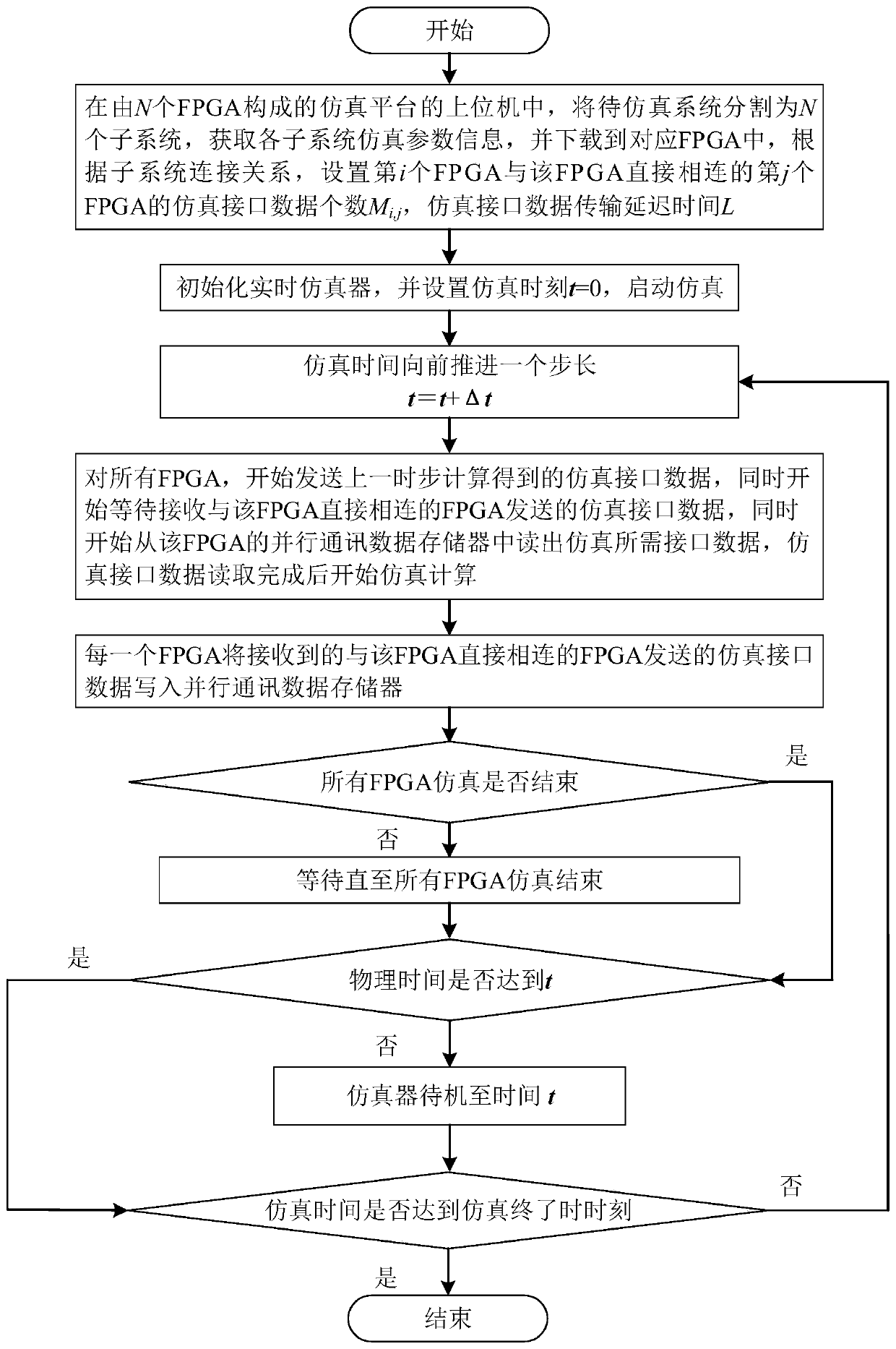

Serial communication method of active distribution network real-time simulator based on multi-fpga

InactiveCN107122562BGuaranteed Simulation AccuracyDesign optimisation/simulationSpecial data processing applicationsReal-time simulationSimulTrain

The invention discloses a serial communication method for the real-time simulator of an active distribution network on the basis of multi-FPGA (Field Programmable Gate Array). The method comprises the following steps that: 1) downloading each piece of subsystem information to a corresponding FPGA; 2) setting a simulation moment t=0, and starting simulation; 3) forward boosting simulation time for one step size, wherein t is equal to t+[Delta]t; 4) finishing simulation calculation by each FPGA; 5) sending simulation interface data obtained by calculation to each FPGA; 6) receiving and writing the simulation interface data to a data memory by each FPGA; 7) carrying out communication end checkout on a real-time simulator; 8) judging whether physical time achieves simulation time t or not, if the physical time achieves simulation time t, entering a next step, and otherwise, entering a next step after the real-time simulator stands after t; and 9) judging whether the simulation time t achieves a set final end moment or not, ending simulation if the simulation time t achieves the set final end moment, and otherwise, returning to the 3). By use of the serial communication method, on a premise that the simulation speed of the real-time simulator is met, simulation accuracy is guaranteed, and a foundation is laid for the real-time simulation of the large-scale active distribution network on the basis of the multi-FPGA.

Owner:TIANJIN UNIV +1

Parallel communication method of active distribution network real-time simulator based on multi-fpga

InactiveCN107423476BImprove simulation speedDesign optimisation/simulationSpecial data processing applicationsReal-time simulationSimulTrain

The invention discloses a parallel communication method for an active power distribution network real-time simulator on the basis of a multi-FPGA (Field Programmable Gate Array). The method comprises the following steps that: 1) downloading each piece of subsystem information into a corresponding FPGA; 2) setting that a simulation moment t is equal to 0, and starting simulation; 3) forwards propelling simulation time for one step, wherein t is equal to t+[Delta]t; 4) beginning to carry out interaction simulation on interface data by each FPGA, and meanwhile, beginning to finish simulation calculation; 5) writing the received simulation interface data into a data memory by each FGPA; 6) carrying out simulation finishing checking on the real-time simulator; 7) judging whether physical time achieves simulation time t or not, if the physical time achieves the simulation time t, entering next step, and otherwise, entering the next step after the real-time simulator is standby to t; and 8) judging whether the simulation time t achieves a set simulation finishing moment or not, if the simulation time t achieves the set simulation finishing moment, stopping simulation, and otherwise, returning to the 3). By use of the parallel communication method adopted by the invention, the simulation speed of the parallel communication method for the active power distribution network real-time simulator on the basis of the multi-FPGA is improved, and a foundation is laid for realizing the real-time simulation of the large-scale active power distribution network on the basis of the multi-FPGA.

Owner:TIANJIN UNIV +2

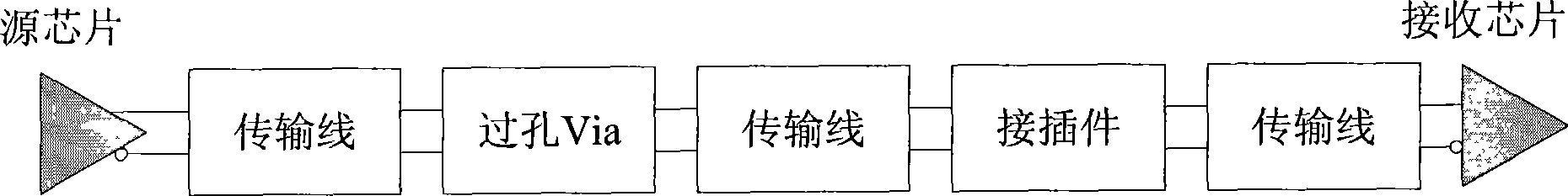

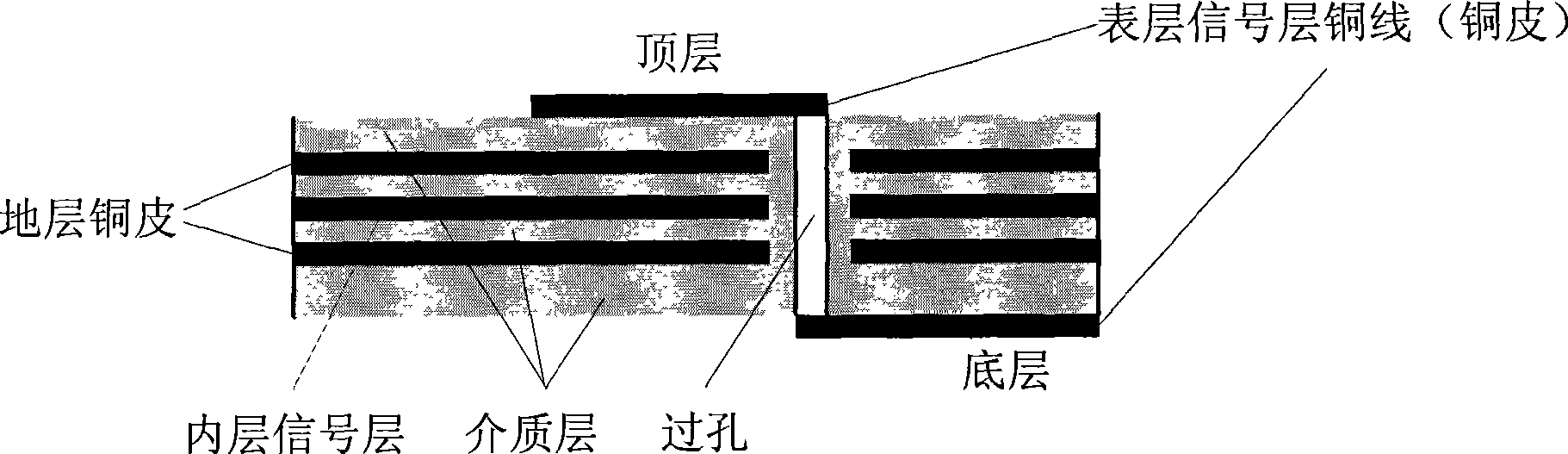

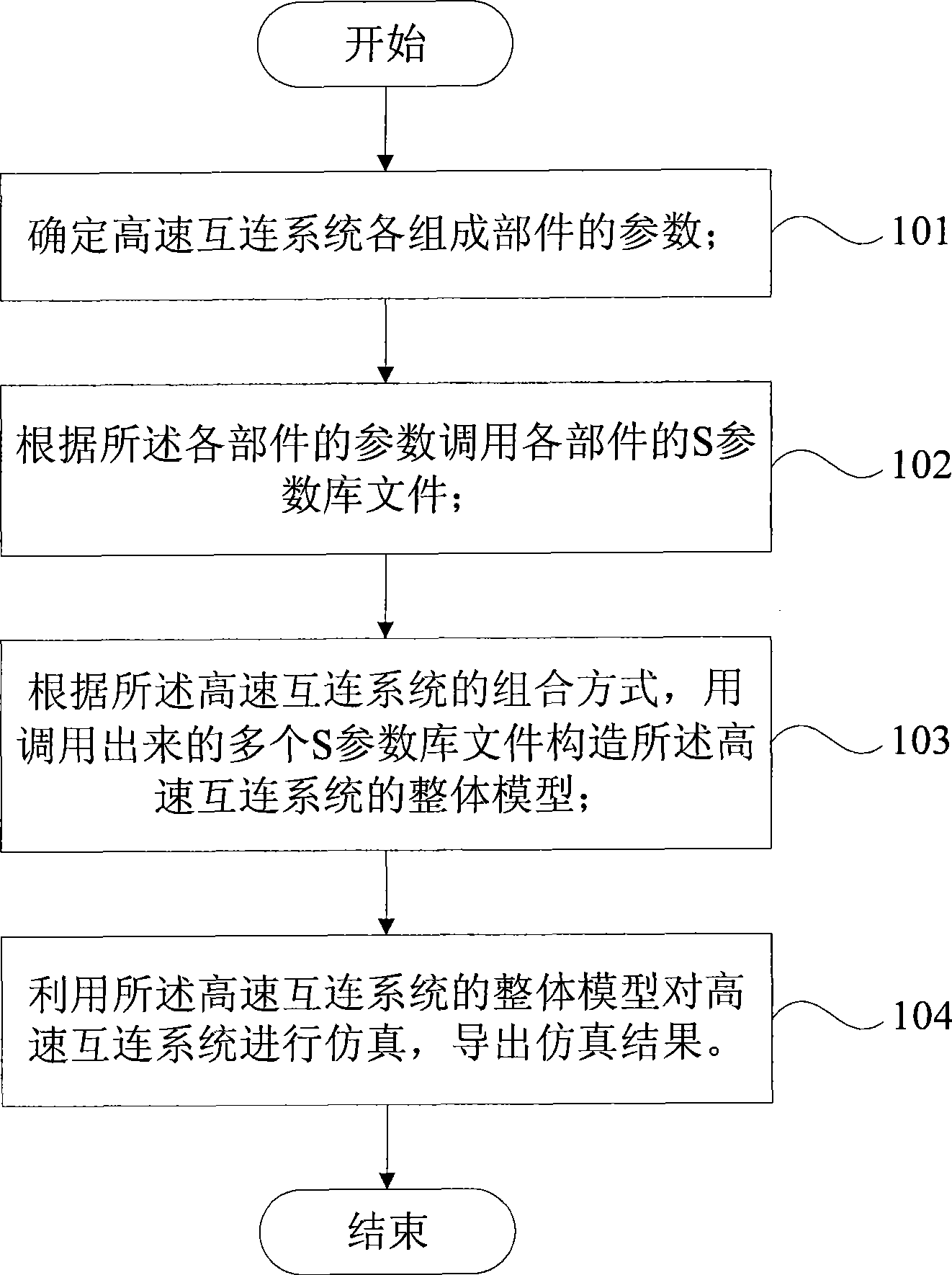

Emulation design method and system for high speed interconnection system

The invention provides an emulation design method for a high-speed inter-connected system and the high-speed inter-connected system. The emulation design method comprises the following steps: determining parameters of composition components in the high-speed inter-connected system; calling S parameter base documents for the composition components according to the parameters of the composition components; building an integral model for the high-speed inter-connected system according to the topology combination mode of the high-speed inter-connected system and by using the called S parameter base documents; and emulating the high-speed inter-connected system by using the integral model of the high-speed inter-connected system and inducing emulation result. The emulation design method for the high-speed inter-connected system and the high-speed inter-connected system adopt a separate modeling mode according to the topology structure of a high-speed tandem system, and flexibly adopt proper emulators to emulatically calculate the components of the high-speed tandem system, so as to overcome the disadvantage of either long calculating time or low accuracy, which is caused by the fact that the same emulators have to be adopted in integral modeling in the prior high-speed tandem system.

Owner:RUIJIE NETWORKS CO LTD

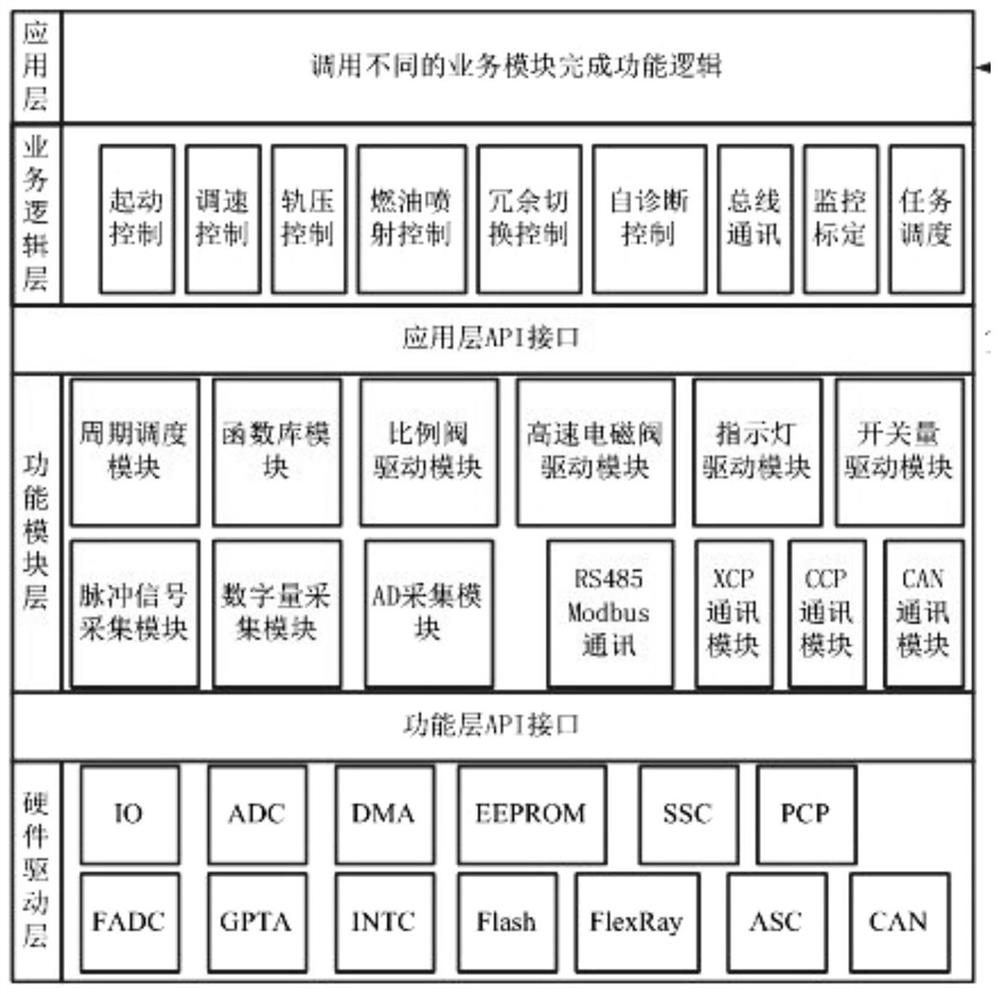

Model-based TC1797 diesel engine control algorithm development tool

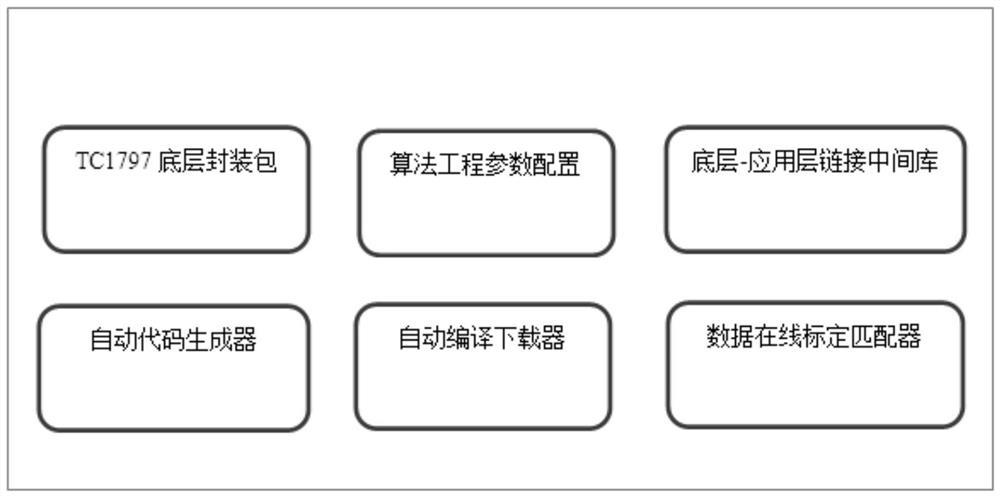

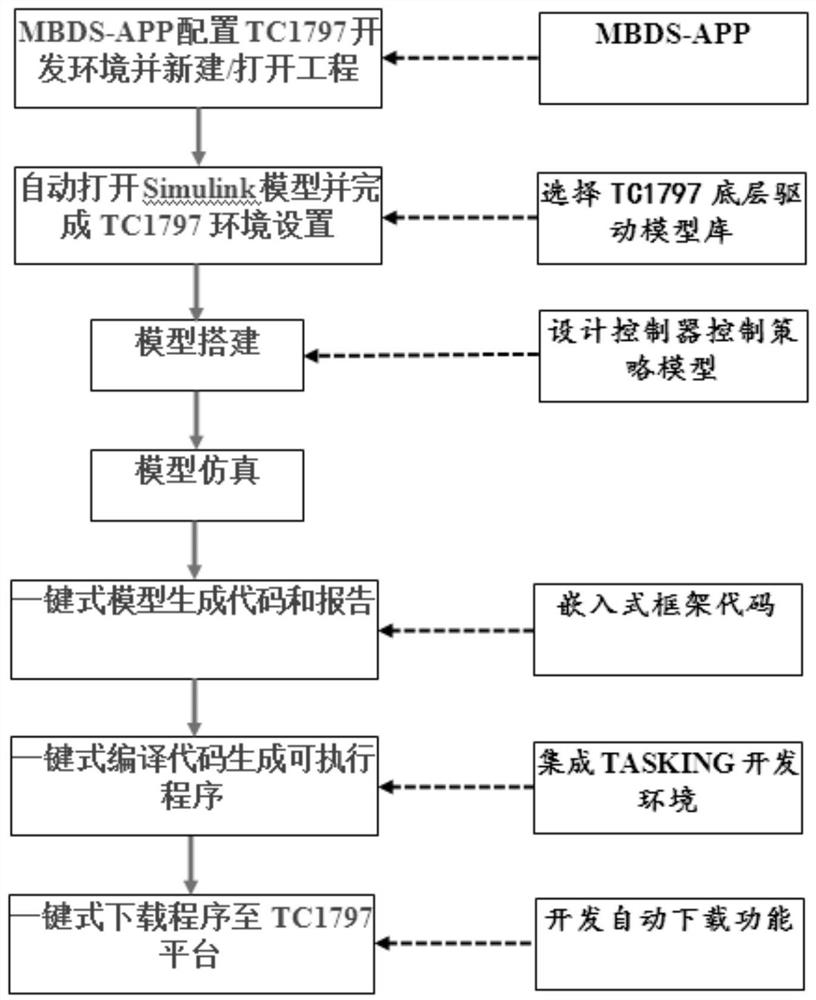

PendingCN113742232ARapid modelingSoftware testing/debuggingCode compilationDiesel engineOperating system

The invention provides a model-based TC1797 diesel engine control algorithm development tool. The invention comprises the following steps of: customizing a TC1797 target platform Simulink model library, seamlessly installing the TC1797 target platform Simulink model library in a Simulink environment, and configuring relevant parameters through a graphical interface; customizing an embedded frame code and an embedded code generation template of the TC1797 target platform; automatically integrating an integrated development environment of TASKING and a one-button model to C code generation, automatically compiling an executable program and downloading to the target platform through an emulator, achieving rapid design, test and verification of an algorithm. According to the method, the Simulink module library is driven through the customized graphical target platform interface to control the algorithm model to quickly generate the executable code of the target platform, and convenient configuration of the development environment of the target platform and unified management of engineering projects can be realized.

Owner:CHONGQING HONGJIANG MACHINERY

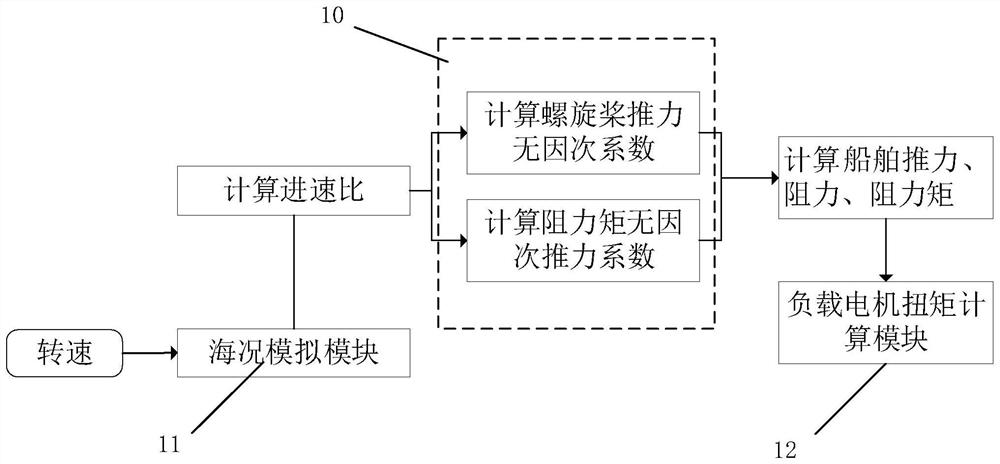

Ship propeller load simulation device and control method based on opc communication technology

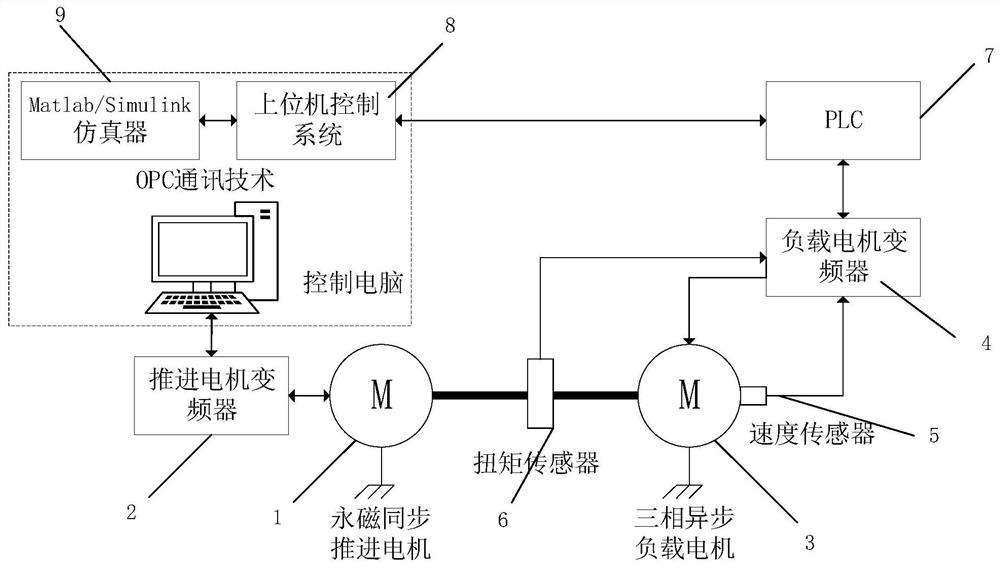

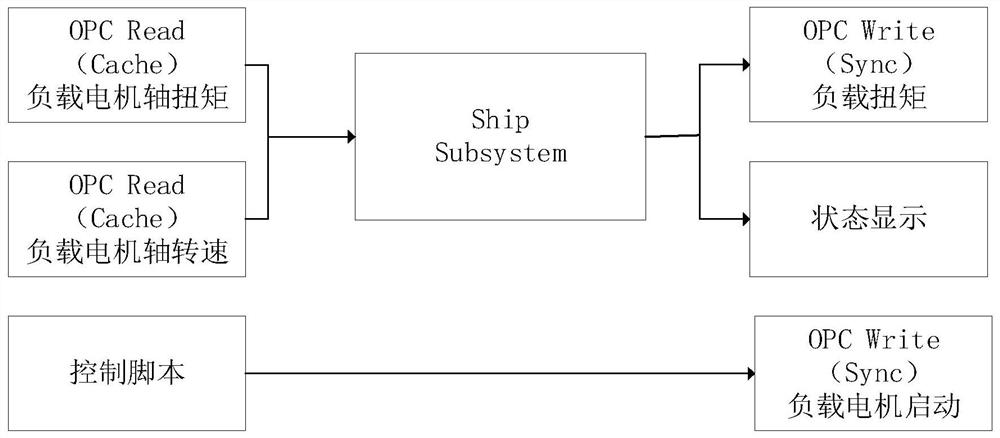

InactiveCN109946604BReduce consumptionDynamo-electric machine testingComputer control systemSimulTrain

The invention discloses a simulation device and a control method for the load characteristic of a ship propeller. In the technical field of motor load simulation, the device includes a propulsion motor, a propulsion motor frequency converter, a load motor, a load motor frequency converter, a speed sensor, a torque sensor, a PLC Programmable controller, upper computer control system and MATLAB / Simulink simulator; upper computer control system includes propeller simulation module, sea state simulation module connected with propeller simulation module and load motor torque calculation module connected with propeller simulation module. The present invention utilizes OPC communication technology to upload the operating state of the propulsion motor to the MATLAB / Simulink simulator in real time, and combines the parameters of the ship, real-time sea conditions and other influencing factors of the ship to simulate the torque of the load motor to make its torque characteristics It is very close to the load condition of the real ship.

Owner:DALIAN MARITIME UNIVERSITY