A time and timing calibration method and device based on processor pipeline analysis

A processor and pipeline technology, applied in the computer field, can solve the problems of time deviation and large timing error, and achieve the effect of improving accuracy and reducing timing error.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

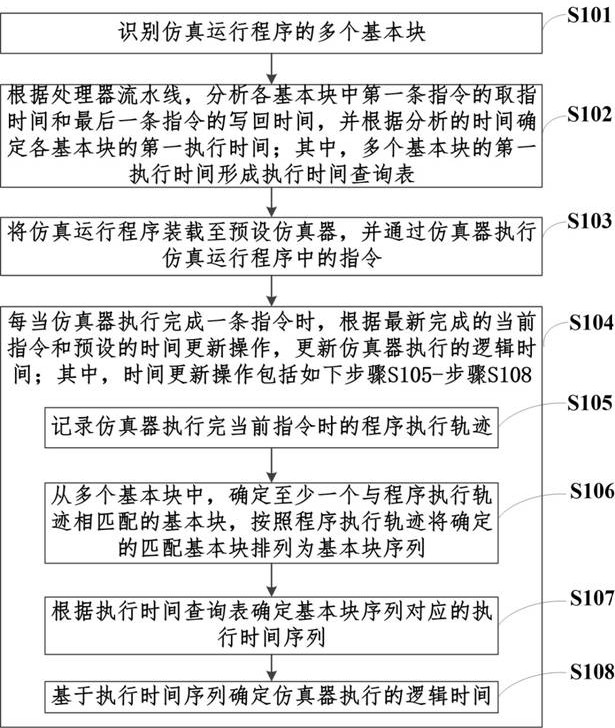

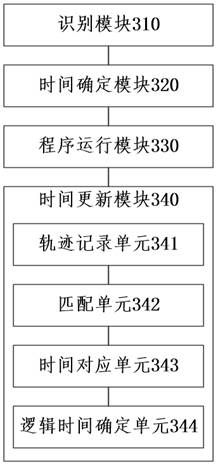

[0034] In order to more clearly understand the above objects, features and advantages of the present disclosure, the solutions of the present disclosure will be further described below. It should be noted that, in the case of no conflict, the embodiments of the present disclosure and the features in the embodiments can be combined with each other.

[0035] In the following description, many specific details are set forth in order to fully understand the present disclosure, but the present disclosure can also be implemented in other ways than described here; obviously, the embodiments in the description are only some of the embodiments of the present disclosure, and Not all examples.

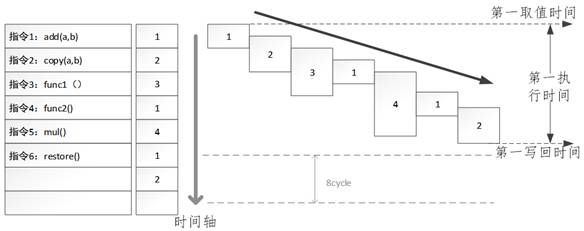

[0036]In the process of design and development of embedded system based on simulation virtual environment, how to ensure the consistency of the time and timing relationship of the simulation system with the actual system has become the key technology of full digital simulation verification. The ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More