Display substrate, display device and driving method of display device

A technology for display substrates and display devices, applied in static indicators, instruments, semiconductor devices, etc., can solve the problems of increasing the number of gate drive chips, reducing the aperture ratio, and disadvantageous narrow borders, etc., to improve display quality and improve aperture ratio. , the effect of improving the pixel charging rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

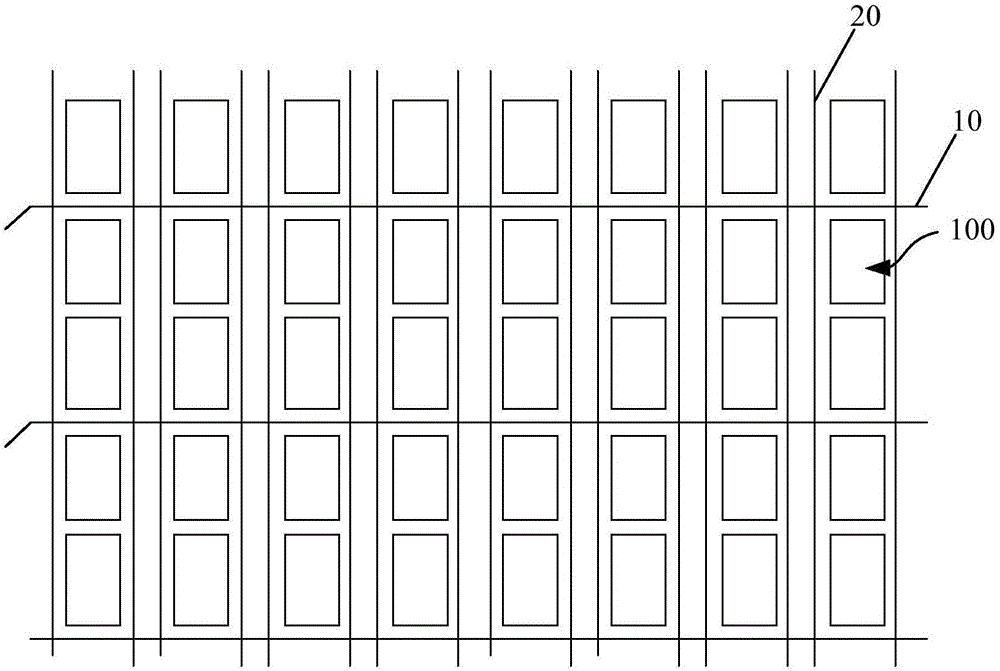

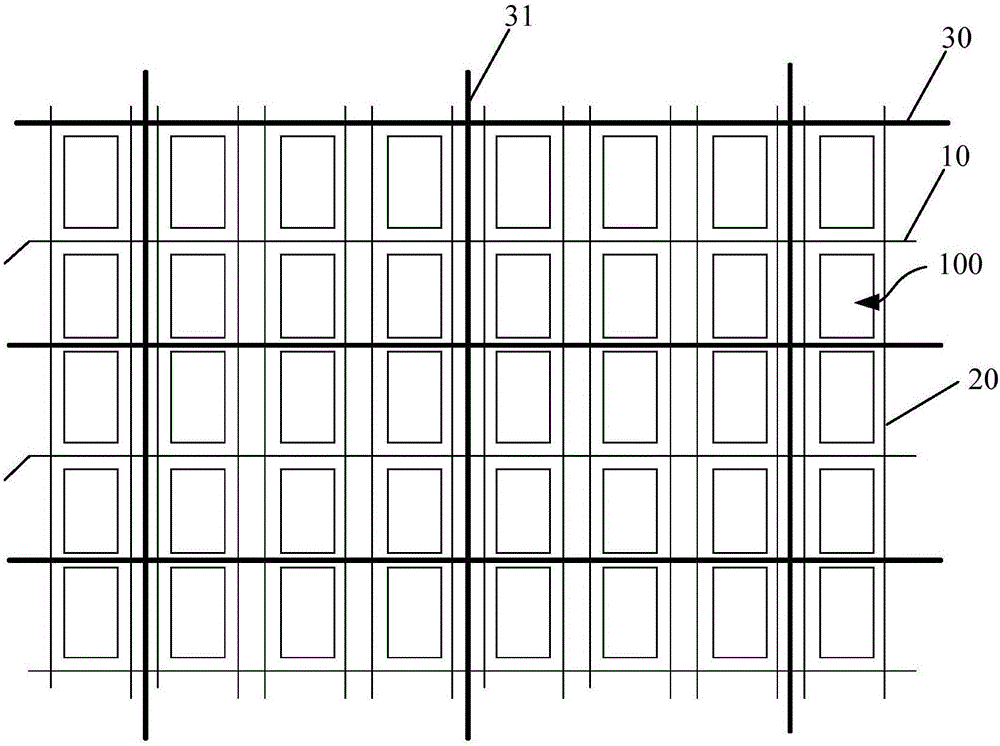

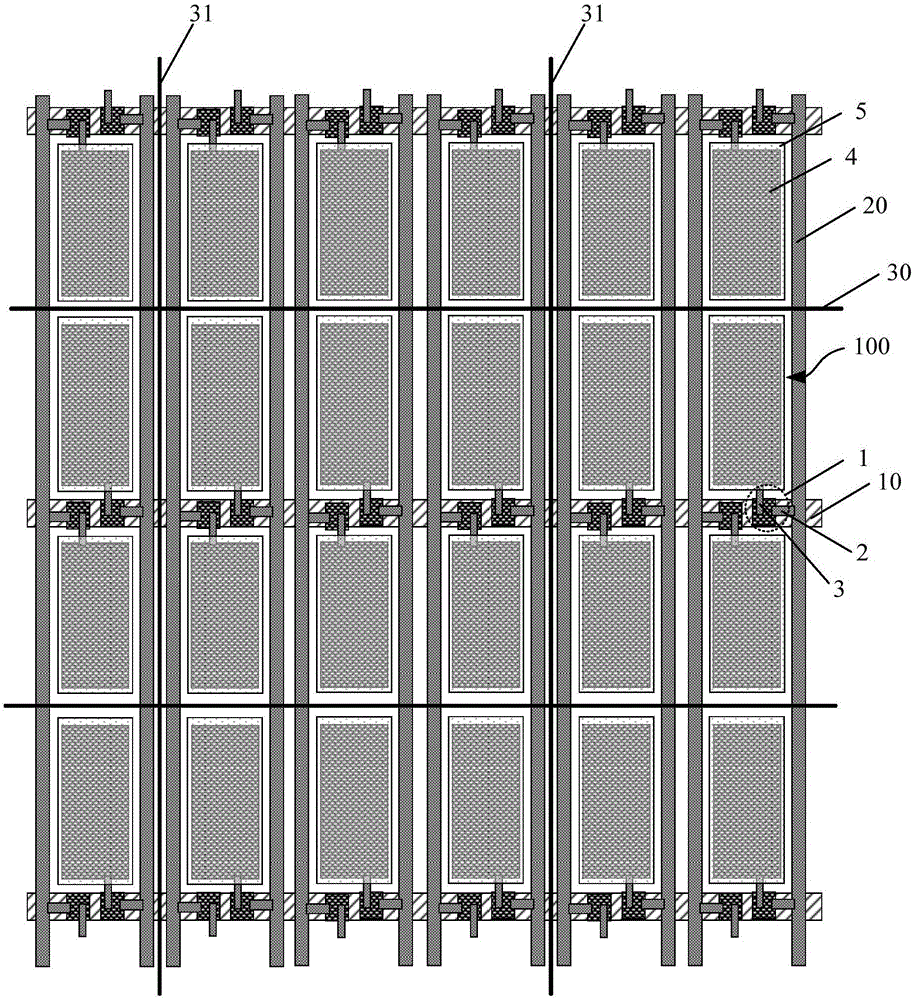

[0021] to combine figure 1 and image 3 As shown, in this embodiment, a display substrate is provided, including a plurality of gate lines 10 and a plurality of data lines 20 , and the gate lines 10 and data lines 20 are distributed across and define a plurality of sub-pixel regions 100 . There are two rows of sub-pixel regions 100 between two adjacent gate lines 10 , and two data lines 20 between two adjacent columns of sub-pixel regions 100 . Each sub-pixel region 100 includes a thin film transistor 1 , the gate electrode of the thin film transistor 1 is integrally formed with the gate line 10 , the source electrode 2 is connected to the data line 20 , and the corresponding thin film transistor 1 is turned on or off through the gate line 10 .

[0022] The thin film transistors 1 of two adjacent rows of sub-pixel regions 100 located on both sides of a gate line 10 are connected to the gate line 10, and the thin film transistors 1 of adjacent two rows of sub-pixel regions loc...

Embodiment 2

[0049] This embodiment provides a display device and a driving method thereof. The display device adopts the display substrate in the first embodiment, and since the number of gate lines is halved, the aperture ratio is increased. At the same time, halving the number of gate lines reduces the number of gate drive chips or gate drive circuits, reduces costs, and facilitates the realization of narrow borders. In addition, since the thin film transistors in one row of sub-pixel regions can open the charging time of two rows of sub-pixels, sufficient charging time is provided, thereby increasing the pixel charging rate and improving display quality.

[0050] Wherein, the display device may be a liquid crystal display device, an organic electroluminescent display device, or the like.

[0051] The driving method of the above display device includes:

[0052] The thin film transistors in two adjacent rows of sub-pixel regions located on both sides of the gate line are simultaneousl...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More